Build your Own Z80 Computer , by Steve Ciarca, full scanned book

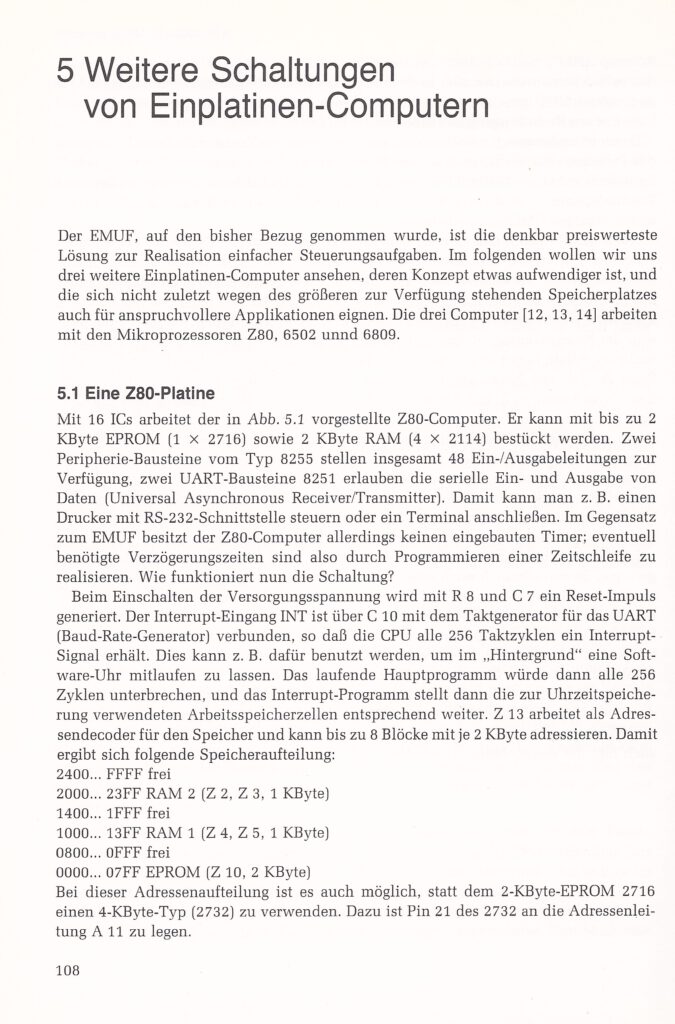

Big Board II

A Z80 computer, able to run CP/M.

In this archive the scans of articles in Elektuur Computing 2.

About small SBC systems

Build your Own Z80 Computer , by Steve Ciarca, full scanned book

A Z80 computer, able to run CP/M.

In this archive the scans of articles in Elektuur Computing 2.

The original Dutch and later international electronics magazine in thee arly microprocessor years did not only pay attention to the 6502, also SC/MP and Z80 were used in designs.

On this pages some of their Z80 articles.

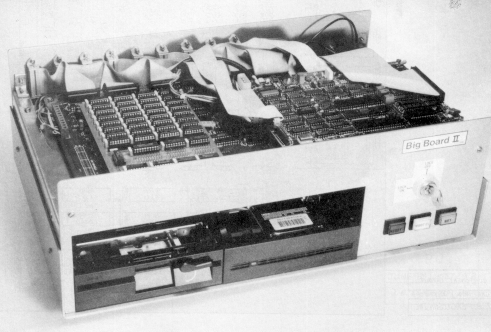

While building the Retro Chip Tester, designed by Stephan Slabihoud, and documented on his 8bit-museum website, I noticed Stephan also designed CPU NOP testers and made designs as gerbers and BOM available. With the PCB of the Retro Chip tester I laso bought the PCB’s for 6502 and Z80 NOP tester from him. NOP testers are very simple test devices and in no way a real CPU stress test. Enough to discover if the IC is not a fake or severely damaged and not fit to be tested in a real system.

The idea of NOP testers is not new, for example Lee Davison documented his NOP tester for the 6502 here.

Stephan made the NOP testers standalone devices. Besides the socket for the CPU to test a clock signal is generated with a 555, a push-button does the reset, the minimal of control lines is connected to ground or puleld high, power is supplied with a USB connector.

The clock oscillator has a very low frequency, so you can see the address lines change by observing LEDs connected. This means the NMOS 6502 and Z80 are operated way below their minimal frequency, e.g. 100KHz for a 6502. The CMOS versions are static and can be driven with this low frequency.

In my experience with these testers is that the NMOS versions of 6502 and Z80 do work with this tester though, but I have seen good 6502’s start off well but after a minute crashed with all LEDs flashing in the tester. So not a definite test for NMOS! An interesting modification would be to have a higher clock frequency (1MHZ at least) and inspect all the address lines with an oscillosope.

Read the original articles and download Gerbers and BOM’s from the 8bit-museum.

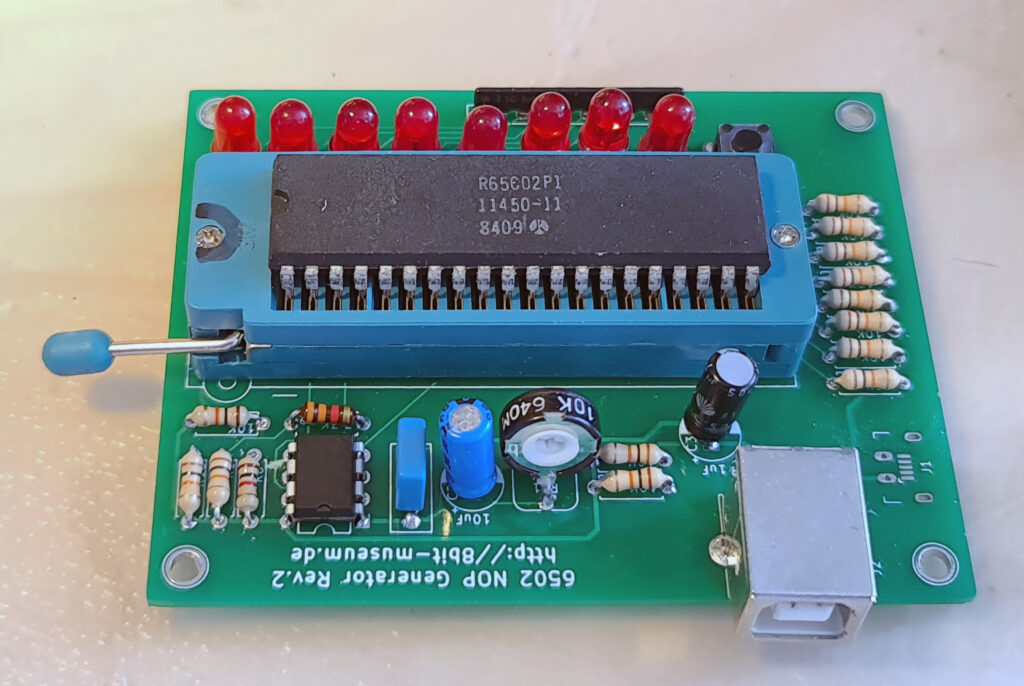

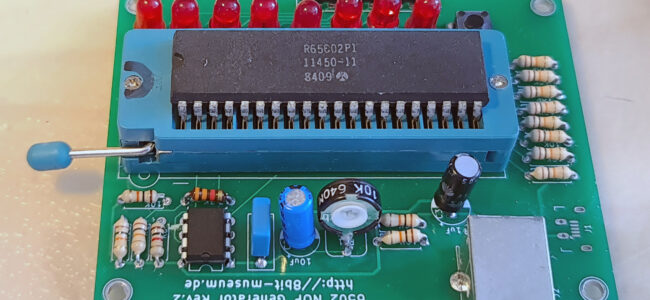

6502 NOP Generator

Used in a 6502 NOP generator , a 6502 CPU only executes NOP commands (No Operation). The low eight address lines can be observed with the aid of LEDs. If the CPU executes the NOPs, the addresses should be continuously incremented. This does not allow a complete test of the CPU, but at least a quick-n-dirty check.

The 6502 NOP generator in action:

The 6502 NOP generator supplies the opcode 0xEA, which corresponds to a NOP for the 6502. After a reset, the 6502 NOP generator starts to count from address 0xEAEA (after a reset the CPU reads the real start address from addresses 0xFFFC-0xFFFD and since this always reads 0xEA, this is 0xEAEA). The LEDs should start counting at 11101010.

It is very nice to see how after the reset the addresses 0xFFFC and 0xFFFD are accessed first (before that a little initialization of the CPU), in order to then count from 0xEAEA (LEDs: FC, FD, E9, E7, EA, E9, FD, [FF] FC, [FF] FD, [EA] EA, EB, EC, ED, EE, EF, F0, F1 .., the upper 8 bits added in square brackets for understanding).

Changes for WDC65C02

While the 6502 NOP Generator has been designed for the 65C02 and 6502 pinout, it can be modified to work with the still available WDC65C02 variant. Differences between the variants are minor but essential:

VPB Vector-Pull output Pin1 must be left open, on the 6502 and 65C02 this is the (second) Ground pin, On the PCB pin 1 is connected to ground, easy to cut track, see the photo below.

Pin 36 BE (Bus Enable) Connect a resistor 10K to VCC. Easy to add on the bottom of the PCB. pin 36 is NC (Not Connected) on 6502 and 65C02.

The latest gerbers on teh site of 8bit-museum have these modifications!

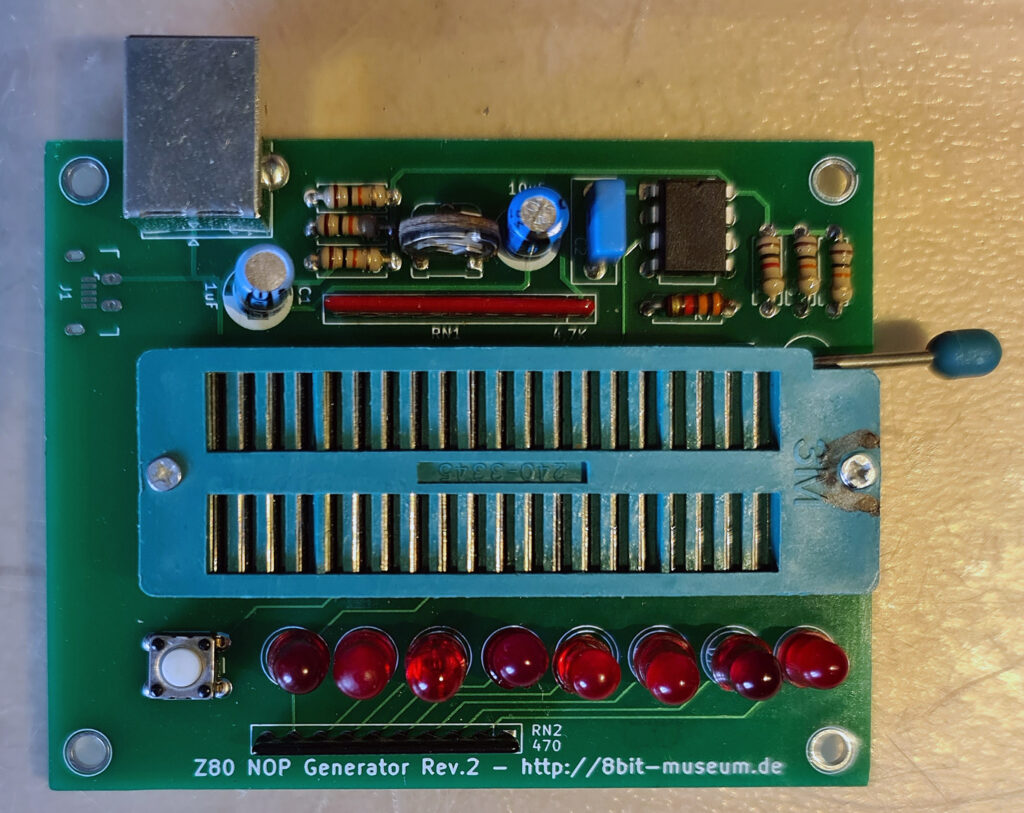

Z80 NOP tester

When used in a Z80 NOP generator , a Z80 CPU only executes NOP commands (No Operation). The low address lines can be observed with the aid of eight LEDs. If the CPU executes the NOPs, the addresses should be continuously incremented. This does not allow a complete test of the CPU, but at least a quick-n-dirty check.

The NOP generator presented here only works with Z80 CPUs. Since the CPU is clocked very slowly, far outside the specification, it is quite possible that an actually functional CPU does not work with the NOP generator. The way it works is very simple: The data lines are pulled to ground by pull-down resistors, so that the CPU reads a NOP (opcode 0x00) when the memory is read. After a reset, the CPU starts executing these commands from address 0.

Z80 Retrocomputer building kit (Budgetronics.eu)

A build of Grant Searle’s famous simple Z80 design

http://searle.x10host.com/z80/SimpleZ80_32K.html

Parts are as expected from Grant’s design, except the EPROM, which is a 27C04012JC. in a PLCC case. A bit overkill (512Mb for a 8K ROM!) but cheap I suspect.

The ROM contents are the Nascom Basic adapted by Grant for a serial terminal. A typical Microsoft Basic of the early microcomputer days.

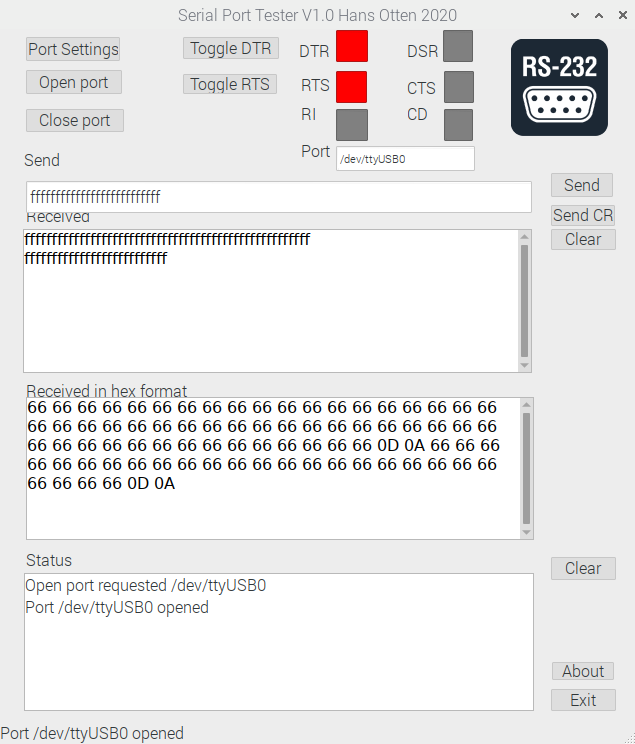

Connect a serial terminal, e.g. an USB TTL Serial cable to the PCB, start Tera term (Windows) or Minicom (linux), set the serial port to the COM/xTTYUSBxx port, speed 57600, no hardware handshake (or to hardware control connect if CTS to RTS connection available). If no hardware handshake, then you will have to adapt the delays after receiving character (1ms) and line (20ms) to prevent overruns on uploading Basic program text file. For me this worked out in Tera Term as shown in the next screenshot:

Without any storage facilities this computer is really only usable with a PC as terminal emulator to send files, as if the charaters in the file were typed in.

The same for saving, grab the ASCII output (the log facility in Tera Term for example).

Nice compact design, works perfect within its limitations.

A program, SerialTester, a guide and test results.

In 1984 I bought my first MSX, a Toshiba HX-10. A toy machine. Fun, but only suited for games. Z80, MSX-Basic, 64K, video (40×24 characters, graphics, color), audio cassette recorder for storage.

|

|

In 1986 the second machine, a Spectravideo SVI.738 Xpress entered my home. And that was not only fun, but a real computer: floppy drive, MSX-DOS, CP/M, 80 column screen. A real workhorse, with CP/M and Turbo Pascal! Mostly used with CP/M and a VT100 as console via the serial interface. Enhanced to MSX-2, two floppy drives, RGB output.

|

|

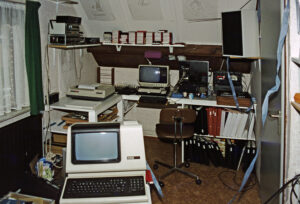

My interest in videoprocessing made me buy the quite expensive NMS8280 in 1992. Enhanced to MSX-2+ with memory mappers, slot expanders, SCSI hard disk interfaces, S-VHS video input/output. An impressive machine, but less a workhorse than I expected it to be. Video processing was very time consuming, I had two Panasonic S-VHS professional recorders, a video mixing tablet and the NM8280. It was not the success I hoped for, that had to wait for Adobe Premiere and full digital video editing with capturing analog video. A stream of IBM PC clones took the place of workhorse the years after and the MSX machines gathered dust.

|

|

Here I show scans and software for MSX I have personally scanned and dumped from floppy. A small subset and in no way intended to be the MSX Info Pages, just my scans and dumps.

History of MSX Info Pages

Around 2000 I started collecting retro home computers, MSX and many other 8 bit CPU based small computers. And developed the MSX Info website full with documents and software, initialy on the machines I owned like SVI.738 and NMS8280 and the interfacing with electronics. The house quickly filled with hundreds of machines, the website exploded with scanned documents and files.

All things come to an end, in 2012 I started selling the huge collection to enable a move to a smaller place and recover some of my investments. So in 2015 all was gone, the photos and files are all that is left.

I continued to update the website MSX Info Pages with what was sent to me or collected from the internet. In 2019 I decided to stop also with the website, thanks to the continued leeching and deep-linking by the unresponsive maintainers of msx.org. The quality content of the website, my pages, my scans, are what made the MSX Info Pages fun for me, not being used as free file storage to by the wiki maintainers of msx.org. So be it. The MSX scene is often an unpleasant environment.

A static copy, thanks to Arnaud de Klerk aka TFH, is available at at TFHs server.

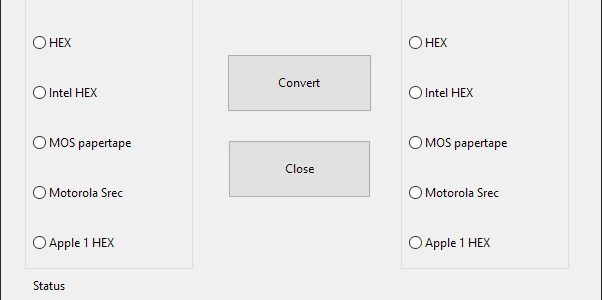

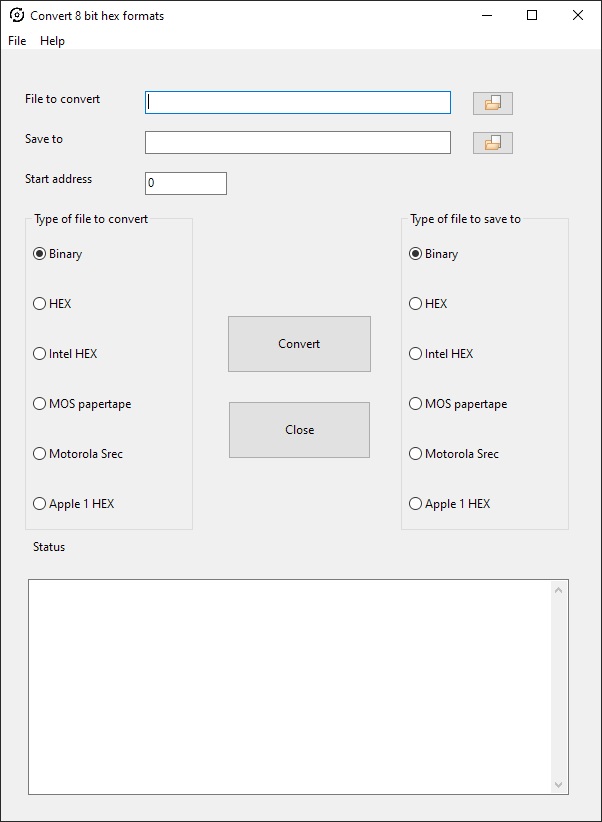

A program to convert between hex or binary files for 8 bit systems with a 64K address space.

V2 adds the Wozmon Apple 1 format and allow multipart Intel Hex, MOS Papertape and Motorola S records.

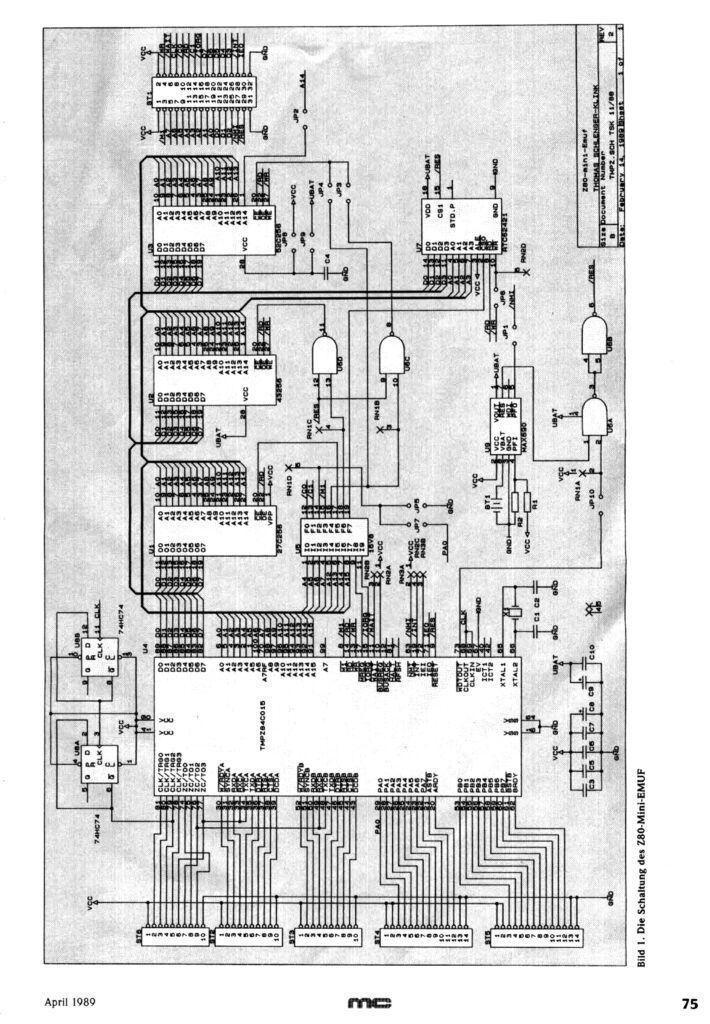

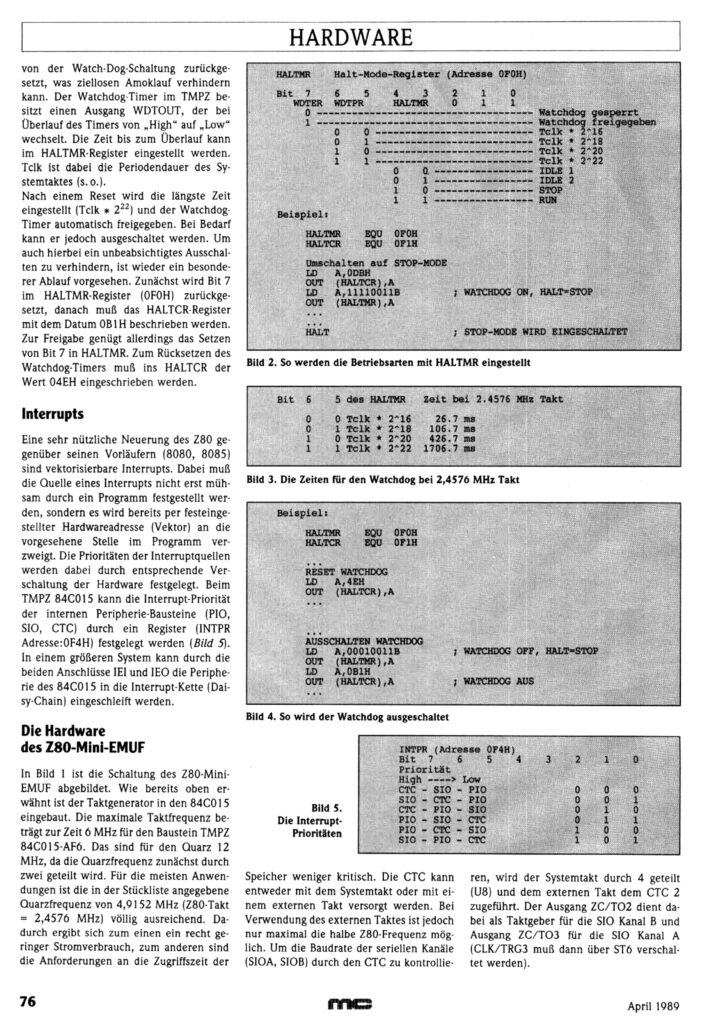

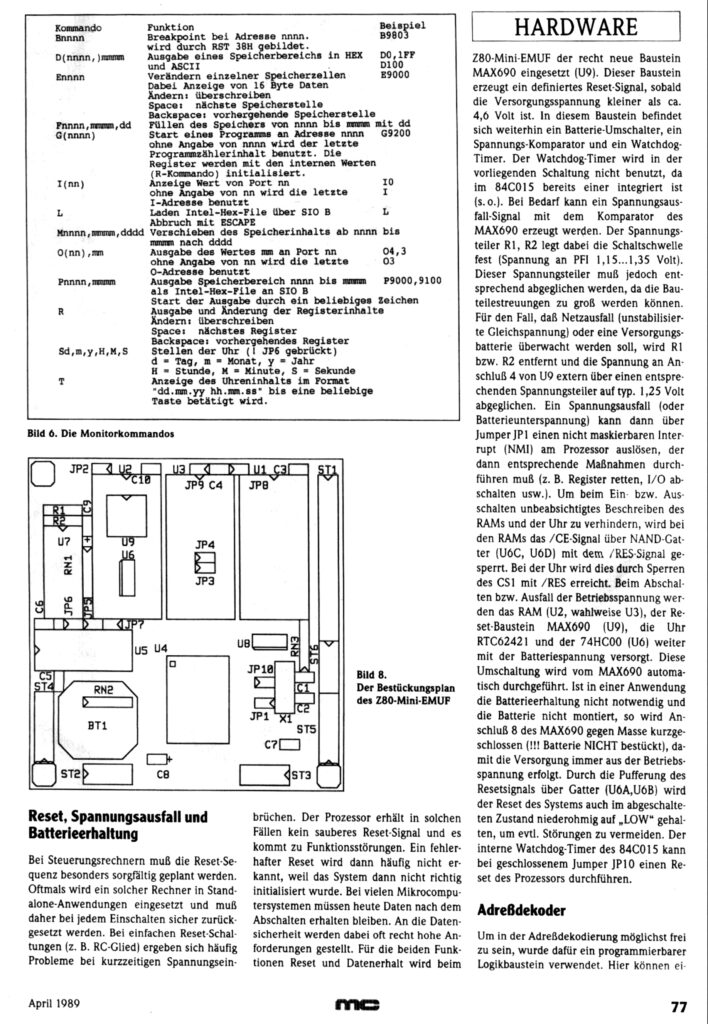

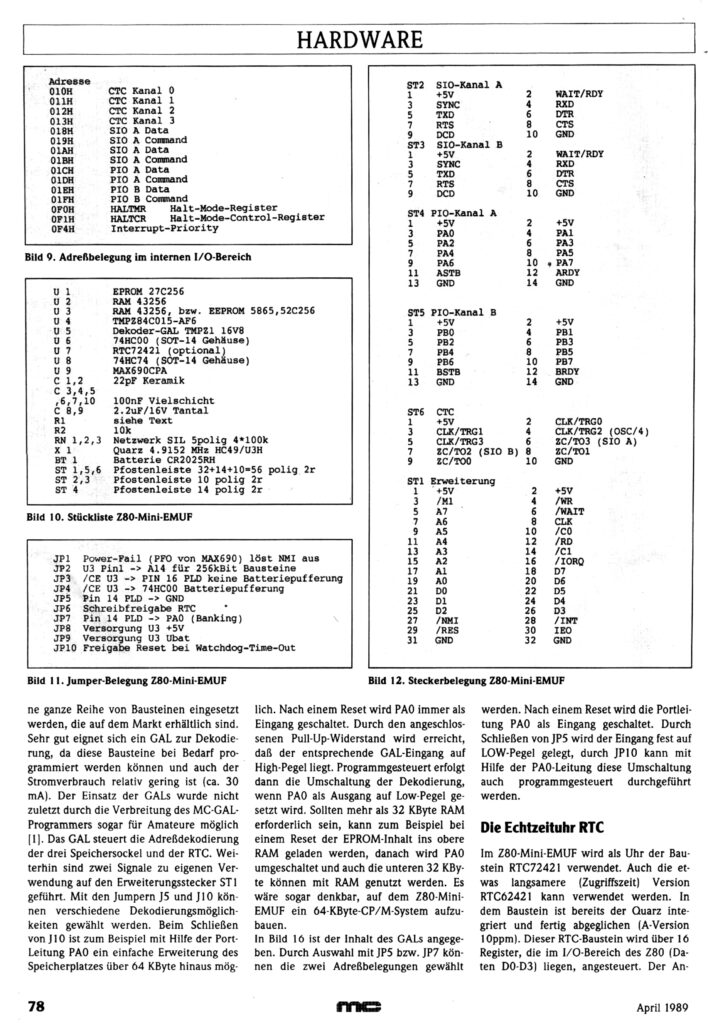

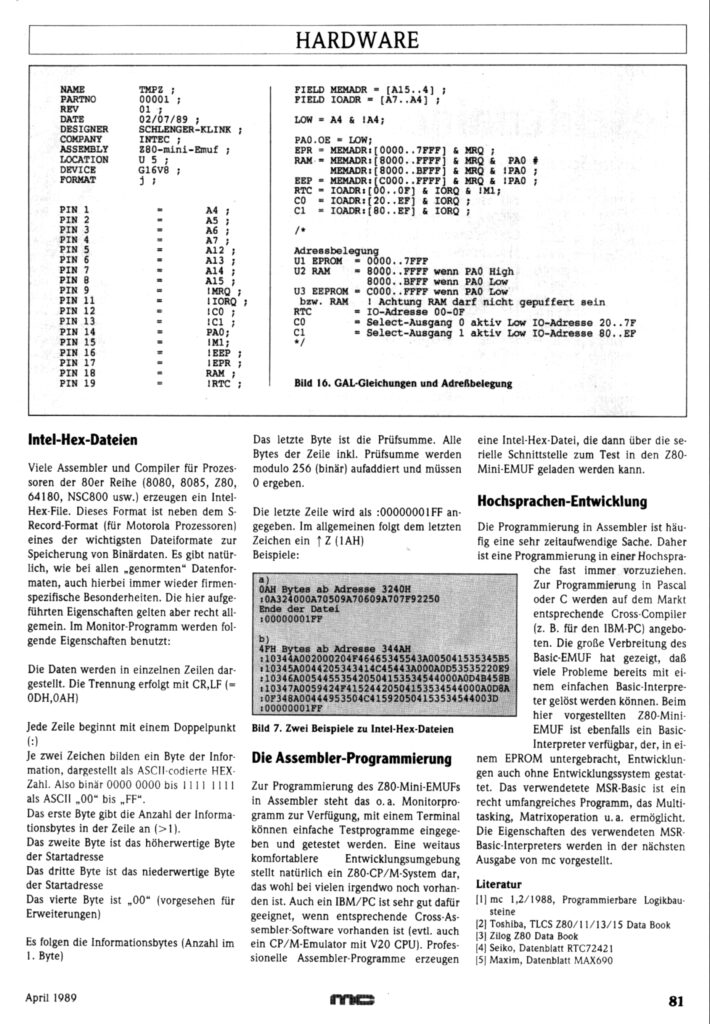

Based on the TMPZ84C015, a Z80 system-on-a-chip ‘Der Z80-Mini-EMUF was published in MC April 1989.

The EMUF family lived on!

Thanks to Bram Prosman for the scan.

Z80-EMUF, 1984 Issue 6

Z80 CPU at 2MHz, 2x Z80 PIO, 1x 2716 EPROM, 1×6116 SRAM

On this page the original article, the printed test program in listing and hex format.

0001 0000 .org 0000h 0002 0000 ; Testprogramm für Z80 EMUF: 0003 0000 ; auf den Ausgängen der PIO's 0004 0000 ; wird nacheinander gezählt 0005 0000 0006 0000 RAM equ 8000h 0007 0000 0008 0000 PIO0 equ 0 0009 0000 PIO1 equ 10h 0010 0000 ; PIO Adressen: 0011 0000 ; PIO+0: Port A 0012 0000 ; PIO+1: Port B 0013 0000 ; PIO+2: Control Port A 0014 0000 ; PIO+3: Control Port B 0015 0000 0016 0000 3E CF EMUT1: ld a,11001111b; Initialisierung aller Ports auf Einzelbit Ein- und Ausgabe 0017 0002 D3 02 out (PIO0+2),a 0018 0004 3E 00 ld a,0 0019 0006 D3 02 out (PIO0+2),a 0020 0008 3E CF ld a,11001111b 0021 000A D3 03 out (PIO0+3),a 0022 000C 3E 00 ld a,0 0023 000E D3 03 out (PIO0+3),a 0024 0010 0025 0010 3E CF ld a,11001111b; Initialisierung PIO2 analog zu PIO1 0026 0012 D3 12 out (PIO1+2),a 0027 0014 3E 00 ld a,0 0028 0016 D3 12 out (PIO1+2),a 0029 0018 3E CF ld a,11001111b 0030 001A D3 13 out (PIO1+3),a 0031 001C 3E 00 ld a,0 0032 001E D3 13 out (PIO1+3),a 0033 0020 0034 0020 06 00 LOOP: ld b,0 0035 0022 78 L1: ld a,b 0036 0023 32 00 80 ld (RAM),a; RAM Adresse 00 .. FF wird angesprochen 0037 0026 3A 00 80 ld a,(RAM) 0038 0029 D3 00 out (PIO0+0),a 0039 002B 05 dec b 0040 002C C2 22 00 jp nz,L1 0041 002F 0042 002F 06 00 ld b,0 0043 0031 78 L2: ld a,b; jetzt 2. Port PIO0 0044 0032 32 00 80 ld (RAM),a; 0045 0035 3A 00 80 ld a,(RAM) 0046 0038 D3 01 out (PIO0+1),a 0047 003A 05 dec b 0048 003B C2 31 00 jp nz,L2 0049 003E 0050 003E 06 00 ld b,0 0051 0040 78 L3: ld a,b; jetzt 1. Port PIO1 0052 0041 32 00 80 ld (RAM),a; 0053 0044 3A 00 80 ld a,(RAM) 0054 0047 D3 10 out (PIO1+0),a 0055 0049 05 dec b 0056 004A C2 40 00 jp nz,L3 0057 004D 0058 004D 06 00 ld b,0 0059 004F 78 L4: ld a,b; jetzt 2. Port PIO1 0060 0050 32 00 80 ld (RAM),a; 0061 0053 3A 00 80 ld a,(RAM) 0062 0056 D3 11 out (PIO1+1),a 0063 0058 05 dec b 0064 0059 C2 4F 00 jp nz,L4 0065 005C 0066 005C C3 20 00 jp LOOP 0067 005F 0068 005F DS 1000h 0069 105F .END

Hex and listing of test program.

Photos and assembler listing from https://makerprojekte.de/z80-emuf-wiederbelebt/