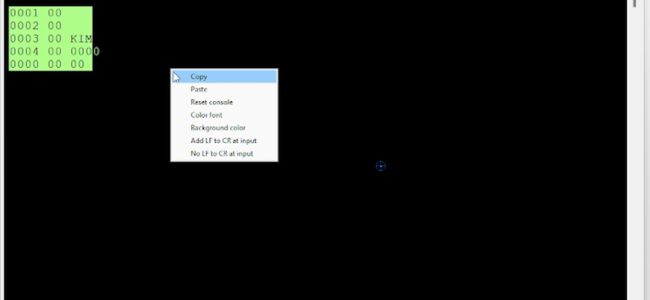

A demo of the new facilities in the KIM-1 Simulator 2.2.1

Scroll, copy paste of the console.

New versions of KIM-1 and TIM Simulator with thanks to Eduardo Casino.

About small SBC systems

A demo of the new facilities in the KIM-1 Simulator 2.2.1

Scroll, copy paste of the console.

New versions of KIM-1 and TIM Simulator with thanks to Eduardo Casino.

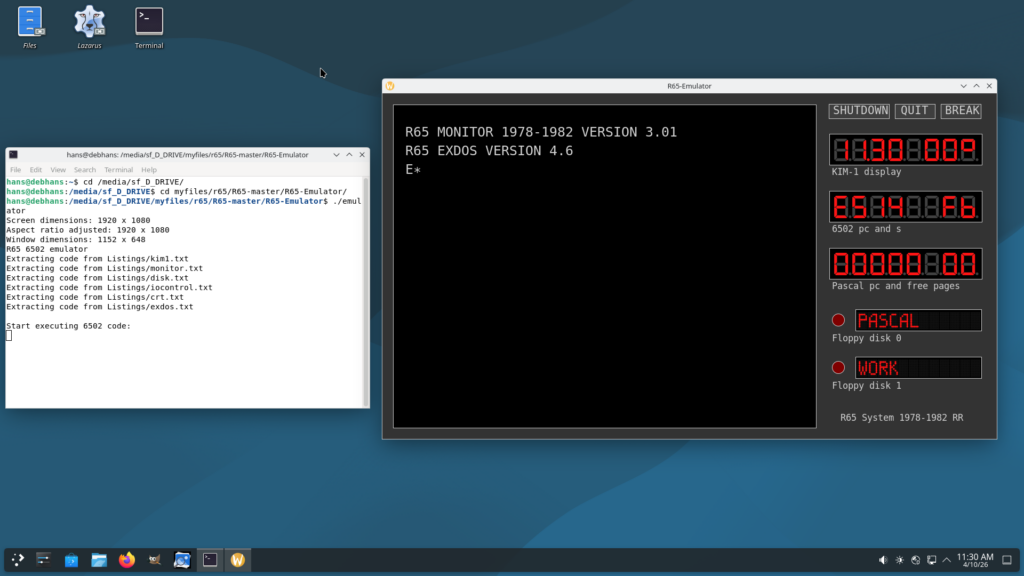

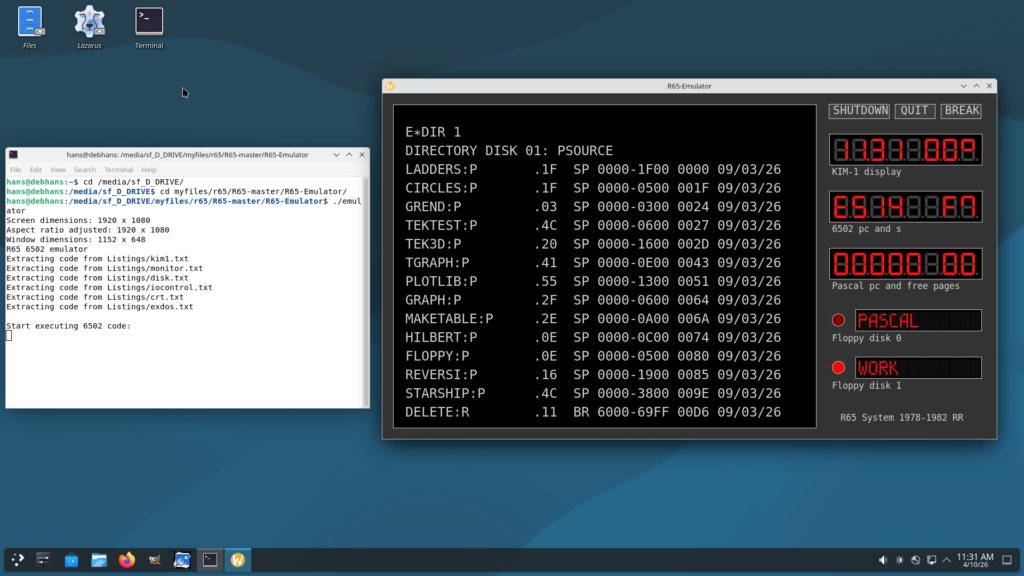

R65 – A late seventies computer built with a KIM-1 by Rene Richarz.

An amazing showcase of how far a KIM-1 and Pascal as programming language can go!

All information on the R65 and the emulator of this computer on the github archive of Rene Richarz, a work in progress!

Including sources and full documentation.

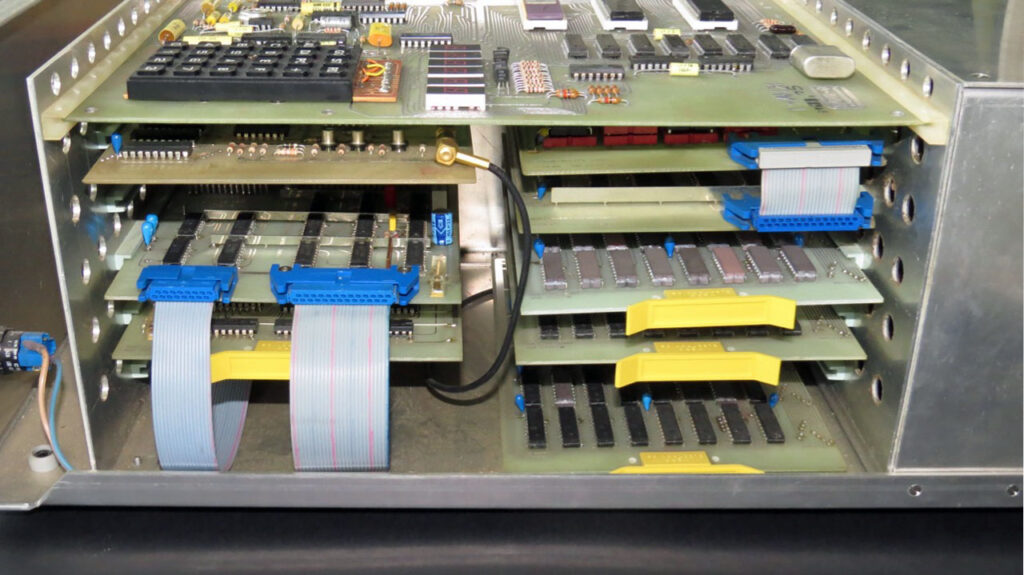

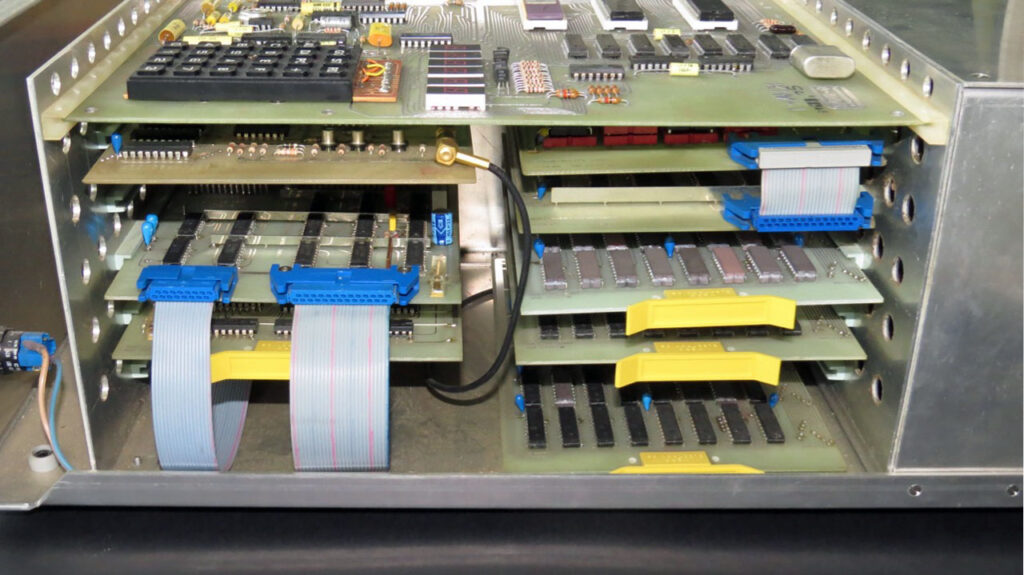

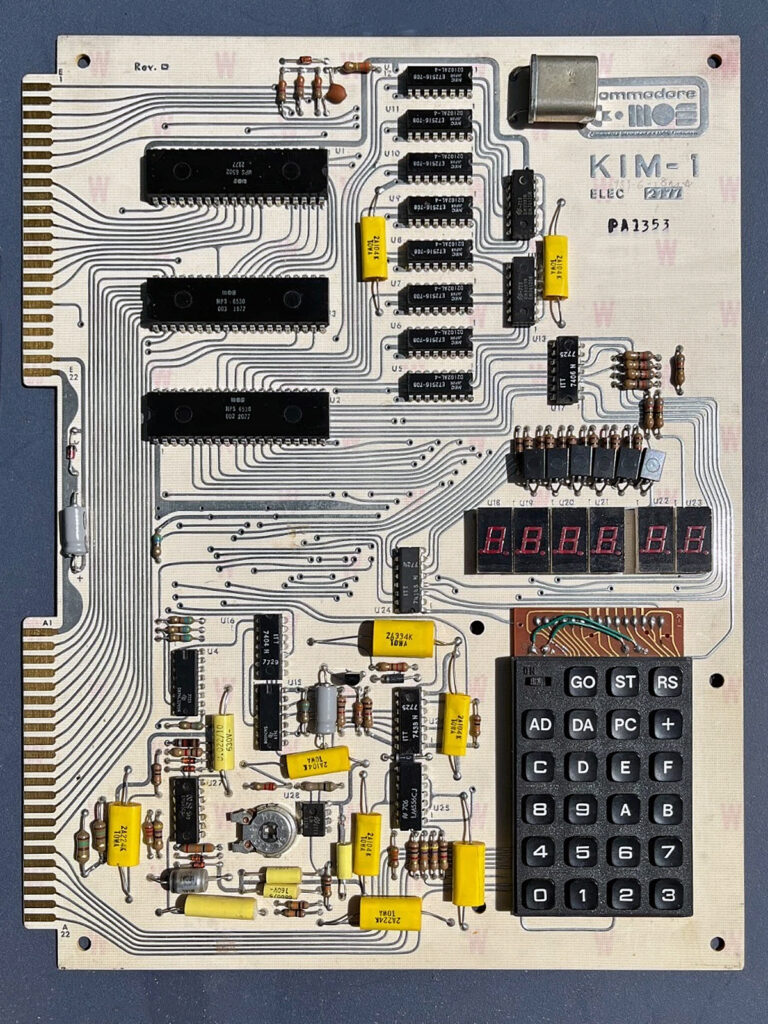

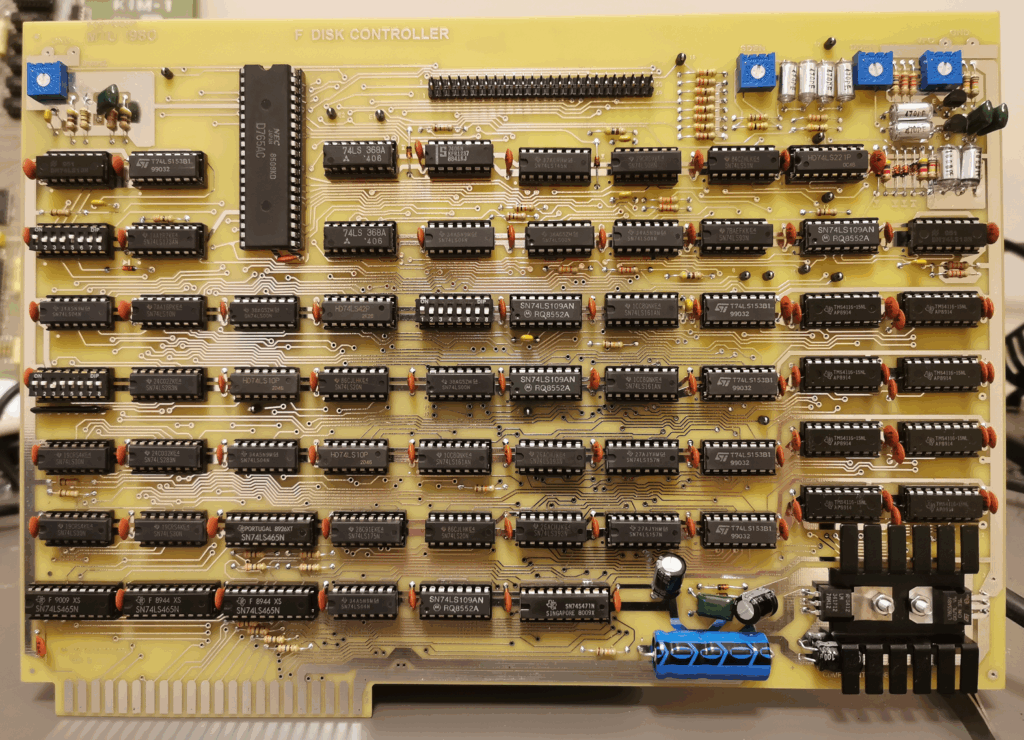

Original Job computer built 1977-1979

The R65 computer has been built 1977-1979 by Rene Richarztogether with Rudolf Baumann, who has built his own JOB computer at the same time with similar hardware. The picture above shows the open JOB computer. The original R65 computer has not survived. The floppy disks have also not survived.

Hardware specifications of the original R65 Computer:

– 6502 8-bit microprocessor

– 1 MHz clock speed

– 17 kByte, 33 kByte, 49 kByte RAM (expanded 2 times between 1977 an 1979)

– 2 kByte graphics RAM

– 10 kByte ROM

– 40 x 16 char monochrome display

– 224 x 118 dot monochrome graphics display (switchable with char display)

– 2 floppy disk drives. Formatted capacity 199680 bytes each.

– Interfaces: Teletype, RS232, parallel printer, audio tape, golf-ball typewriter, tv

R65 – A late seventies computer built with a KIM-1 by Rene Richarz.

All information on the R65 and the emulator of this computer on the github archive of Rene Richarz, a work in progress!

Original Job computer built 1977-1979

The R65 computer has been built 1977-1979 by Rene Richarztogether with Rudolf Baumann, who has built his own JOB computer at the same time with similar hardware. The picture above shows the open JOB computer. The original R65 computer has not survived. The floppy disks have also not survived.

Rene Richarz (left) and a guest looking at the R65 system

Hardware specifications of the original R65 Computer:

– 6502 8-bit microprocessor

– 1 MHz clock speed

– 17 kByte, 33 kByte, 49 kByte RAM (expanded 2 times between 1977 an 1979)

– 2 kByte graphics RAM

– 10 kByte ROM

– 40 x 16 char monochrome display

– 224 x 118 dot monochrome graphics display (switchable with char display)

– 2 floppy disk drives. Formatted capacity 199680 bytes each.

– Interfaces: Teletype, RS232, parallel printer, audio tape, golf-ball typewriter, tv

Most of the original 6502 assembler programs have been written by Rene Richarz 1977 – 1980, some of them based on code snippets found in publications. They have been modified and improved up to 1982 by Rudolf Baumann for his hardware. Thanks to him for keeping his hardware (not functional anymore) and printed program listings up to today. The program listings have been scanned and digitized 2018 by Rene Richarz.

The main software includes the original KIM-1 ROM and 4 modules, which were burned on EPROMS at that time. These modules are:

– A system monitor module, which is executed at startup

– A disk controller module, which handles the access to the floppy drives

– A IO controller module, which handles other IO

– A CRT controller module, which handles the display

These 4 modules run in their original version, with the exception of a few minor bug fixes.

Emulator

The software also includes an extended disk operating system module (EXDOS), which has been modified substantially. A number of commands have been added to the emulator version of the extended disk operating system module. They allow to import and export serial data files to and from the Linux operating system and to “change floppy disks”. The emulator emulates 2 floppy drives as in the original system, but can handle an unlimited number of floppy disks.

The original text editor has not been implemented, because it must be considered very user unfriendly given todays standards. Instead, using the “edit” command of EXDOS, the file to edit is automatically exported to the Linux file system, and the Linux text editor “mousepad” is called. Once mousepad is quit, the edited file is imported automatically back into the R65 file system. This happens automatically and very quickly.

Please note that even so the emulator includes the original KIM-1 ROM, it is NOT a KIM-1 emulator. Only the KIM-1 hardware required for the operation of the R65 computer system is emulated in the emulator.

The emulator uses a very nice 6502 emulation module written 2011 by Mike Chambers (miker00lz@gmail.com). The look and feel of the emulated system is very similar to the original. But everything is much faster.

The original R65 computer included a BASIC interpreter, and an improved Tiny Pascal compiler. The R65 Pascal system, which was quite powerful for a 8-bit microprocessor at that time, and the BASIC interpreter have been reconstructed.

The floating point subroutines of the R65 Pascal system were published in Dr. Dobbs Journal, Volume 1, Number 7, August 1976, page 17 by Steve Wozniak.

It is easy to compile and run the emulator on any Debian system. The installation is well described.

You may have some trouble with the font installation, the script failed for me on bot the Raspberry as Debian Linux X86 due to protection errors. I copied the fints by hand and set the file protection to read for the world.

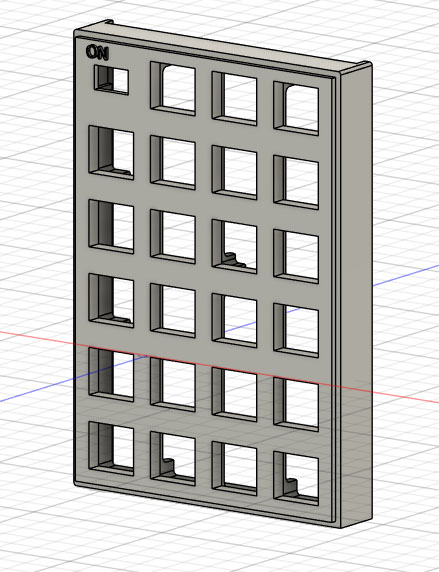

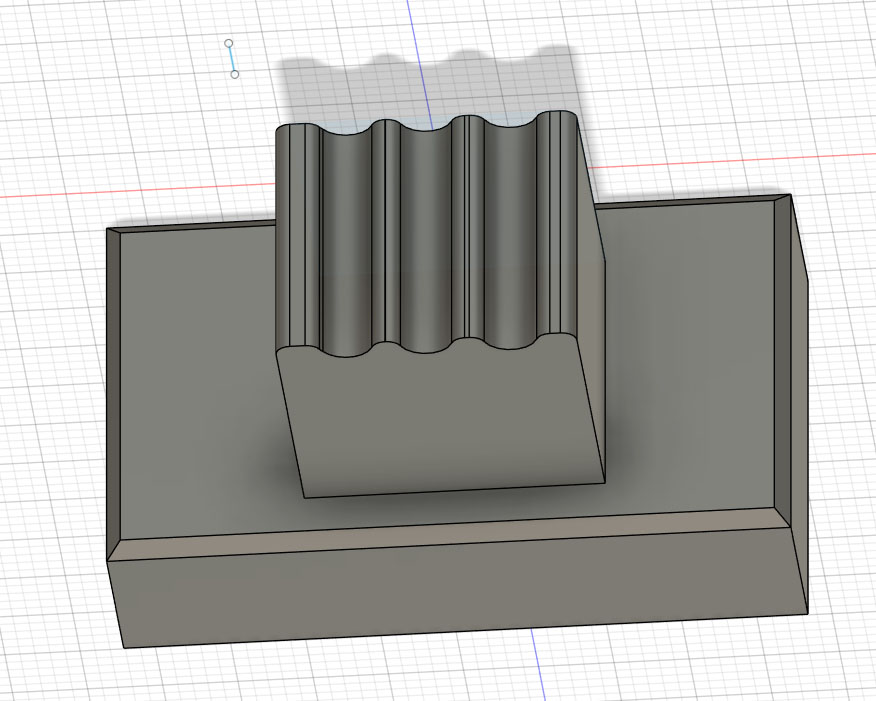

The DIY KIM-1 keypad case and button 3D designs have been slightly improved:

The case has a small cutout around the top edges as the original.

The button has some ribbles as the original has.

After cleaning up and repairing the keyboard of a white KIM-1 Rev D I found a second one, as new!

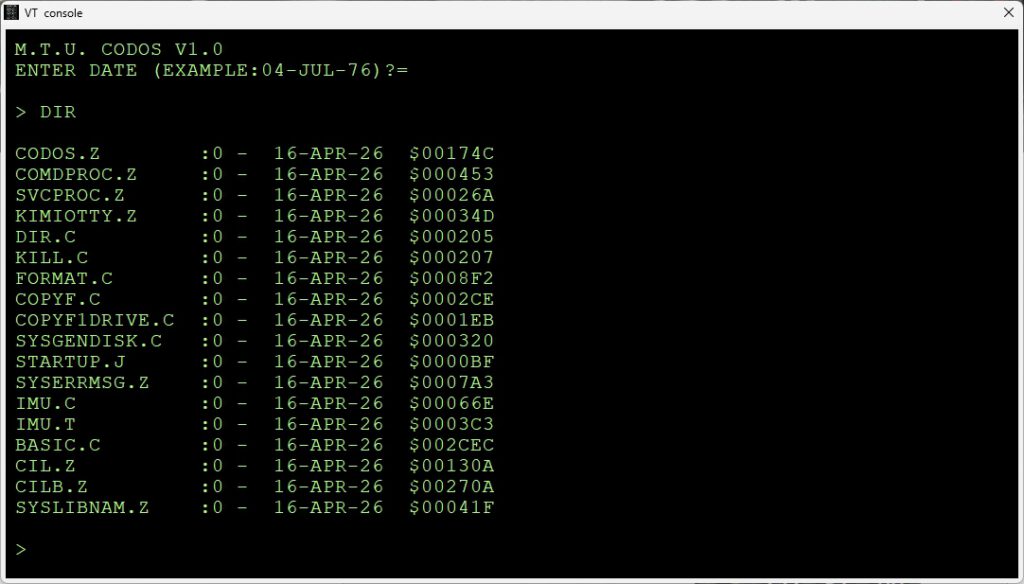

MTU K-1013 FDC emulation added to the KIM-1 Simulator.

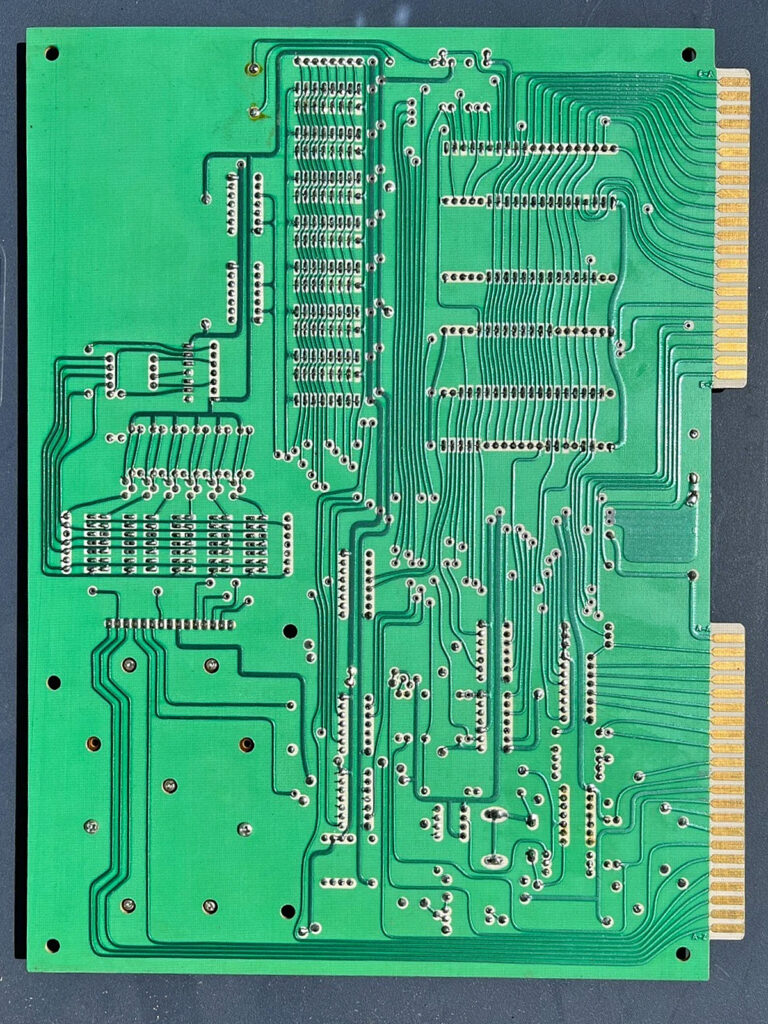

CODOS is the operating system developed by MTU for their K-1013 based computer systems.

Eduardo Casino reverse engineered CODOS for the KIM-1 form teh MTU-130 based CODOS V2

And now Eduardo has ported a version special to the KIM-1 Simulator with K-`013 simulation. See CODOS on his github archive.

The main changes are to support the KIM-1 Simulator character I/O, using the ACIA simulation instead of low level KIM-1, for non-blocking character input.

How to start CODOS

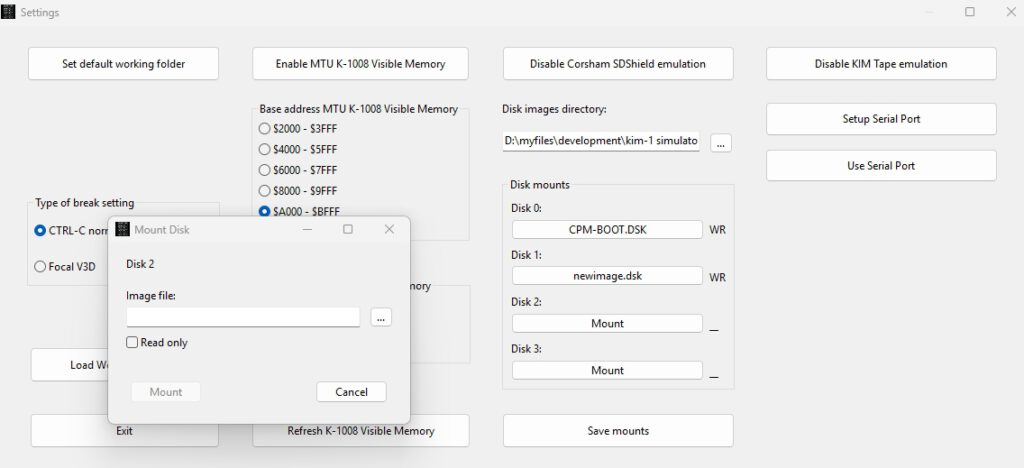

To start using the K-1013 FDC go to the menu settings.

Make sure the first disk mounted is codos17.imd. The IMD files are in the K-1013 folder.

Now you start CODOS.

The disks, stored in files with type .imd are in the K-1013 folder. You can mount/dismount/create disks from the Settings screen.

You can have as many as four.

On the Settings screen the disks mounts are shown. Click on the name of a mounted disk or an empty Mount, to go to the Mount Disk dialog. Mount/Dismount here, in Write or read Only mode.

Press the the three … next to the field Image file to select or create a disk image.

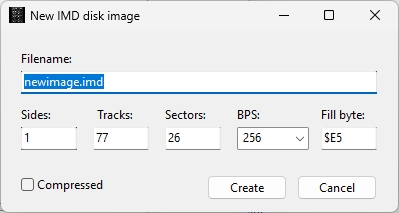

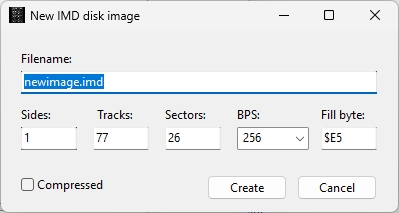

Press New and you get the New diskimage dialog.

There is also the IMU utility in CP/M-65 to work with disks: mount/unmount, list the directory of the K-1013 folder. create/delete and copy.

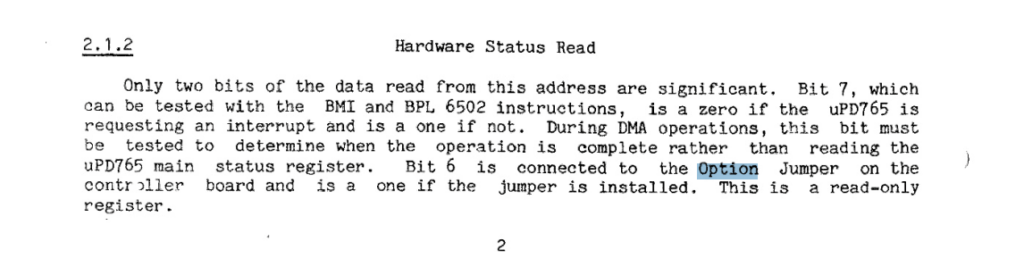

The option switch

The option switch does this:

It just sets bit 6 in the HSR. For example, the boot PROM can use it to decide whether to boot the OS or just follow the normal KIM 1 boot procedure.

CP/M-65 is a native port of Digital Research’s seminal 1977 operating system CP/M to the 6502.

Developed by David Given. Ported to many 6502 systems, see the original github archive.

Currently you can cross-assemble programs from a PC, as well as a working C toolchain with llvm-mos. For native development, there’s a basic assembler, a couple of editors, a BASIC, and a byte-compiled Pascal subset and interpreter.

Eduardo Casino ported CP/M-65 to the KIM-1 with an MTU K-1013 FDC, directly connected SD card module, the 1541 drive or Corsham Technology SD CARD/RTC Shield.

And now Eduardo has ported a version special to the KIM-1 Simulator with SD Card/RTC Shield simulation. See his fork of CP/M-65 on his github archive. Several branches are available, development versions with a.o. the KIM-1 Simulator version.

The main changes are to support the KIM-1 Simulator character I/O, using the ACIA simulation instead of low level KIM-1, for non-blocking character input.

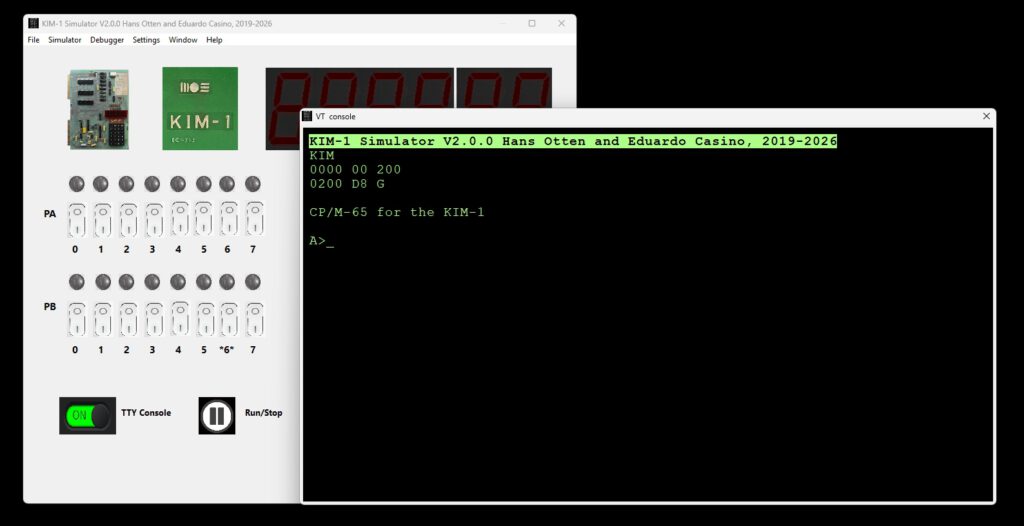

How to start CP/M-65

To start using the K-1013 FDC go to the menu settings.

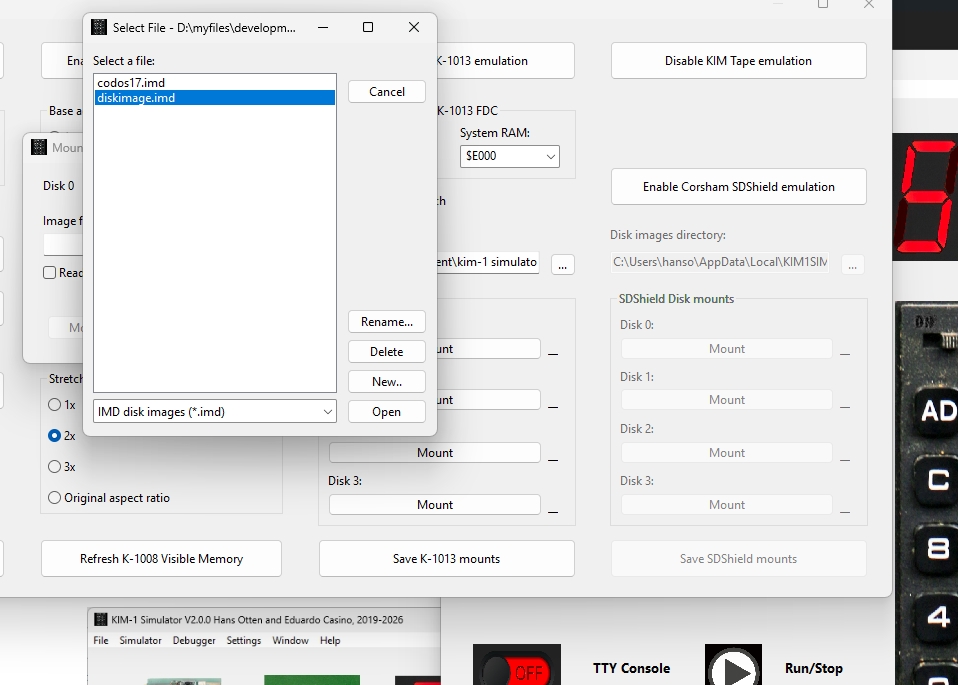

Make sure the first disk mounted is diskimage.imd. The IMD files are in the K-1013 folder.

Now you start CP/M-65.

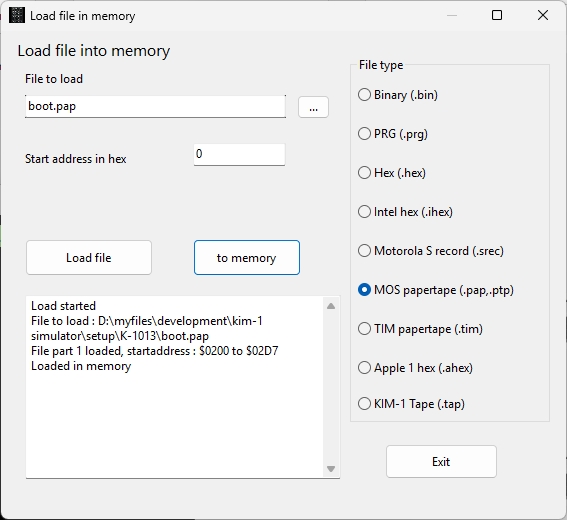

Load the file boot.pap into memory with File – Load file in Memory – papertape.

The file is in the K-1013 folder.

The disks, stored in files with type .imd are in the K-1013 folder. You can mount/dismount/create disks from the Settings screen.

You can have as many as four.

On the Settings screen the disks mounts are shown. Click on the name of a mounted disk or an empy Mount, to go to the Mount Disk dialog. Mount/Dismount here, in Write or read Only mode.

Press the the three … next to the field Image file to select or create a disk image.

Press New and you get the New diskimage dialog.

There is also the IMU utility in CP/M-65 to work with disks from within CP/M-65: mount/unmount, list the directory of the K-1013 folder. create/delete and copy.

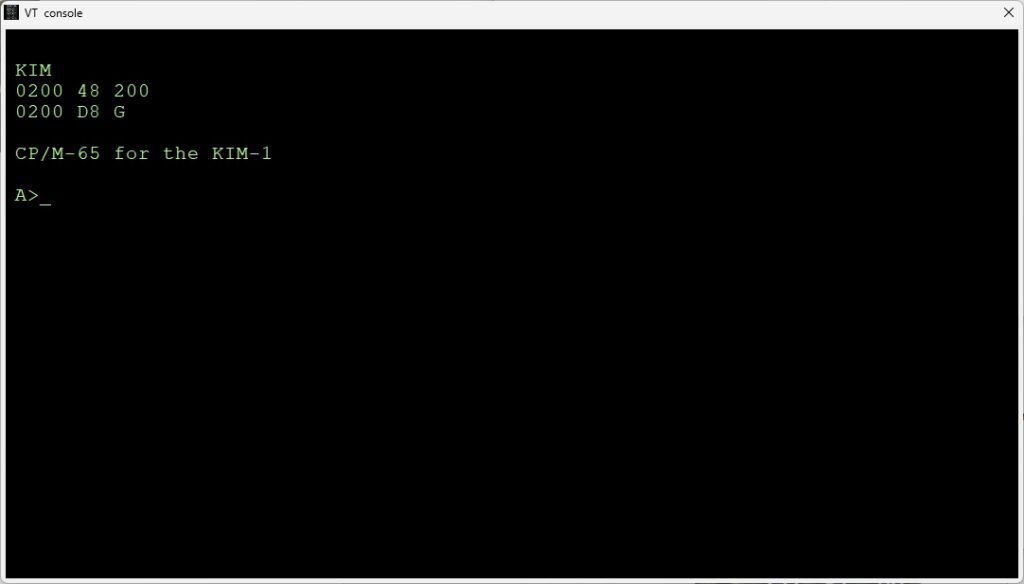

Example session

KIM

0200 D8

KIM

0200 D8 G

CP/M-65 for the KIM-1

A>dir

A: SCRVT100 COM : IMU COM

A: IMU TXT : SYS COM

A: PASC PAS : ASM TXT

A: HELLO ASM : DEMO SUB

A: ASM COM : ATTR COM

A: BEDIT COM : CAPSDRV COM

A: COPY COM : CPUINFO COM

A: DEVICES COM : DINFO COM

A: DUMP COM : LS COM

A: STAT COM : SUBMIT COM

A: MORE COM : BEDIT ASM

A: BEDIT TXT : DUMP ASM

A: LS ASM : CPM65 INC

A: DRIVERS INC : ATBASIC COM

A: ATBASIC TXT : OBJDUMP COM

A: MKFS COM : ADM3ADRV COM

A: ADM3ATST COM : CLS COM

A: LIFE COM : QE COM

A: SCRNTEST COM : VT52DRV COM

A: VT52TEST COM : KBDTEST COM

A: MBROT COM : DS COM

A: DS TXT : PINT COM

A: PASC OBB : PLOAD COM

A: HELLO PAS : IMU3 TXT

A: HELLO SYM

A>pint PASC.OBB PASC.PAS PASC.OBS

Pascal-M interpreter for CP/M-65: B66F bytes free

Pascal-M compiler V2k1 for CP/M-65

Processing: writeerr

Processing: beginlin

Processing: endline

Processing: error

Processing: stringsi

Processing: nextchar

Processing: insymbol

Processing: enterid

Processing: searchse

Processing: searchid

Processing: getbound

Processing: hexout

Processing: writeout

Processing: bytegen

Processing: wordgen

Processing: genujpen

Processing: plantwor

Processing: skip

Processing: test1

Processing: test2

Processing: intest

Processing: constant

Processing: comptype

Processing: isstring

Processing: simplety

Processing: fieldlis

Processing: typ

Processing: constdec

Processing: typedecl

Processing: vardecla

Processing: paramete

Processing: procdecl

Processing: ldcigen

Processing: ldagen

Processing: lodgen

Processing: condgen

Processing: loadsetc

Processing: cspgen

Processing: incgen

Processing: load

Processing: store

Processing: loadaddr

Processing: falsejum

Processing: calluser

Processing: selector

Processing: variable

Processing: processt

Processing: readproc

Processing: processt

Processing: writepro

Processing: newstate

Processing: releases

Processing: resetrew

Processing: closepro

Processing: assignpr

Processing: getcomma

Processing: ordfunc

Processing: succfunc

Processing: predfunc

Processing: chrfunc

Processing: oddfunc

Processing: eofeolns

Processing: callnons

Processing: call

Processing: opgen

Processing: setexpre

Processing: factor

Processing: term

Processing: simpleex

Processing: expressi

Processing: assignme

Processing: compound

Processing: ifstatem

Processing: casestat

Processing: repeatst

Processing: whilesta

Processing: forstate

Processing: statemen

Processing: body

Processing: block

Processing: stdnames

Processing: enterstd

Processing: enterstn

Processing: enterund

Processing: initiali

Processing: compileh

Processing: compilep

Processing: skipspac

Processing: getword

Processing: findend

Processing: openfile

Processing: closefil

Processing: dumperro

Processing: cpascalm

Compilation successful.

No compilation errors PASC.PAS

A>pload PASC.OBS PASC.OBB

Opening input file...

Opening output file...

Reading OBP...

Seen 94 procedures

Writing output file...

Closing output file...

Success.

A>type HELLO.PAS

program HelloWorld;

begin

writeln('Hello from Pascal!')

end.

A>

A>pint PASC.OBB HELLO.PAS HELLO.OBS

Pascal-M interpreter for CP/M-65: B66F bytes free

Pascal-M compiler V2k1 for CP/M-65

Processing: hellowor

Compilation successful.

No compilation errors HELLO.PAS

B>A:pload A:HELLO.OBS HELLO.OBB

Opening input file...

Opening output file...

Reading OBP...

Seen 1 procedures

Writing output file...

Closing output file...

Success.

B>A:pint HELLO.OBB

Pascal-M interpreter for CP/M-65: B66F bytes free

Hello from Pascal!

B>

The emulation of the MTU K-1013 floppy Disk controller card allow you to use the CODOS and CP/M65 operating systems on the KIM-1 Simulator.

Read here all about the actual K-1013 card, incluidng a real replica by Eduardo Casino.

Replica by Eduardo Casino

The K-1013 emulation uses the same resources as the K-1013 card, but onlky if enabled.

The supporting files for the K-1013 are in the folder K-1013 and contain:

boot.pap bootrom.bin codos17.imd diskimage.imd mounts.cfg t.txt

The usage of these files is explained on this page. You can add any file there at wish.

To start using the K-1013 go to the menu settings.

Now you either start CP/M-65 or CODOS.

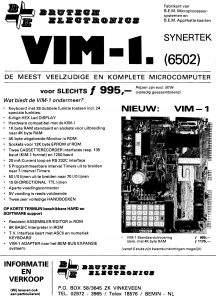

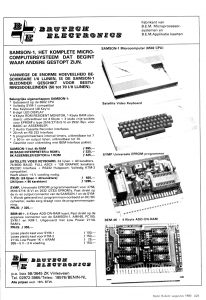

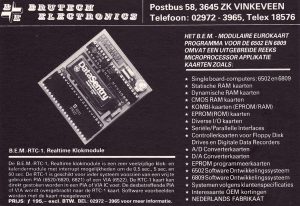

Brutech and the Radio Bulletin magazine worked together. The hardware produced or resold by Brutech was offered to the magazine for reviews. And Brutech placed many advertisements in the magazine. I visited the Brutech offices several times, it was close to where I lived.

|

BEM-1 card, as used in the KIM memory expansion article November 1977 |

|

The BEM bus |

|

Brutech sold the VIM-1 and SYM-1, with their cards as expansions. Review in Radio Bulletin November 1978 |

|

Brutech sold also the PC100, the Siemens OEM version of the AIM 65. Again the expansions could be used, same bus. Review in Radio Bulletin August 1980 |

|

The AIM 65 and KTM-2 packaged as the Samson system,. the BEM-4 memory card, the SYMP universal programmer. Review in Radio Bulletin November 1980 |

|

BEM RTC1 card, advert in the RB CB Special 1980 |

|

BEM-Impact 1000, a BEM-bus based development system, review in Radio Bulletin Oktober 1980 |

|

BEM Eurocard system, article by C.J. Bruyn, on the BEM bus, BEM-MON-1 (a TIM 6530 004 system!) and other cards |

|

Micro-gebeuren november 1977, BEM-1, other BEM cards |

|

Micro-gebeuren April 1980, BEM-PSIO-1 USART card, BEM-AD3, BEM-AD4 |

|

Micro-gebeuren Mei 1980, BEM-6 16/32K EPROM card |