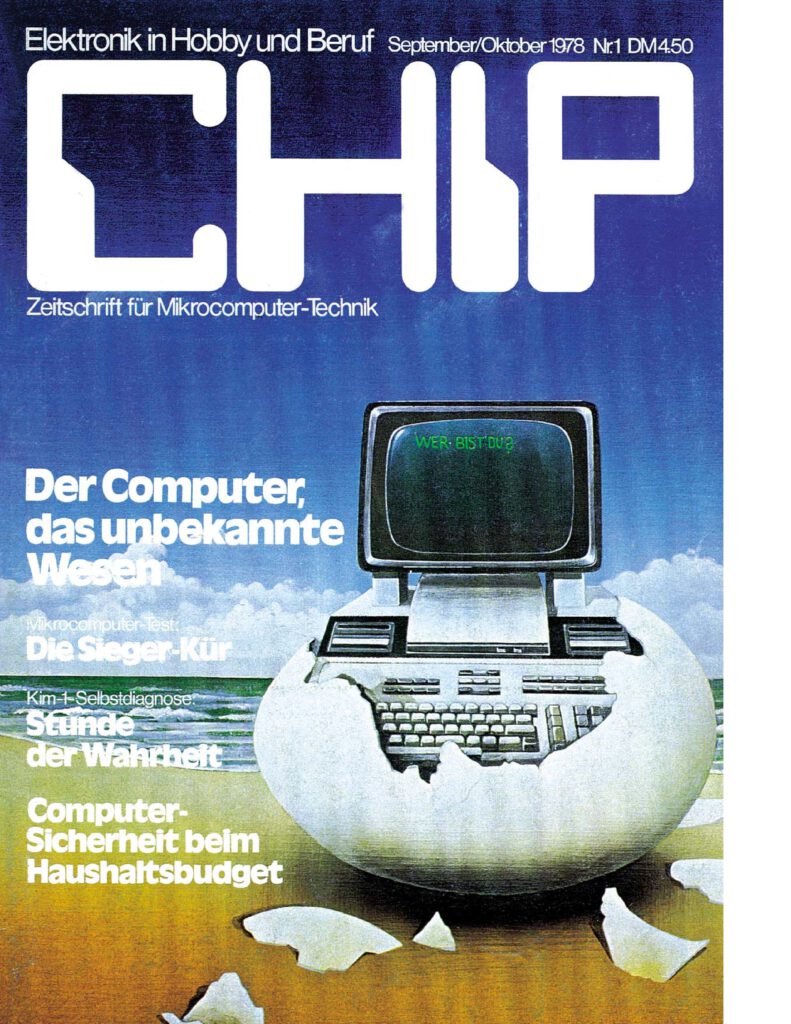

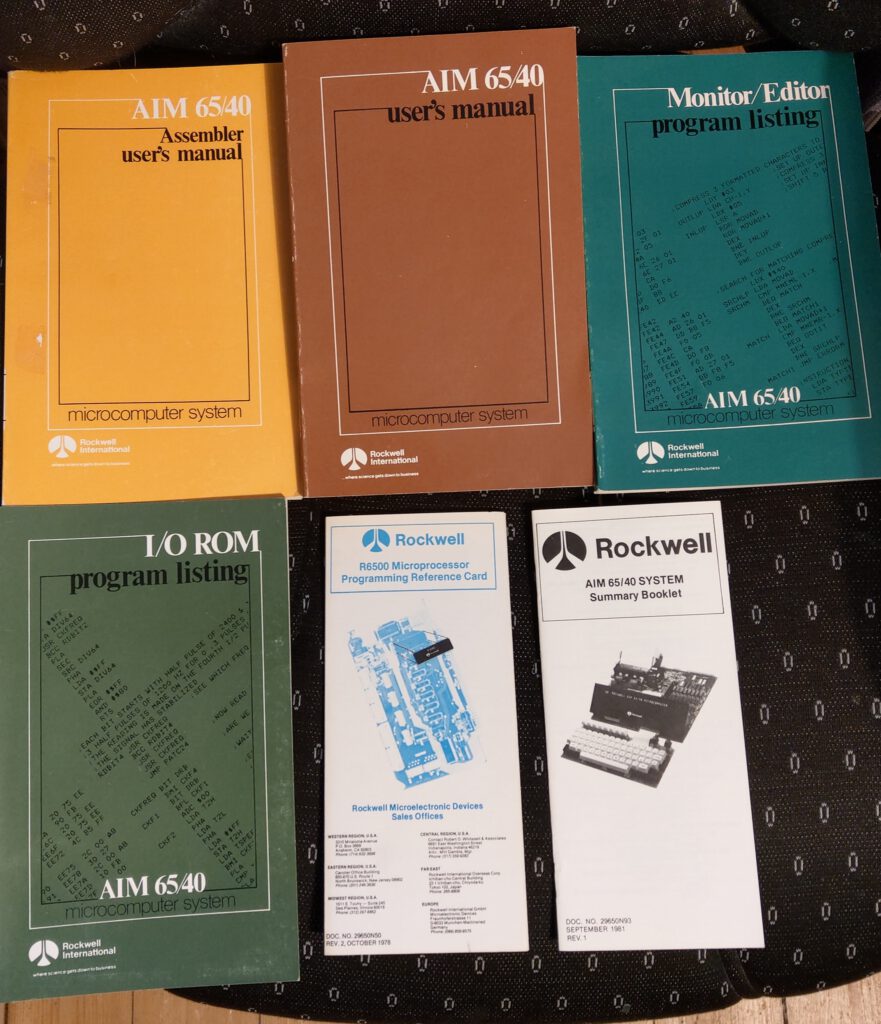

Pages from CHIP 9 1978 and CHIP Special 1981

About small SBC systems

Pages from CHIP 9 1978 and CHIP Special 1981

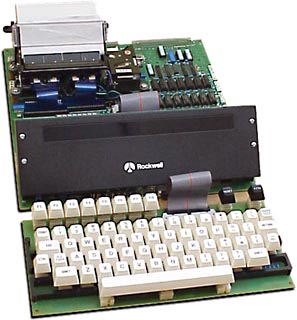

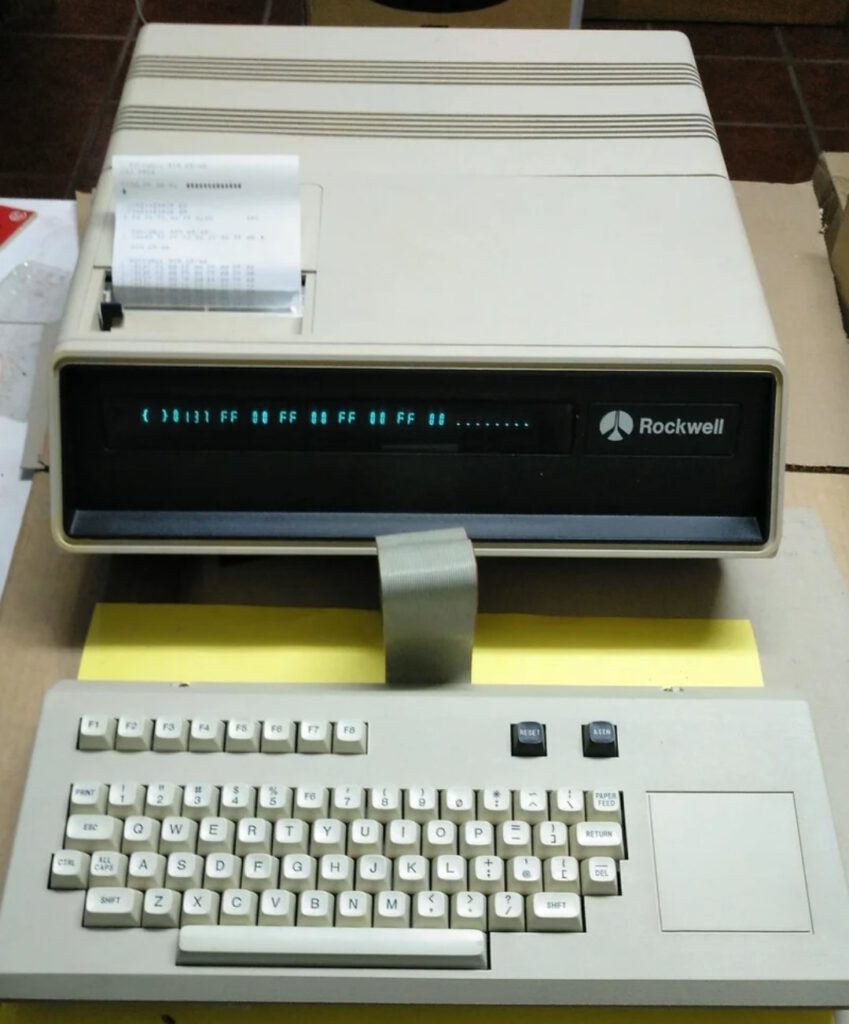

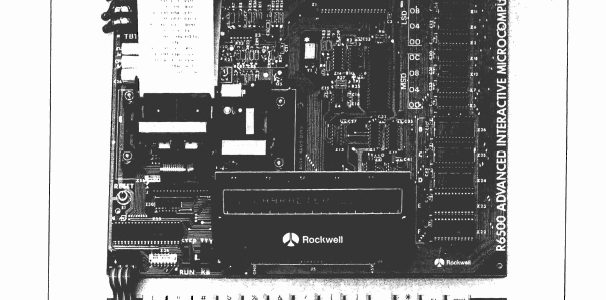

The AIM 65/40 is a SBC with the look and feel of the AIM 65, , with a 40 character display (over the 20 of the AIM 65). More memory, more ROM, User prioritized interrupts, RM 65 bus expansion.

(from http://oldcomputers.net/AIM-65-40.html)

AIM = Advanced Interactive Microcomputer.

65= Rockwell 6502 processor.

40= 40 column display.

An upgrade of the original Rockwell AIM-65, this model has a larger display, among other features.

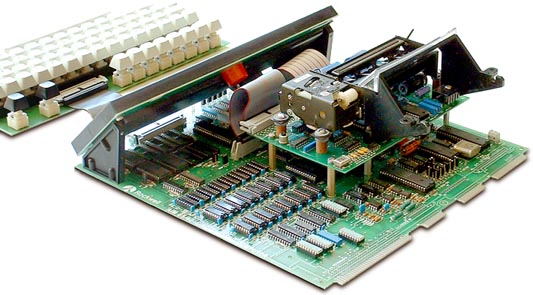

The four edge-card connectors are labeled:

From the Rockwell “Interactive” newsletter, issue no. 5:

Rockwell International will shortly be introducing the AIM 65/40. The AIM 65/40 microcomputer is made up of an R6502 based single board computer with on-board expansion to 65 kilobytes of memory, a full graphics 280 X N dot matrix or 40-column alphanumeric printer, a 40-character alphanumeric display, and a full ASCII keyboard with user assignable function keys.

An advanced generation of Rockwell’s popular AIM 65 microcomputer, the AIM 65/40 will be available as a complete system or as individual computer and intelligent peripheral modules.

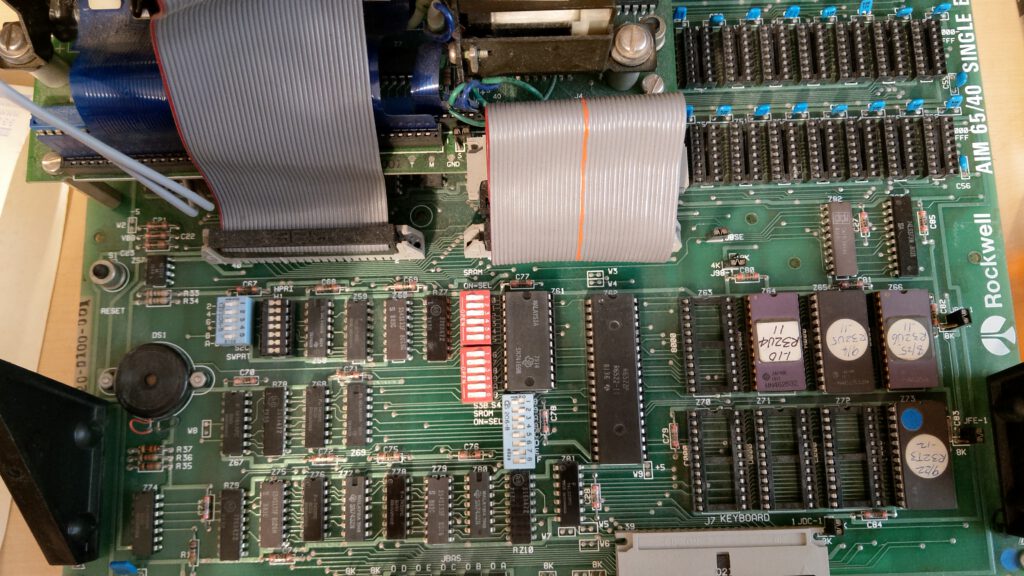

The AIM 65/40 Series 1000 single board computer modules feature system address expansion up to 128K bytes with on-board memory up to 48 kilobytes of RAM and up to 32 kilobytes of ROM or EPROM. Six level priority interrupt logic and 16-bit multi-mode timers are included for flexibility in production automation and laboratory control applications. Extensive I/O capability provides an RS-232C asynchronous communications interface channel with programmable data rates of up to 19,200 baud for terminals or modems, plus a 20 ma current loop TTY interface, dual audio cassette interfaces, and two user-definable 8-bit parallel ports with handshake control, two 16-bit timer/counters and an 8-bit serial shift register.

Three additional 8-bit parallel ports are directly programmable as dictated by the user’s application to provide more TTL level I/O or interface to keyboards, displays, and printer modules. Manufacturer supplied ROM resident software included with the AIM 65/40 Series 1000 computer provide I/O drivers for the intelligent peripherals and more. The printer connector is compatible with the Centronics parallel interface that is so popular with high speed dot matrix printers.

A buffered system bus accommodates off-board expansion via Rockwell’s RM 65 microcomputer modules which include intelligent peripheral controllers for mini or standard floppy disks, CRT monitors and the IEEE-488 instrumentation bus, plus additional communications interfaces and a selection of RAM, ROM and EPROM memory expansion options up to 128K bytes of memory and memory-mapped I/O capacity.

The AIM 65/40 Model 0600 graphics printer module consists of an intelligent microprocessor controller integrated with the printer mechanism. The module operates in two modes. Character mode operation prints upper and lower case ASCII character font formatted as 40-characters/line at 240 lines/minute. Full graphics mode outputs any data pattern desired as a 280 X N dot matrix. With its own microprocessor controller, user changeable character generator ROM, thermal head drivers, motor control, and parallel handshake ASCII interface, this freestanding peripheral minimizes demand on the AIM 65/40 central processor, permitting maximum system performance.

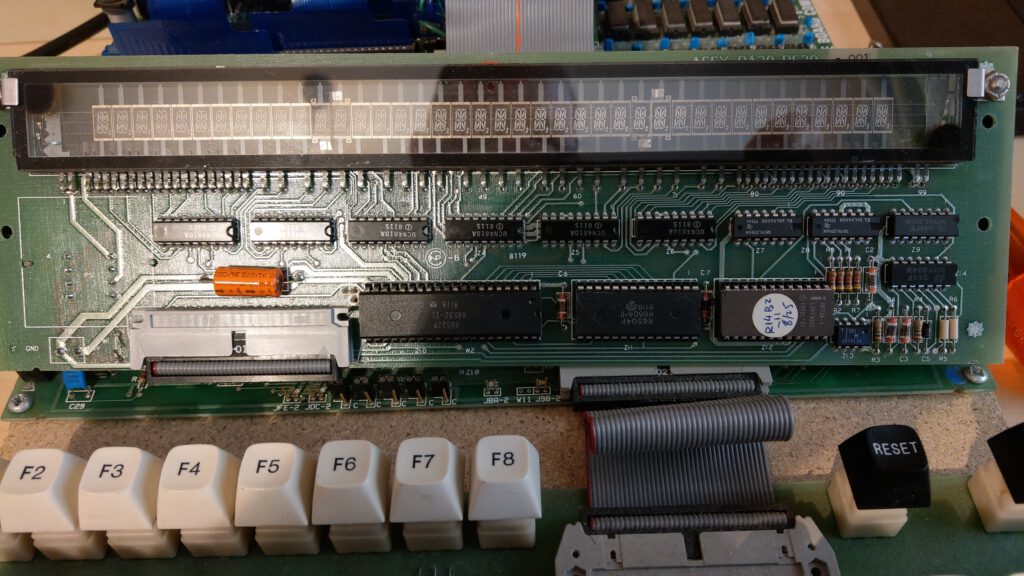

The Model 0400 display module features a bright, crisp vacuum fluorescent 40-character alphanumeric display. This stand-alone module has its own microprocessor controller for display of alphanumeric, special, and limited graphics characters, parallel handshake ASCII interface, support circuitry and operates from a single +5 volt power supply. Special control commands permit variable display timing, cursor control, auto-scroll, and character blinking.

The Module 0200 keyboard module provides a terminal style alphanumeric and special character keyboard matrix with 64 keys, including locking ALL CAPS, control, and eight user definable function keys. Three keys labeled ATTN, RESET, and PAPER FEED have dedicated lines to the interface connector.

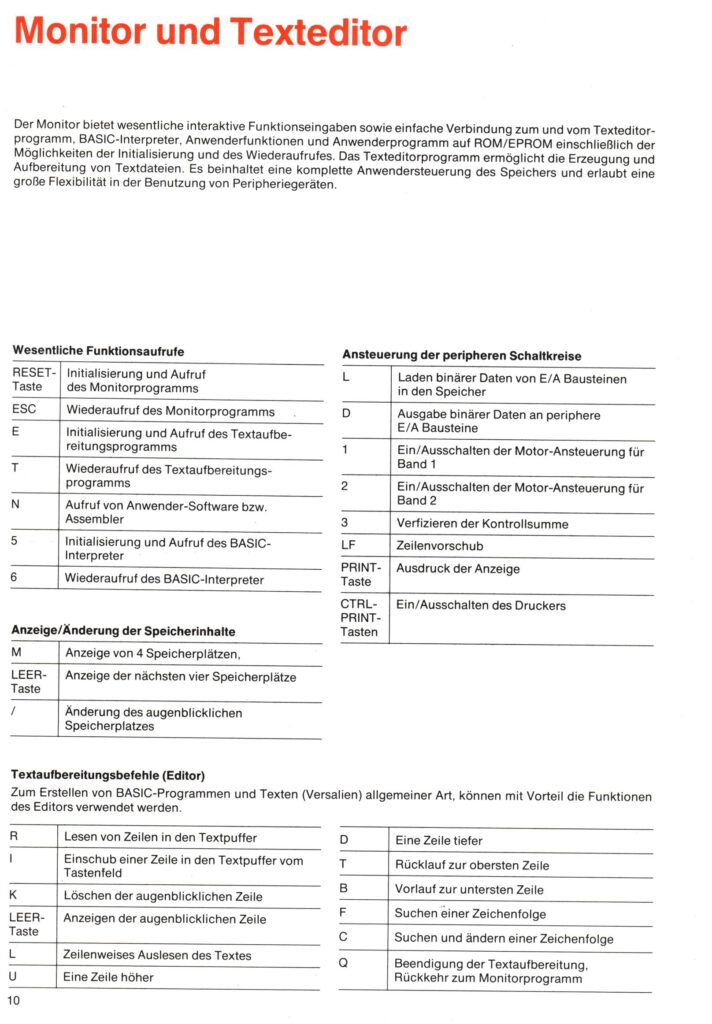

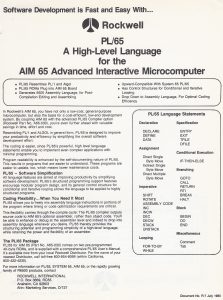

The AIM 65/40 Series 5000 incorporates a ROM resident software system and integrates all four modules into a complete microcomputer system. The interactive monitor software controls the AIM 65/40 system with single keystroke, self-prompting commands, supports software development with assembler, debug and control commands. A multi-file text editor supports both line and screen editing functions. Optional languages include a fully symbolic R6500 assembler and BASIC. FORTH, PASCAL, and PL/65 software packages are in development.

The AIM 65/40 is expected to be available sometime during the third quarter of 1981.

The following photos and files are given to me by Jörg, Ross Milbourne and David Colglazier, thanks!

|

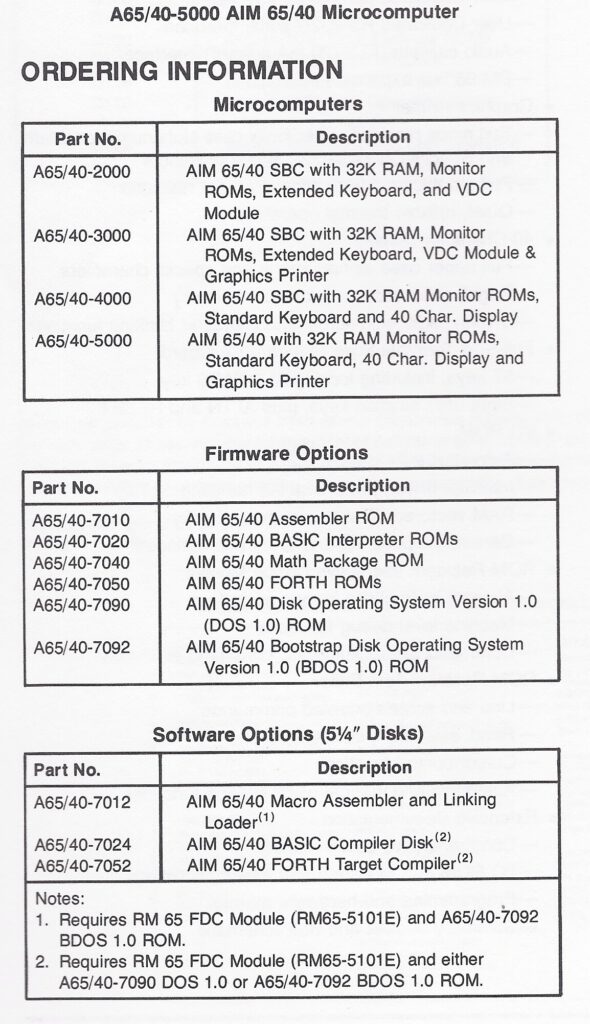

Datasheet AIM 65/40 A65/40-2000 -3000 -4000 -5000 |

|

AIM 65-40 System Users Manual |

|

AIM 65/40 Printer Circuit Diagram |

|

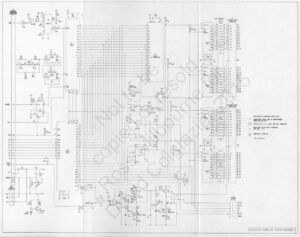

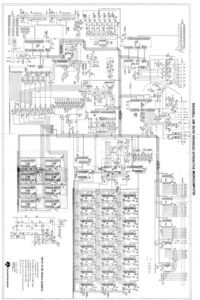

AIM 65/40 Circuit Diagram |

|

AIM65 40 Forth Manual |

|

AIM-65 Forth Supplement 65_40 |

ROMs

R14B2-11_8_25.bin

R32T3-12_9_22.bin

R32U4-11_1_10.bin

R32U5-11_9_4.bin

R32U6-11_8_25.bin

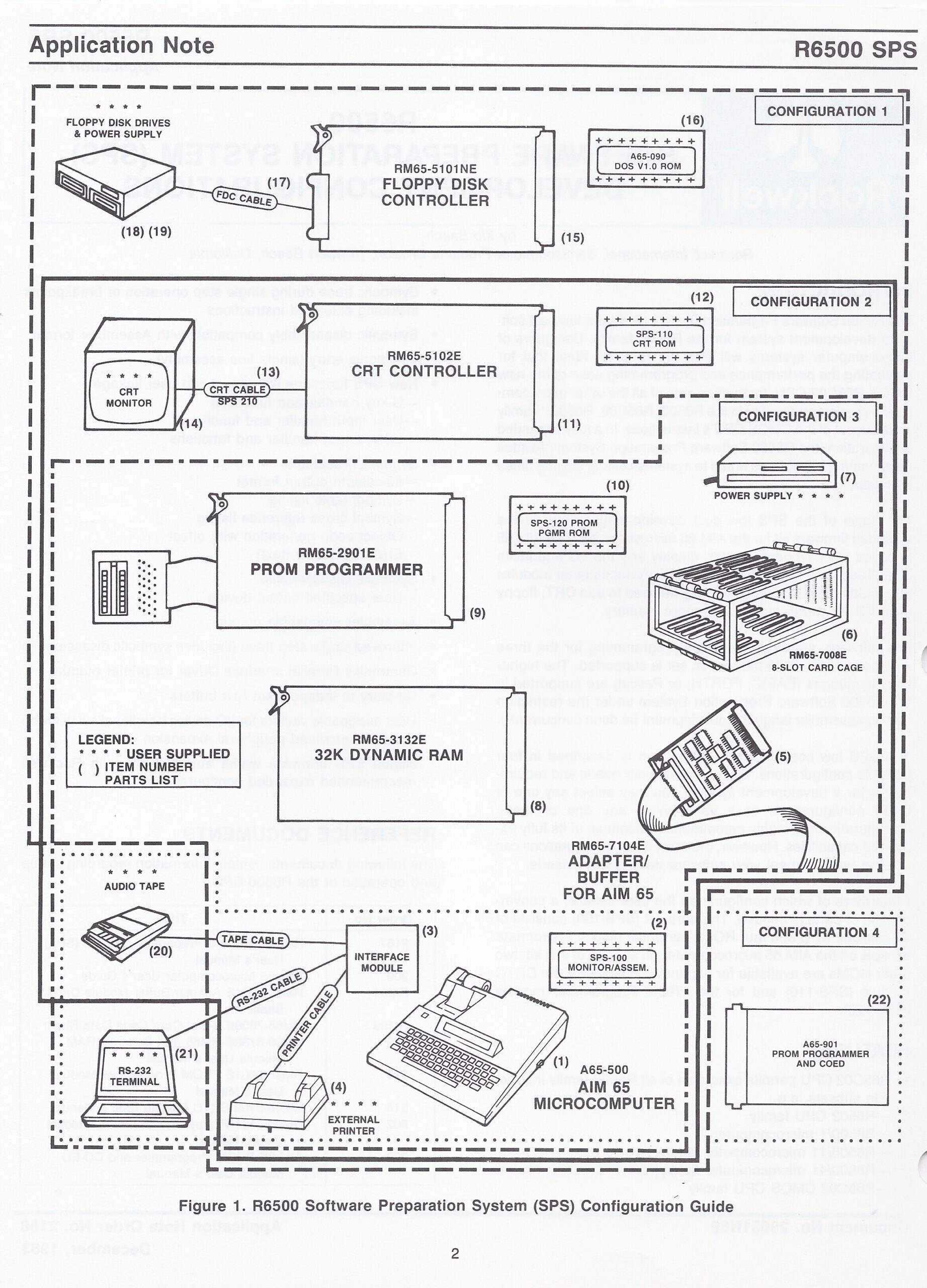

Software Preparation System Development

The R6500 Software Preparation System (SPS) is a low cost software development system for the R6500 family, for the 65C02 and 6502 and otehr 6500 family members.

The system can be used with a simple AIM 65 with cassette recorder and dump terminal, to floppy based systems with video display.

SPS and guide ROMs download:

|

Software Preparation System Development Configurations guide |

SPS DOS.BIN

Z22 SPS100 war im AIM.BIN

Z23 SPS100.BIN

Z25 SPS100.BIN

Z26 SPS100.BIN

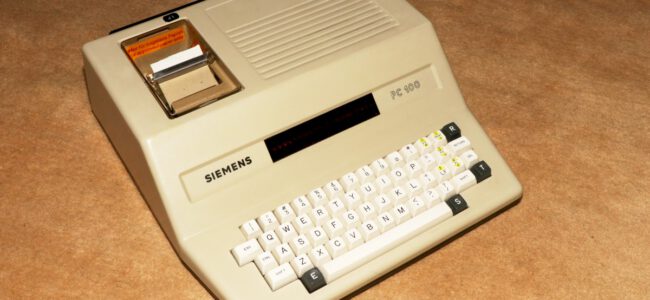

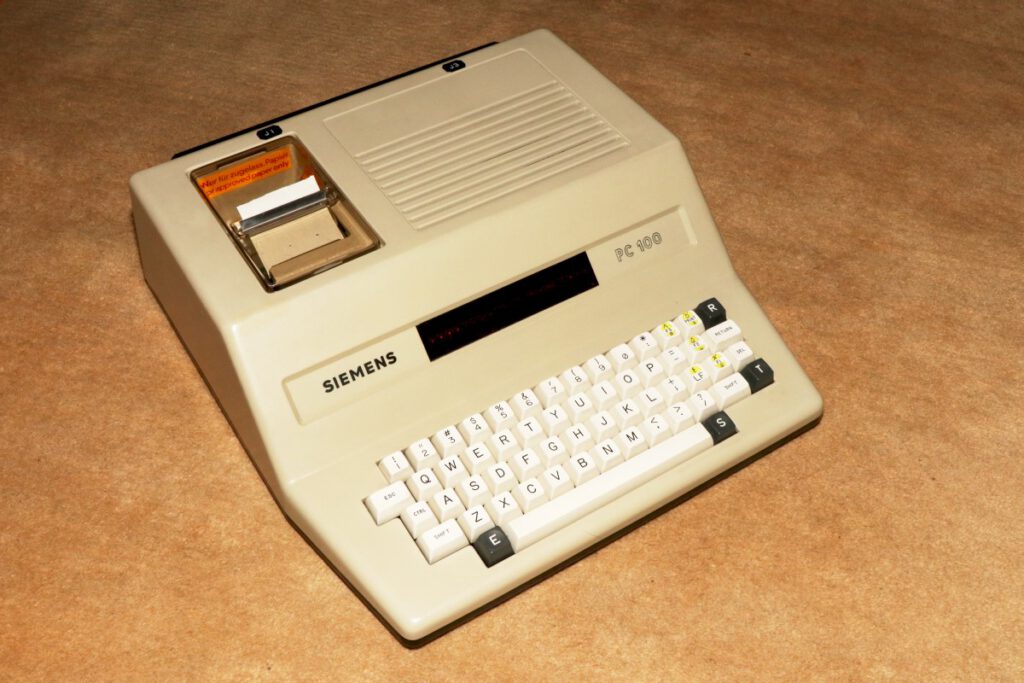

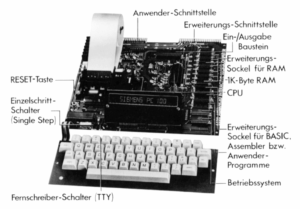

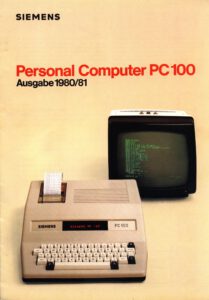

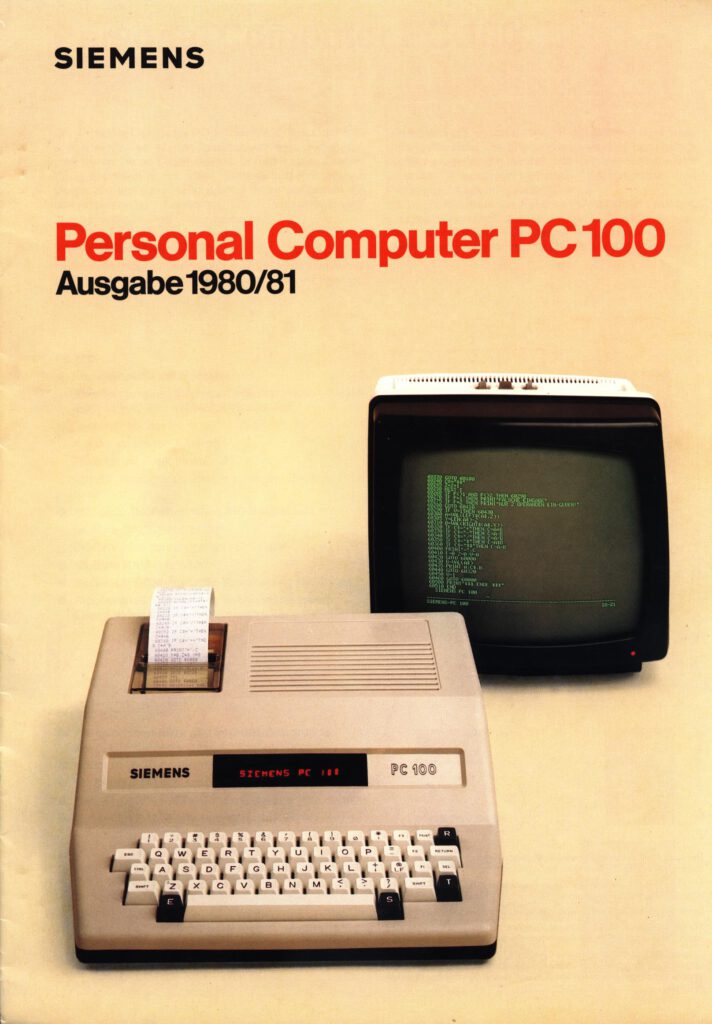

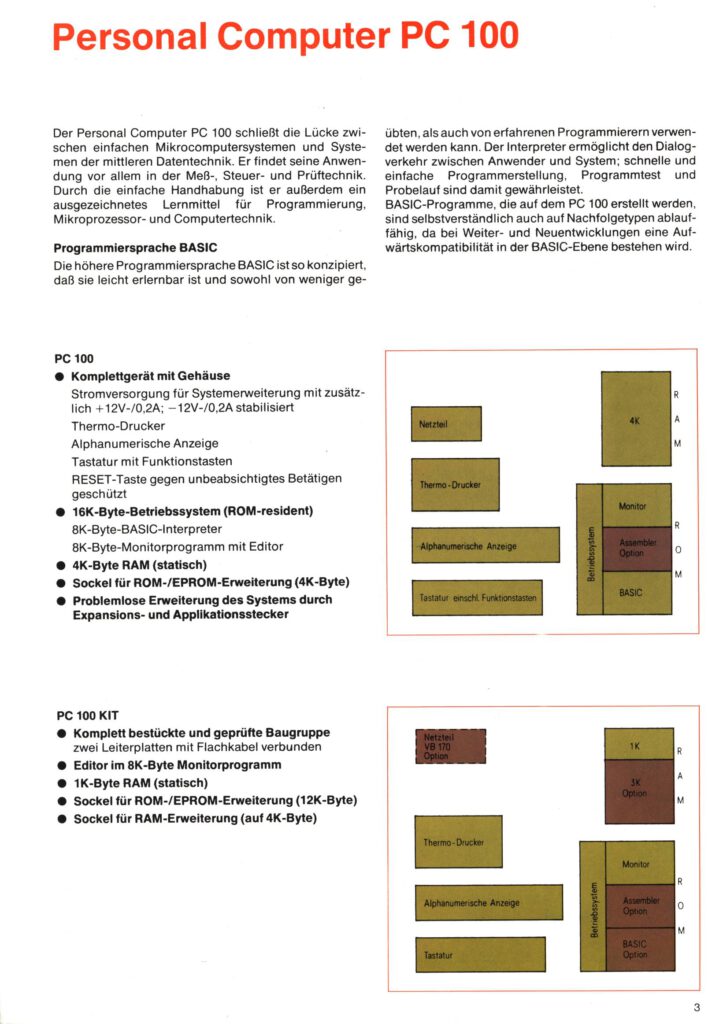

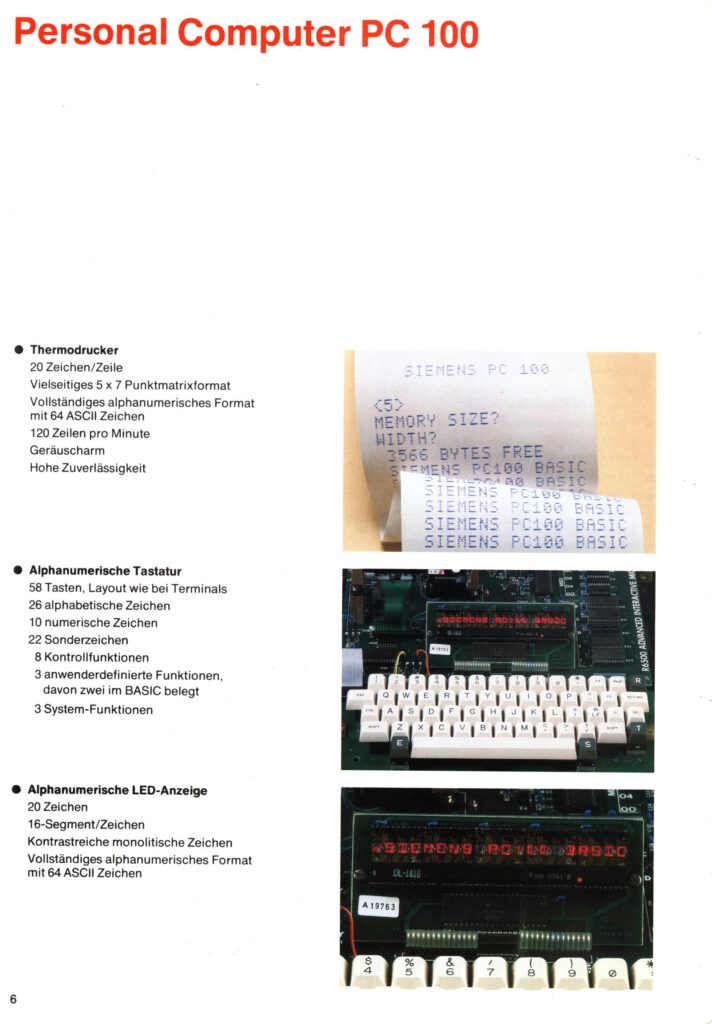

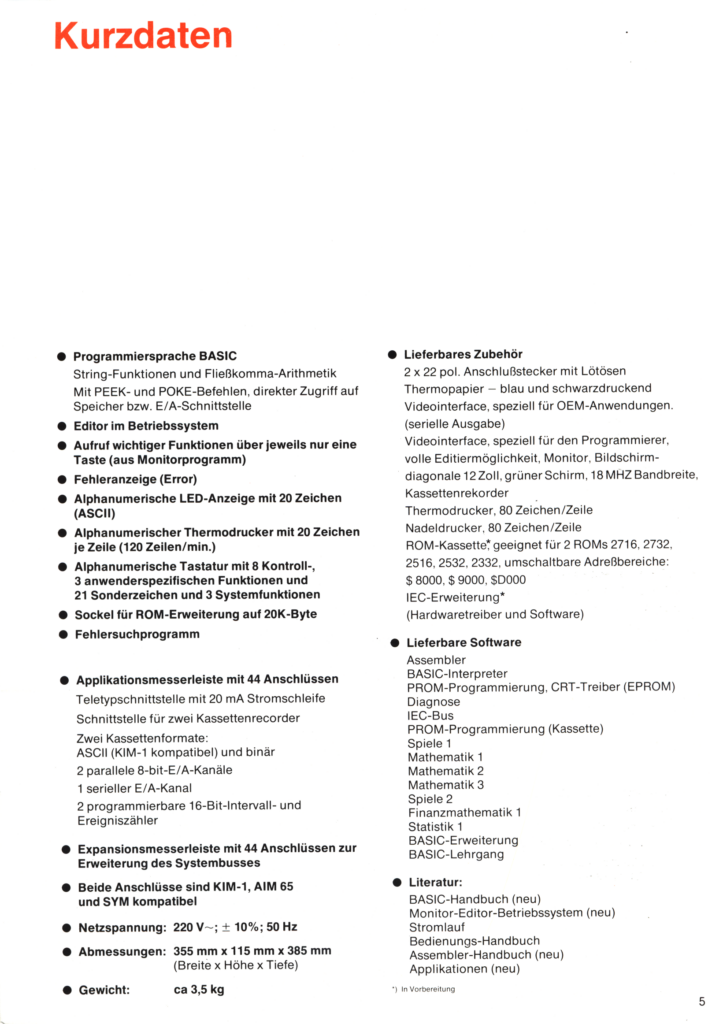

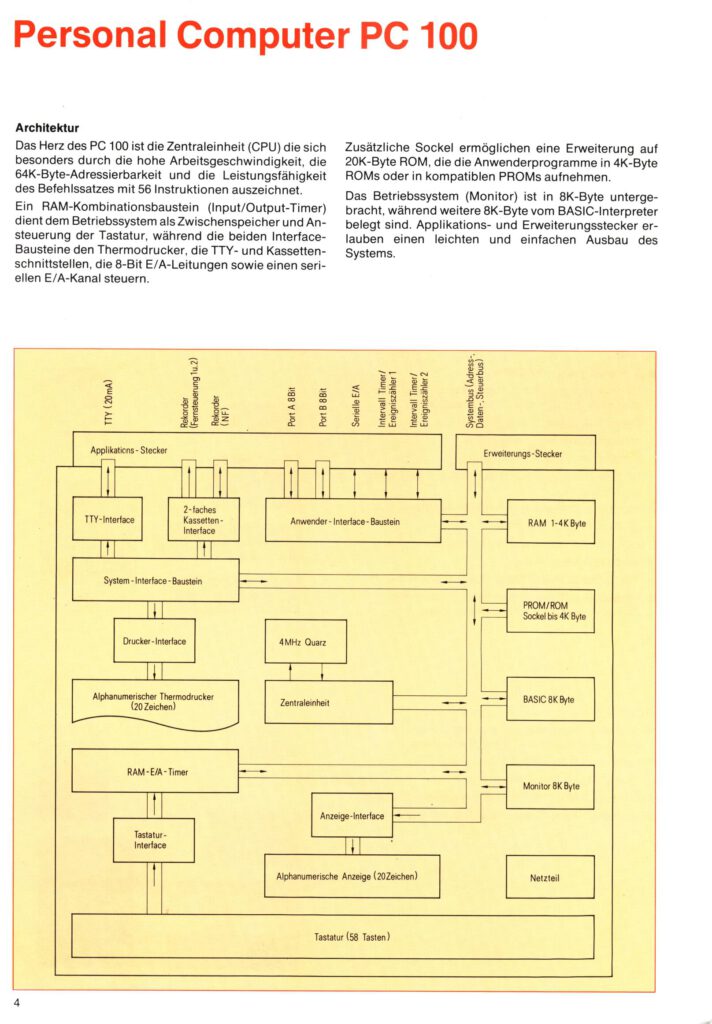

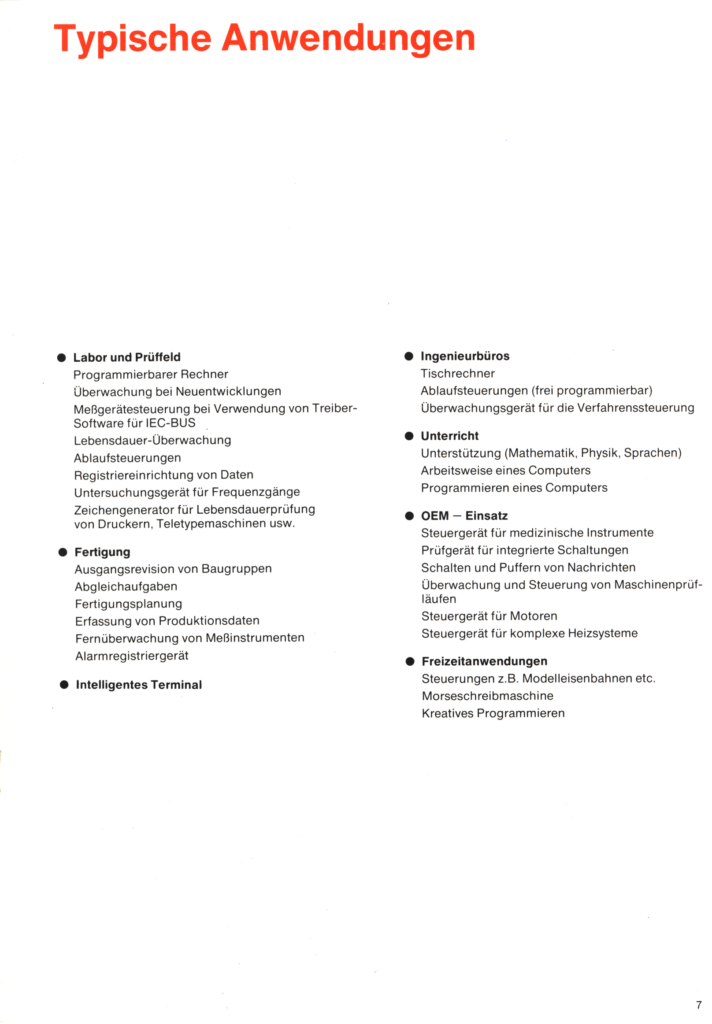

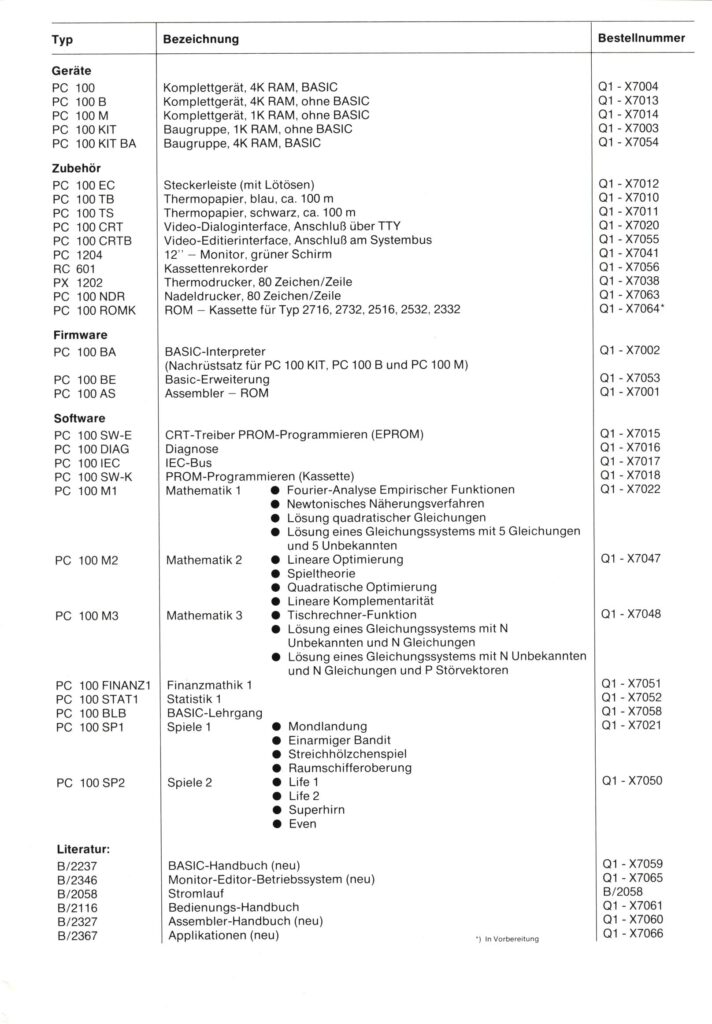

Siemens variant of Rockwell’s AIM 65. An AIM 65 in a Siemens case (with power supply) with German documentation and slightly modified ROMs

Downloads

(with thanks to the members of the German “VzEkC e.V” and Michael Steil)

|

Siemens Personal Computer PC 100 Bedienungsanleitung, Ausgabe 1981/1982 |

|

Applikationen zum Personal Computer PC100 Ausgabe 1980/81 |

|

Assembler Handbuch 1979/80 |

|

Assembler Handbuch 1980/81 |

|

Monitor-Editor-Betriebssystem |

|

PC100 Bedienungsanleitung 197/80 |

|

Personal Computer PC100 Ausgabe 1980/81 |

|

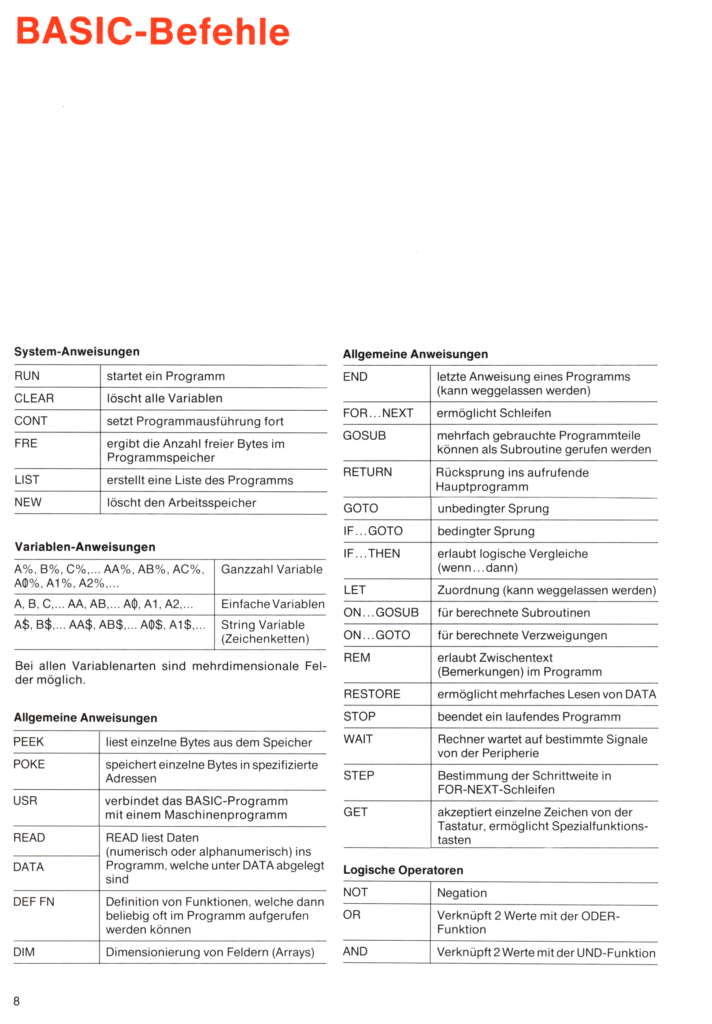

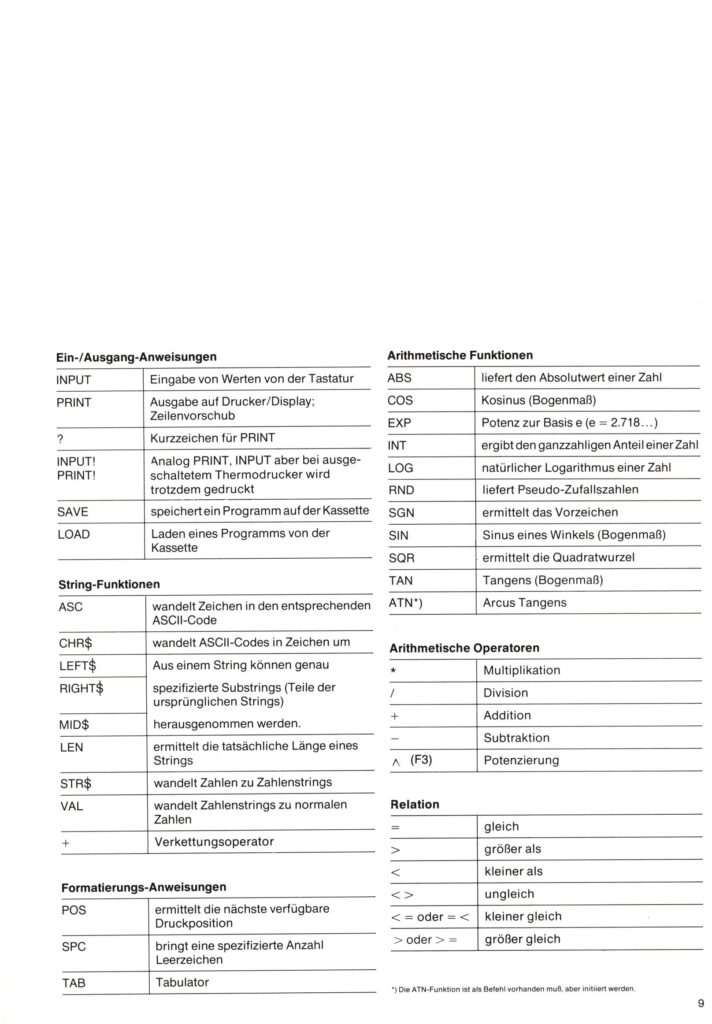

Basic Handbuch |

|

Basic Handbuch 1980/81 |

|

ROMs Extended Basic 2.1 by GWK |

|

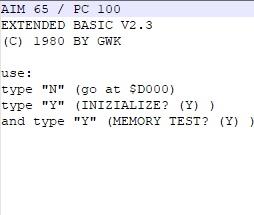

ROMs Extended Basic 2.3 by GWK AIM 65 / PC 100 EXTENDED BASIC V2.3 (C) 1980 BY GWK use: type “N” (go at $D000) type “Y” (INIZIALIZE? (Y) ) and type “Y” (MEMORY TEST? (Y) ) |

|

AIM65 Siemens PC100 BASIC ROMs |

|

GWK AIM 65 Development Aid (C) 1980 |

|

AIM BASIC MICROSOFT V1.1 B C D zusatz |

The last number in the ROM file is the location of the ROM in the board, see photo.

I have added Superjolt manuals and schematics to the Jolt pages

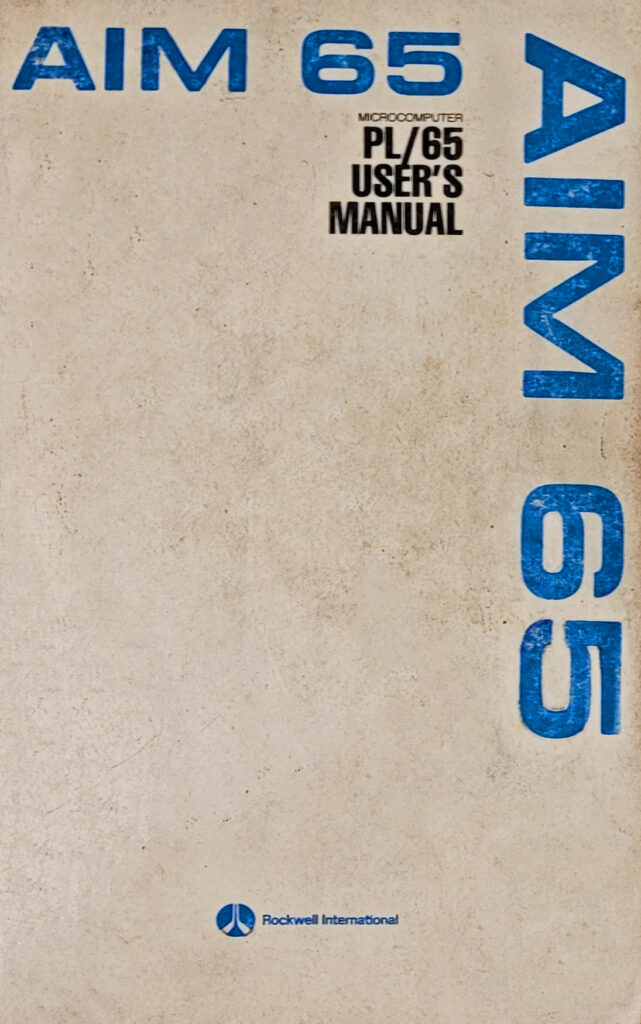

PL/65 Manual in PDF format

PL/65 Manual in text format

PL/65 disassembly, no comments

PL/65 V1.0 ROM 1

PL/65 V1.0 ROM 2

The last number in the ROM file is the location of the ROM in the board, see photo.

AIM 65 Forth Manual for the AIM65, V1.3, complete manual

AIM 65 Forth V1.4 Manual for the AIM 65/40, after chapter 2 is this manual also applicable also to AIM 65

Compact A65-050 AIM Forth ROMS description of all Forth words

First Forth ROM V1.3 AIM 65-050

Second Forth ROM AIM 65-050

Basic Language Reference manual in PDF format

Basic Language Reference manual in PDF format

Basic Language Reference manual in text format

First Basic ROM R3225-11

Second Basic ROM R3226-11 part R32J1-11

See Create your own Version of Microsoft BASIC for 6502 and Microsoft BASIC for 6502 for a commented assembler source for AIM 65 Basic.

AIM BASIC MICROSOFT V1.1 B C D extension (D000 ROM)