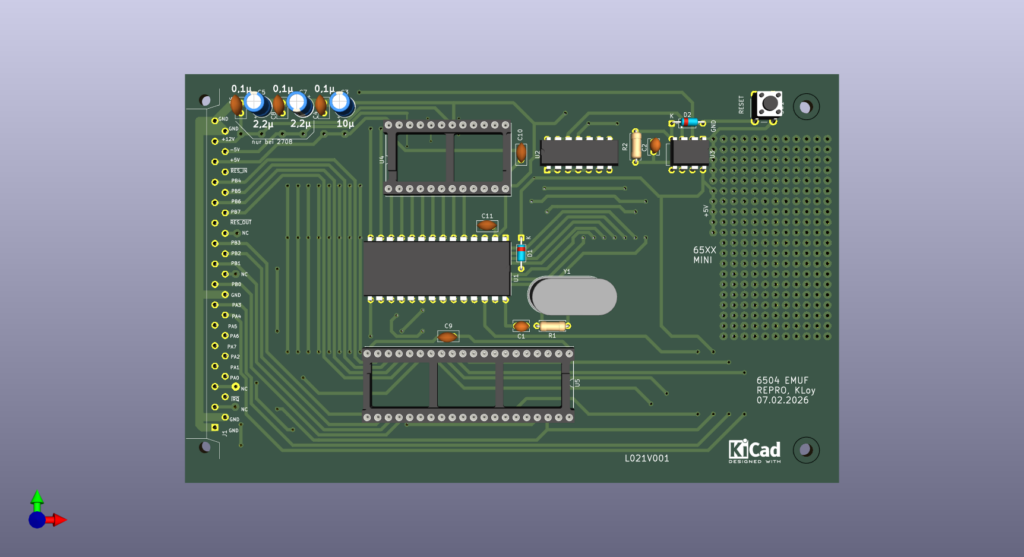

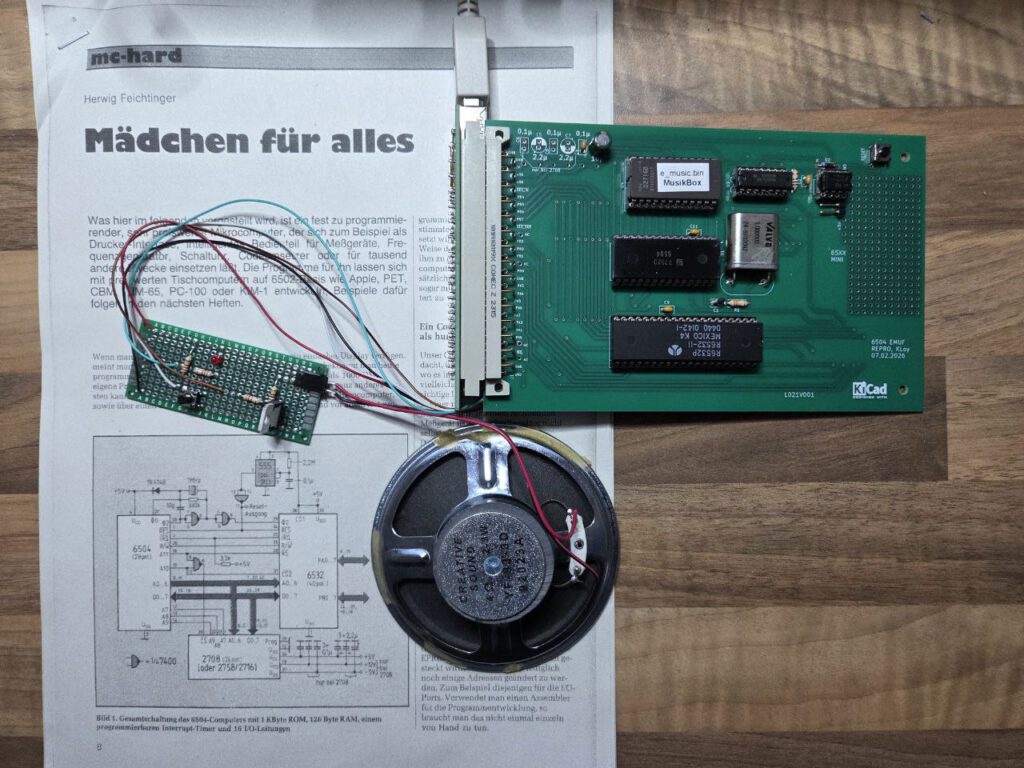

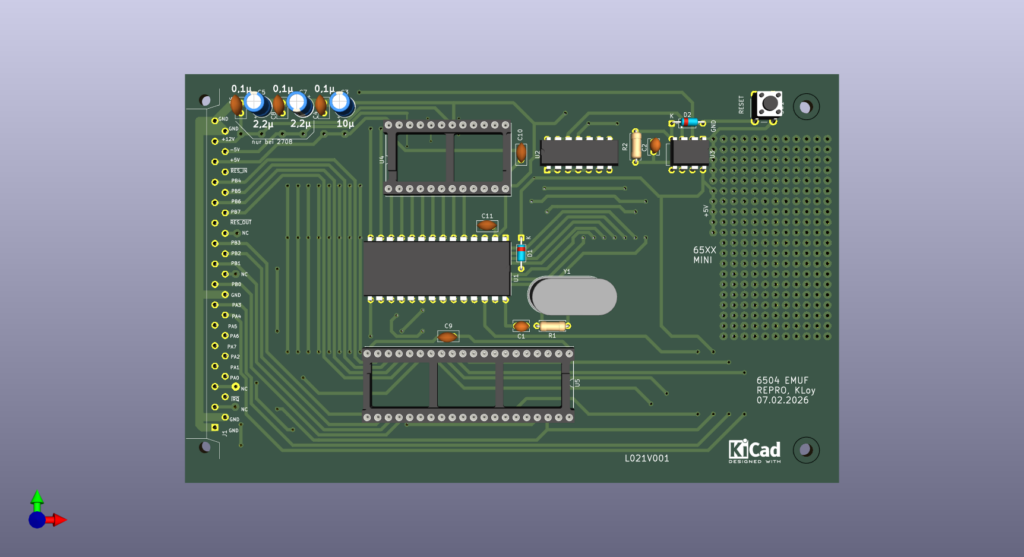

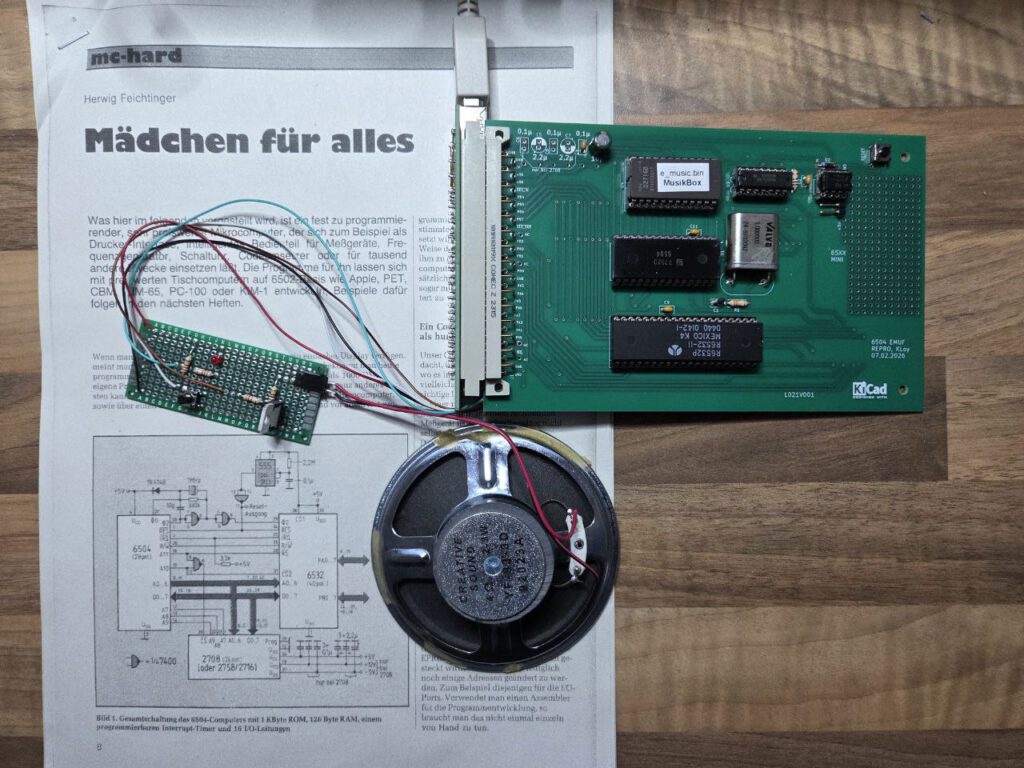

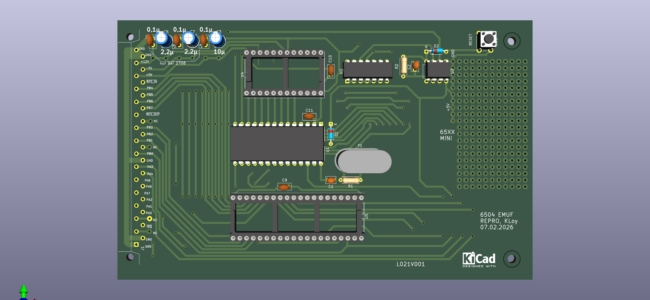

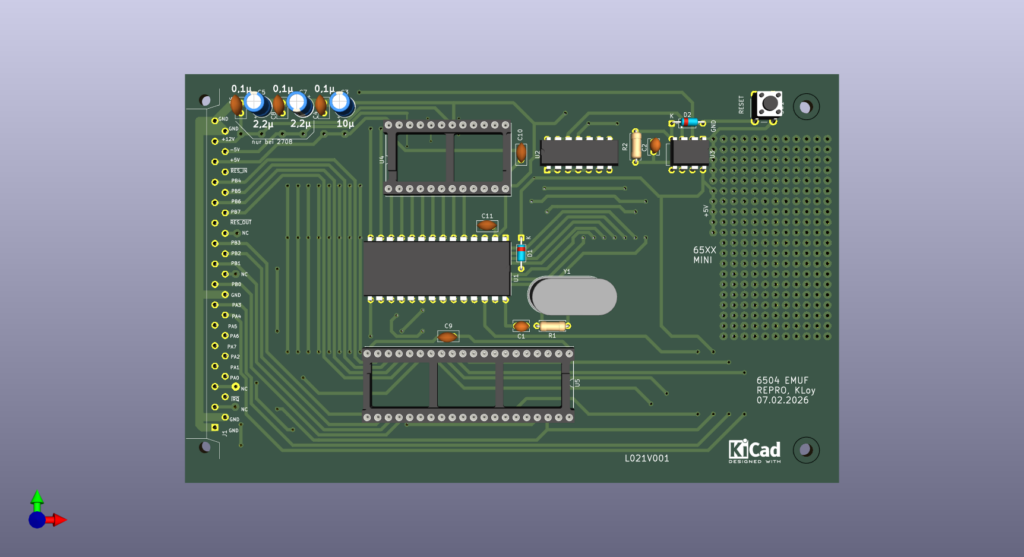

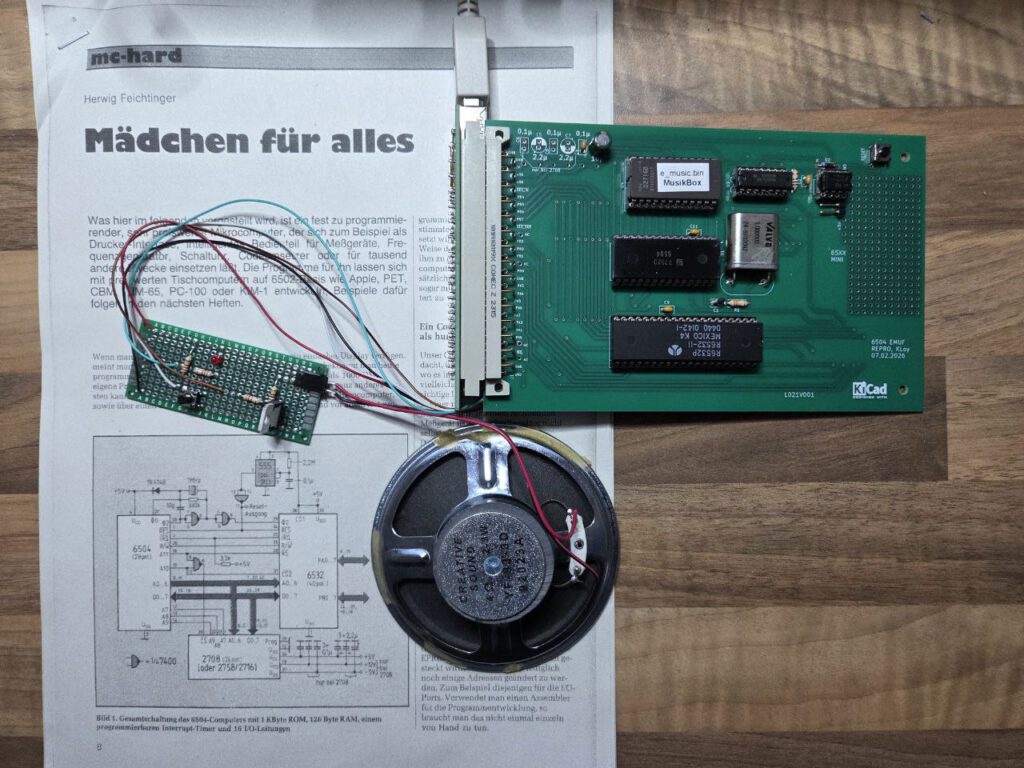

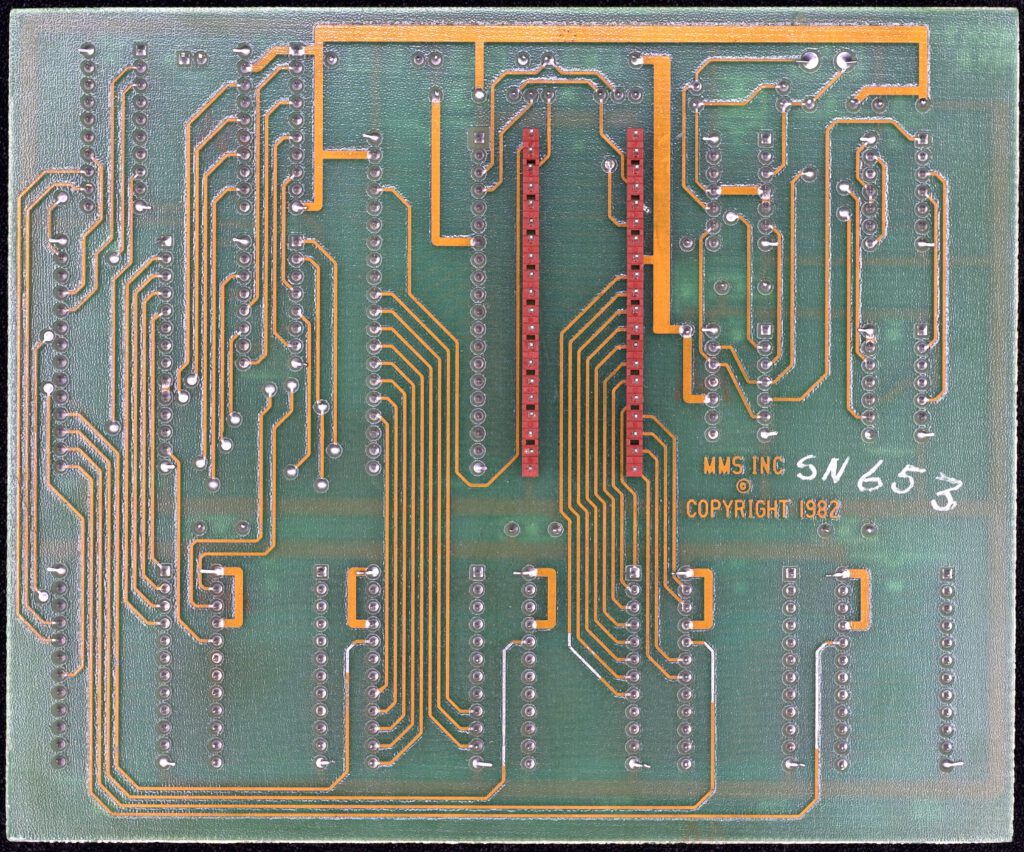

A remake by Klaus Loy of the 6504 based EMUF 6504 as published in MC, see for the many original articles about the EMUF SBCs.

Here the announcement.

Here a local copy of the work by Klaus.

See his github archive for the original.

About small SBC systems

A remake by Klaus Loy of the 6504 based EMUF 6504 as published in MC, see for the many original articles about the EMUF SBCs.

Here the announcement.

Here a local copy of the work by Klaus.

See his github archive for the original.

A remake by Klaus Loy of the 6504 based EMUF 6504 as published in MC, see the many original articles about the EMUF.

Here the announcement.

Here a local copy of the work by Klaus.

See his github archive for the original.

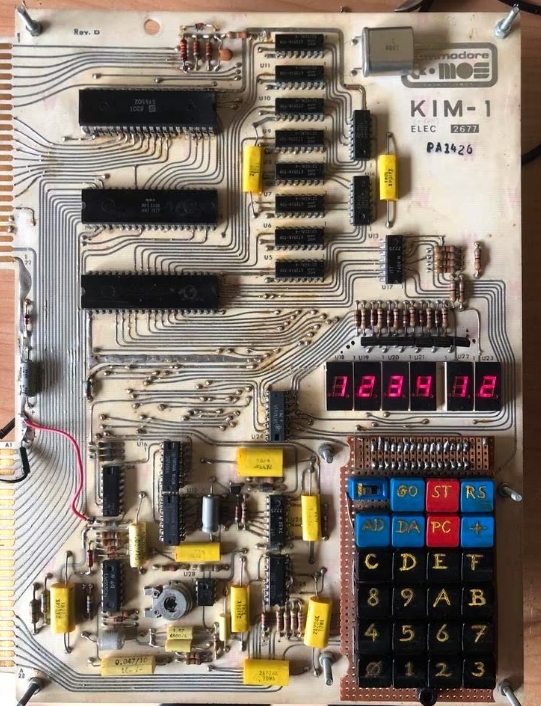

New project, cleanup and restore this KIM-1 . Poor thing still works but had a rough life. KIM-1 collection complete now, this one was the one I was waiting for.

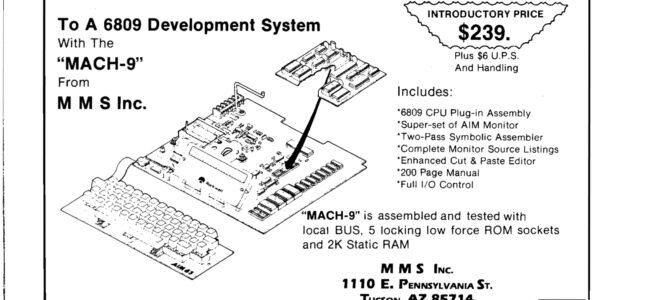

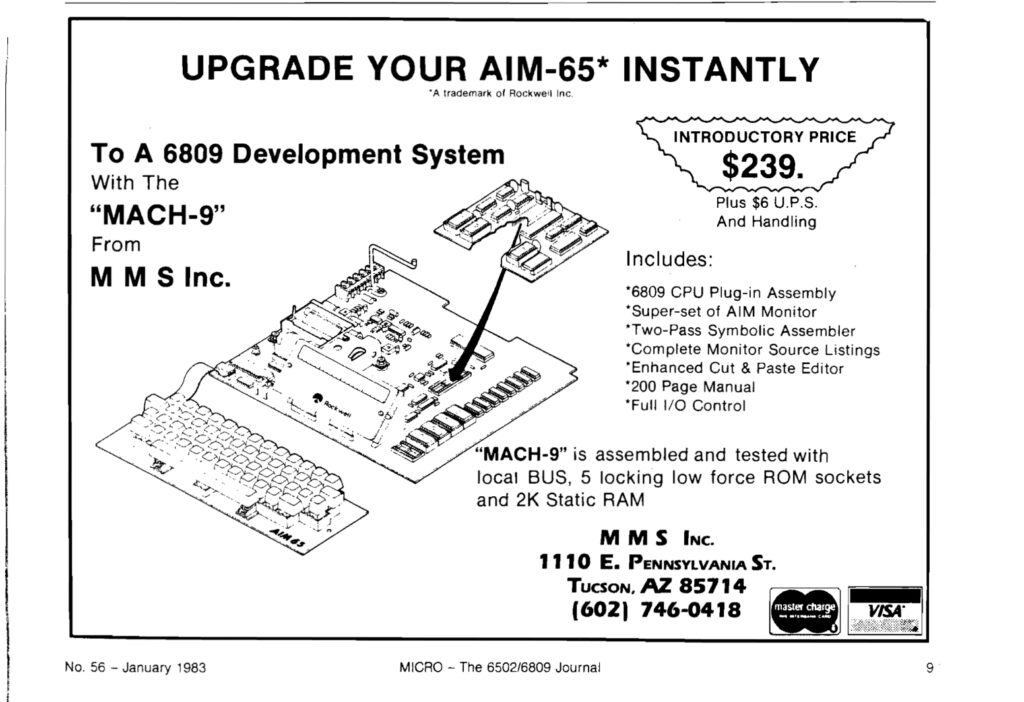

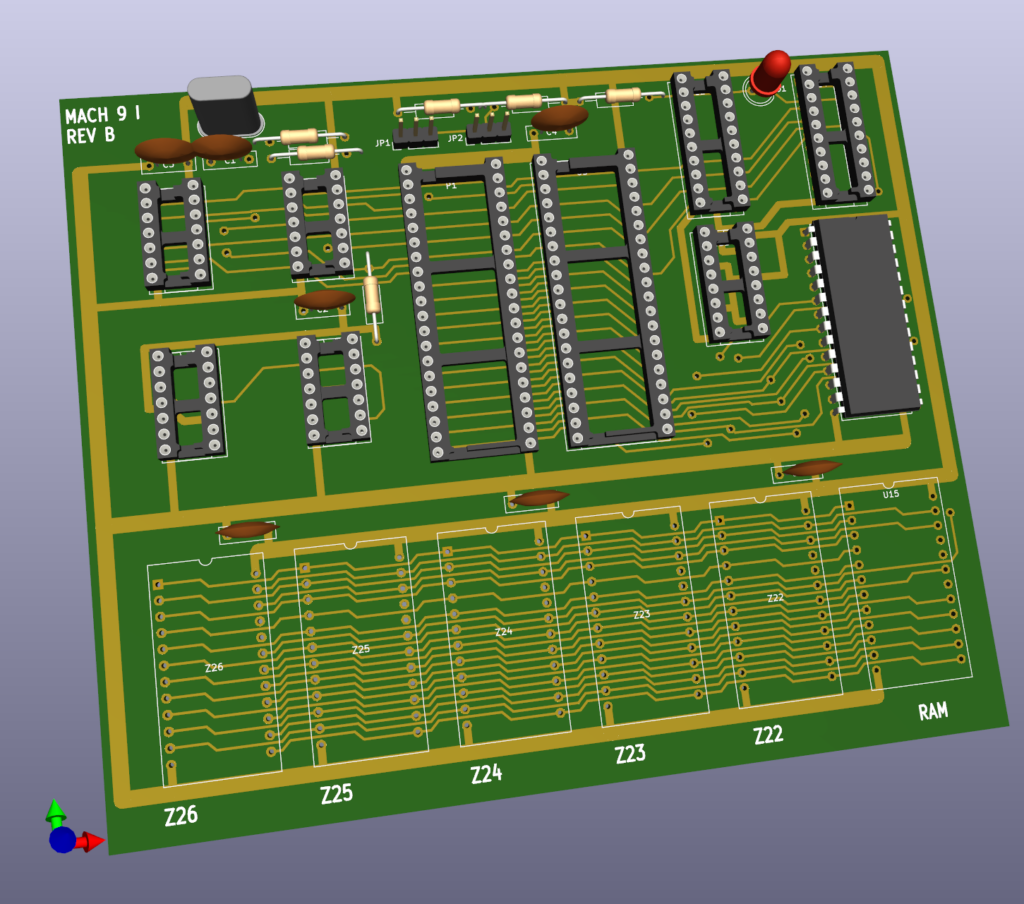

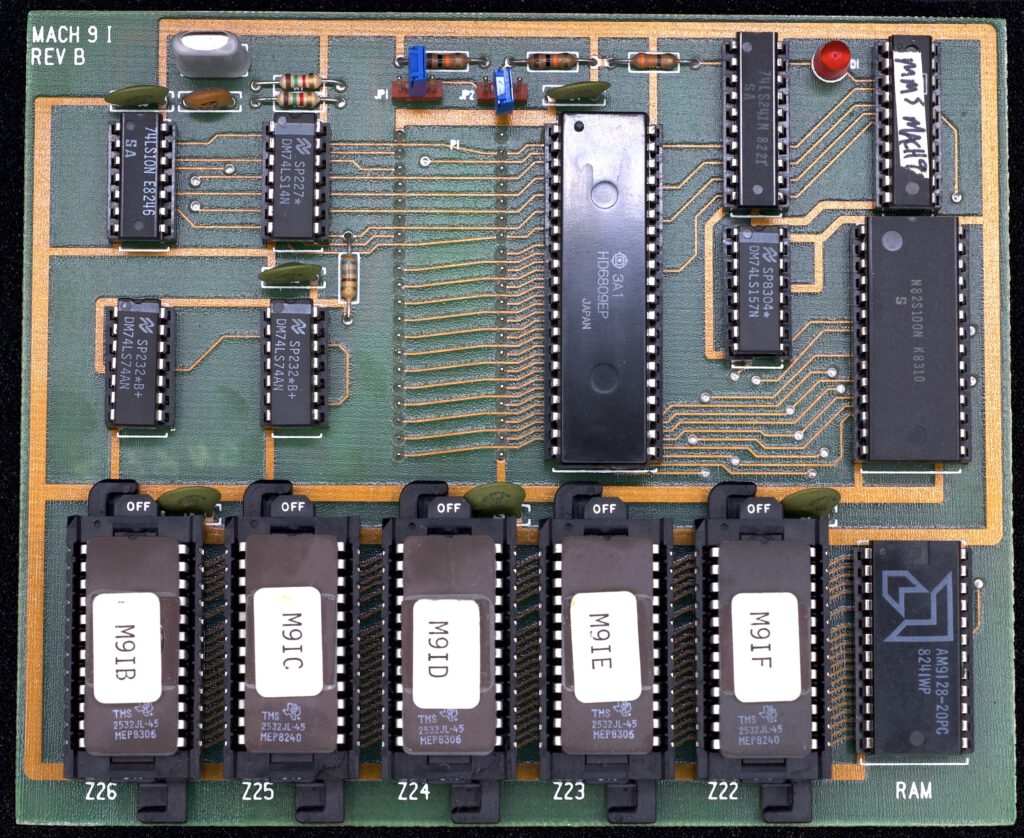

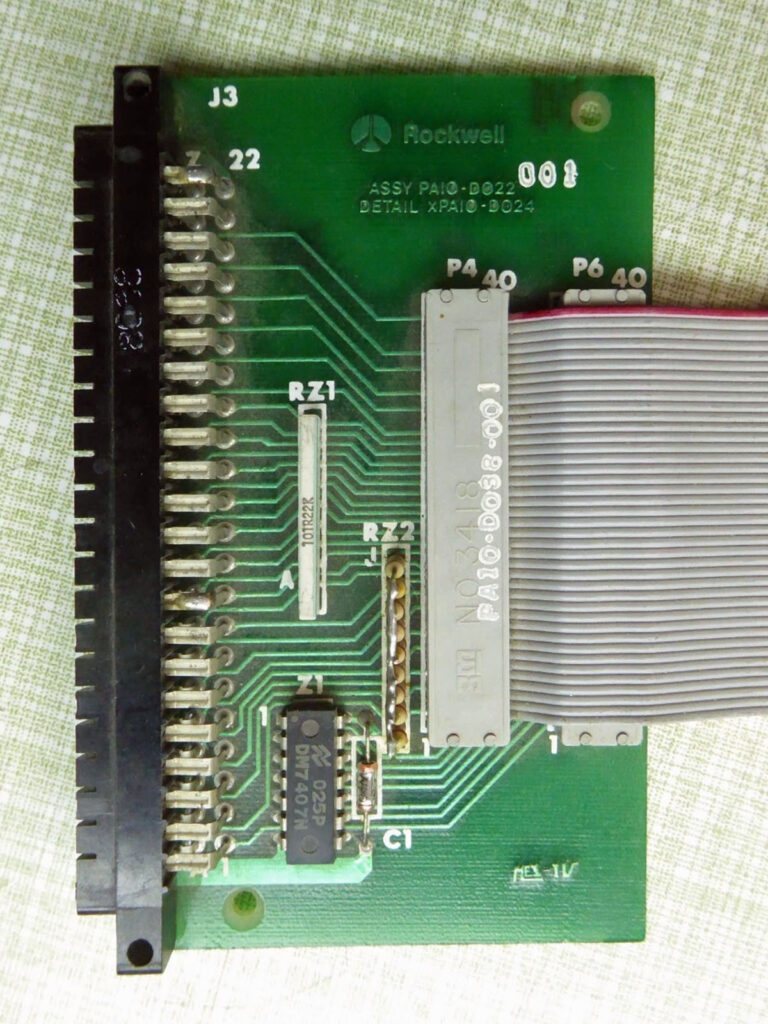

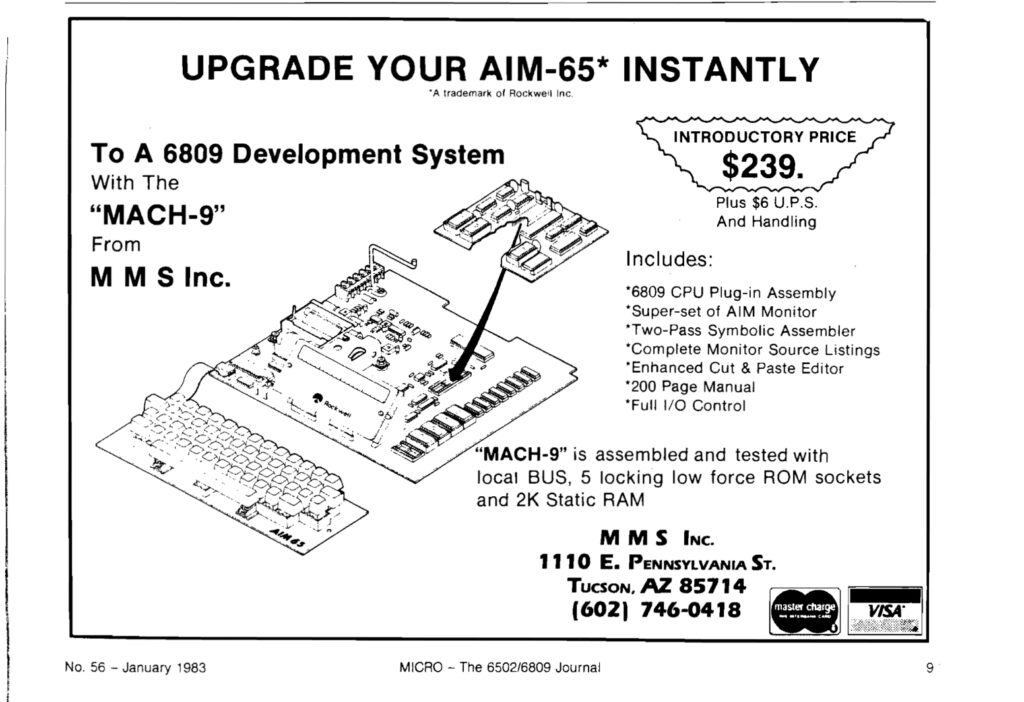

Royce Taft has a MACH-9 MMS Inc 6809 CPU Plug-in for AIM 65 and reverse engineered it.

He sent me his design to be published here.

Downloads

|

Here the archive with circuit diagram, ROMs and design files for the 82S100 PROM and PAL10L8 |

|

The Kicad Design files for the MACH-9 PCB |

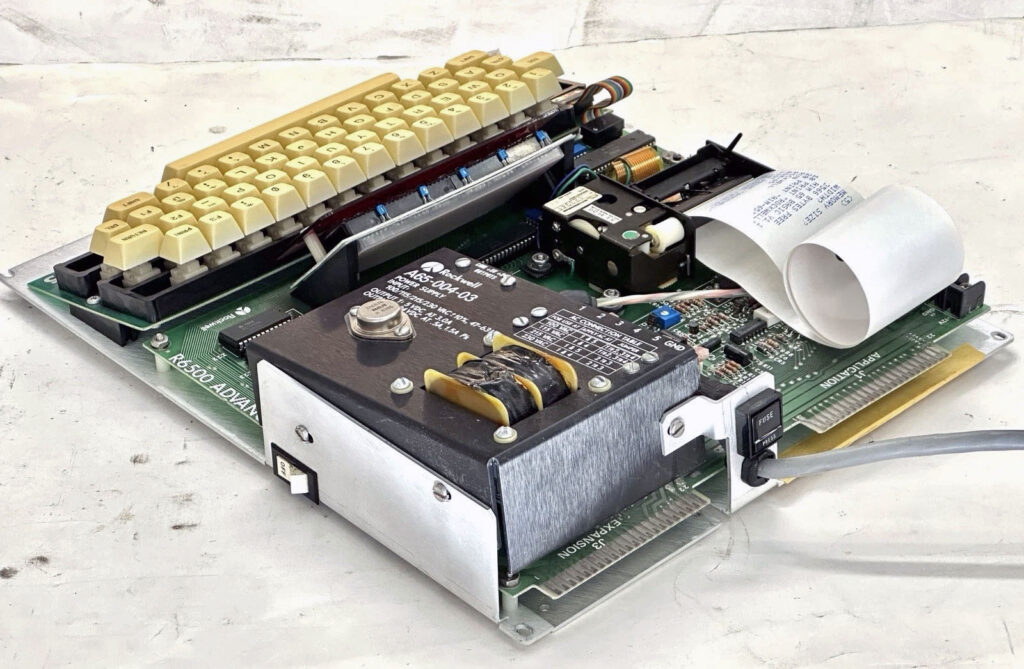

A65-004-03 Power Supply

Input 110/115/215/230 V AC n47-63 Hz

Output 1 : 5V DC 3.0A

Output 2 : 24 V DC .5A, 1.5A Peak

AIM 65 to RM 65 hardware interface

Royce Taft has a MACH-9 MMS Inc 6809 CPU Plug-in for AIM 65 and reverse engineered it.

He sent me his design to be published here.

Thanks to Eduardo Casino version 1.6.0 is also available on macOS.

1. Unzip the file

2. Move the KIM1SIM app to Applications

3. Remove quarantine:

$ attr -dr com.apple.quarantine /Applications/KIM1SIM.app

Rev D

PLEASE is a very small package for a standard KIM-1. It has a tiny monitor, command interpreter and many handy subroutines.

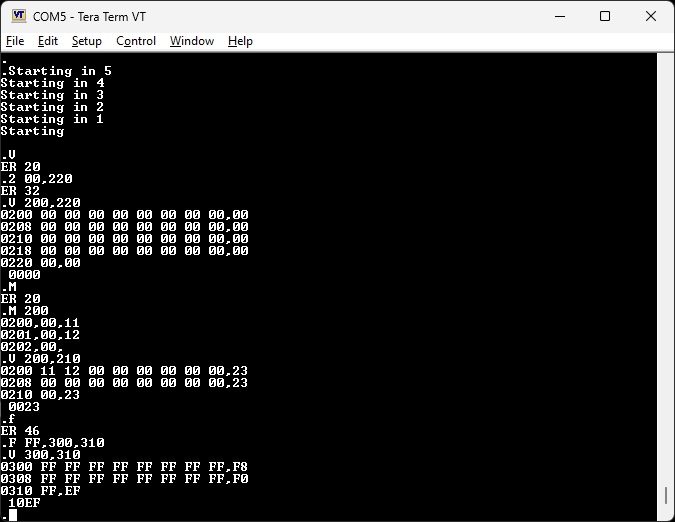

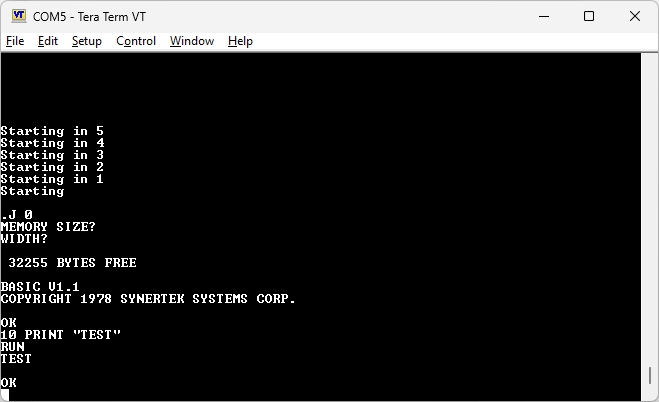

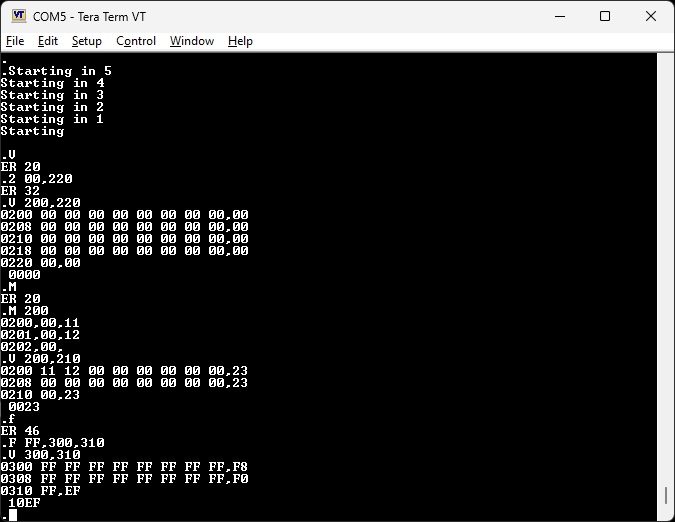

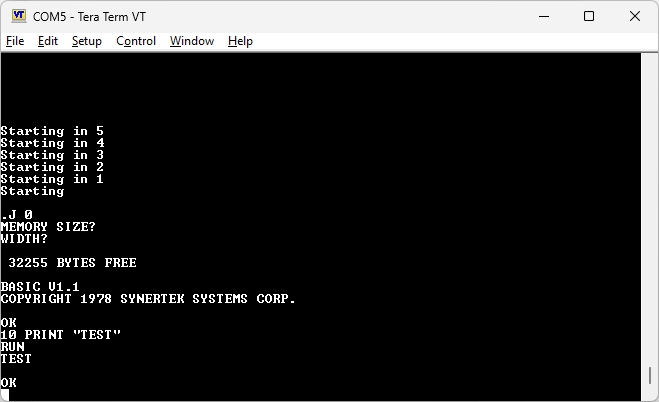

Emulation of a Synertek Sym-1 on a Raspberry Pi Pico 1 (W).

By andysa on the emulation forum on 6502.org

Here is the archive with source, documentation and the binary .uf2 file ready to run on a Pico,

It is based on Jonathans Fouvers “pico-6502 emulator” and “Fake6502”.

You will need this archive to compile the source of PicoSYM.

picoSYM Memory Map

PicoSYM emulates a SYM-1 with the Supermon V1.1 Monitor, Basic, RAE Assembler & Editor and 1541DOS at the typical addresses. The 1541DOS implementation uses “Port A” of an emulated VIA to connect to SD2IEC style floppy disk emulator modules. It has been tested with reasonable success with both the UIEC-SD and pi1541.

These SD2IEC type modules need to be connected to the RPi Pico GPIO ports via a suitable 3.3v/5v level converter and 7416 open collector inverter. (Refer SYM-1 1541 DOS manual and connection diagram within the ZIP file or the 1541 DOS page here)

The 1541DOS relies heavily on the VIA Timers, which required much experimentation with the emulator code in order to get operational. As such, the reliability has not been fully confirmed, however Loading, Saving of files and directory listings does appear to be functional and repeatable at this stage.

The only noticeable bug is with the Directory Listing reporting of “Blocks Free”, which contains erroneous characters. This is due to the 1541DOS simplistic decoding of the received IEC filesize data. This worked fine back in the day given the 170KB storage capacity of a floppy disk.

With the larger capacity of modern SD cards however, the reported free block size is larger than what the 1541DOS routines can accommodate. Partitioning SD cards to a smaller capacity should get around this problem in the short term, however andysa is in the process of patching the necessary subroutines in 1541DOS.

Usage

——-

To use the emulator, put the Raspberry Pi Pico in bootloader mode, by holding the ‘BootSel’ button while connecting it to a computer.

The Pico will appear as a drive. Drop the UF2 file to it.

Open a comms utility such as Putty, at 115200 baud (or use 2400 for a real SYM-1 experience!).

Emulation of a Synertek Sym-1 on a Raspberry Pi Pico 1 (W).

By andysa on the emulation forum on 6502.org

Here is the archive with source, documentation and the binary .uf2 file ready to run on a Pico,

It is based on Jonathans Fouvers “pico-6502 emulator” and “Fake6502”.

You will need this archive to compile the source of PicoSYM.

picoSYM Memory Map

PicoSYM emulates a SYM-1 with the Supermon V1.1 Monitor, Basic, RAE Assembler & Editor and 1541DOS at the typical addresses. The 1541DOS implementation uses “Port A” of an emulated VIA to connect to SD2IEC style floppy disk emulator modules. It has been tested with reasonable success with both the UIEC-SD and pi1541.

These SD2IEC type modules need to be connected to the RPi Pico GPIO ports via a suitable 3.3v/5v level converter and 7416 open collector inverter. (Refer SYM-1 1541 DOS manual and connection diagram within the ZIP file or the 1541 DOS page here)

The 1541DOS relies heavily on the VIA Timers, which required much experimentation with the emulator code in order to get operational. As such, the reliability has not been fully confirmed, however Loading, Saving of files and directory listings does appear to be functional and repeatable at this stage.

The only noticeable bug is with the Directory Listing reporting of “Blocks Free”, which contains erroneous characters. This is due to the 1541DOS simplistic decoding of the received IEC filesize data. This worked fine back in the day given the 170KB storage capacity of a floppy disk.

With the larger capacity of modern SD cards however, the reported free block size is larger than what the 1541DOS routines can accommodate. Partitioning SD cards to a smaller capacity should get around this problem in the short term, however andysa is in the process of patching the necessary subroutines in 1541DOS.

Usage

——-

To use the emulator, put the Raspberry Pi Pico in bootloader mode, by holding the ‘BootSel’ button while connecting it to a computer.

The Pico will appear as a drive. Drop the UF2 file to it.

Open a comms utility such as Putty, at 115200 baud (or use 2400 for a real SYM-1 experience!).

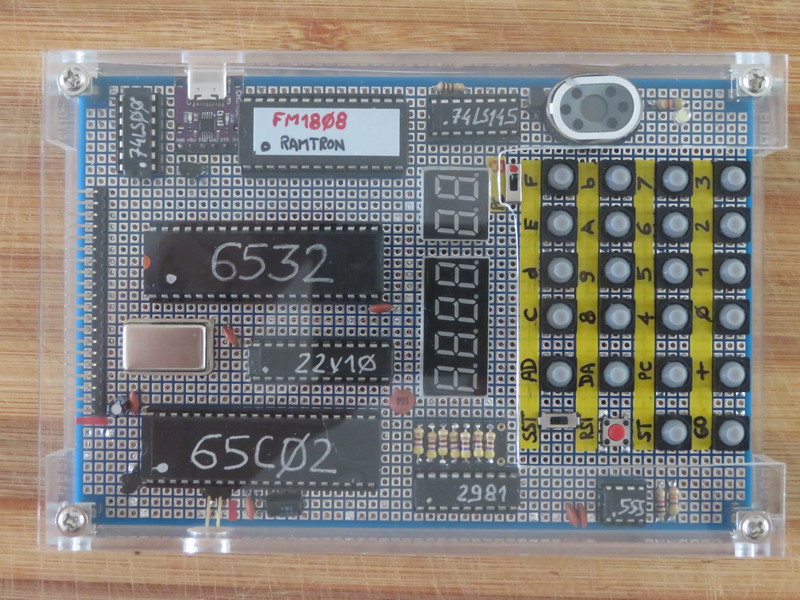

Small enough to take with you traveling, battery powered and thanks to the FRAM the contents of RAM are kept when powered off.

The FM1808 used is a non-volatile RAM (32Kx8), used here for ROM and RAM. Datasheet here.

This design appeared in the Google group devoted to the PAL-1 and PAL-1 (and the KIM-1 of course). The design is by Voyageur.

Read all about the KIM1Mod here.