I have acquired 3! Superjolts. With a Synertek Superjolt CP110 manual and Tiny Basic + RAP (assembler) in ROM.

A good opportunity to update the 6530 and the Jolt SuperJolt pages. Better quality and more documents, more photos, ROMs dumped.

About small SBC systems

I have acquired 3! Superjolts. With a Synertek Superjolt CP110 manual and Tiny Basic + RAP (assembler) in ROM.

A good opportunity to update the 6530 and the Jolt SuperJolt pages. Better quality and more documents, more photos, ROMs dumped.

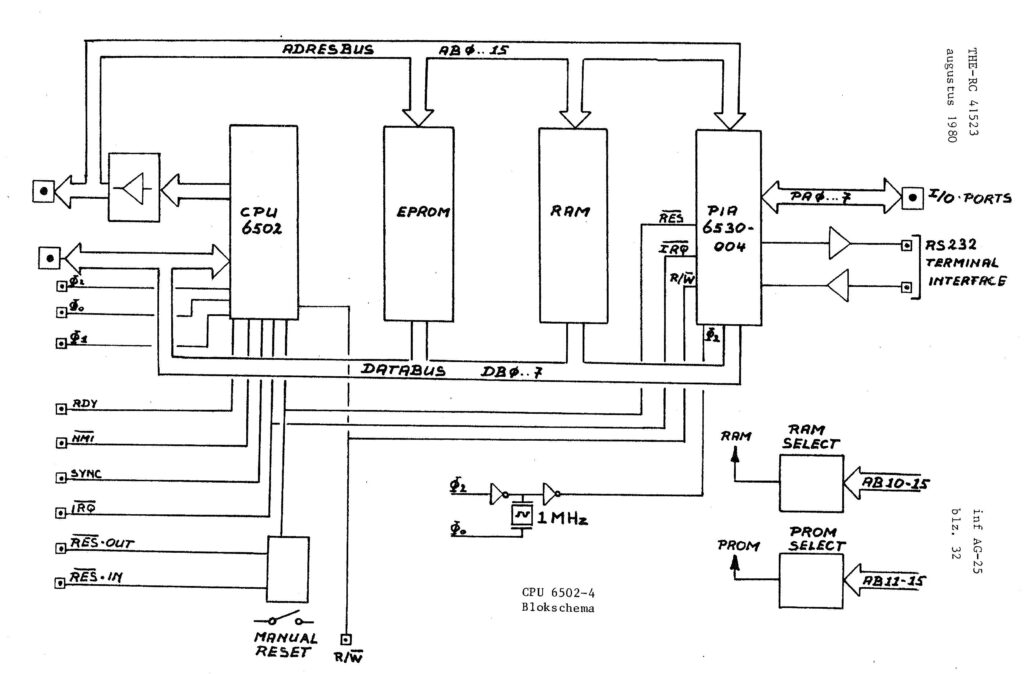

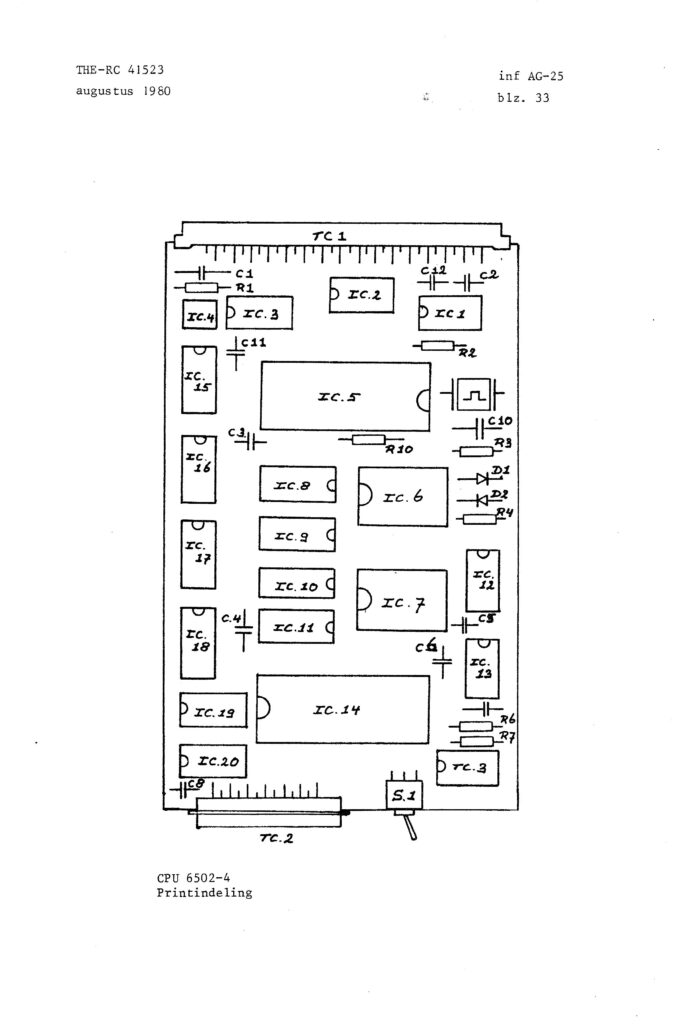

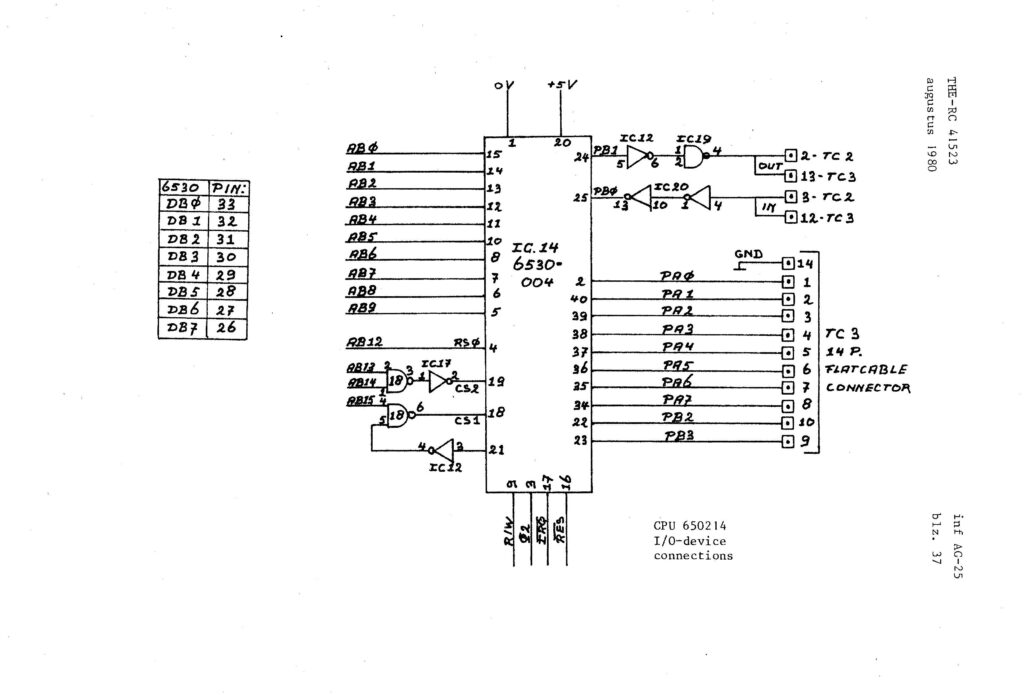

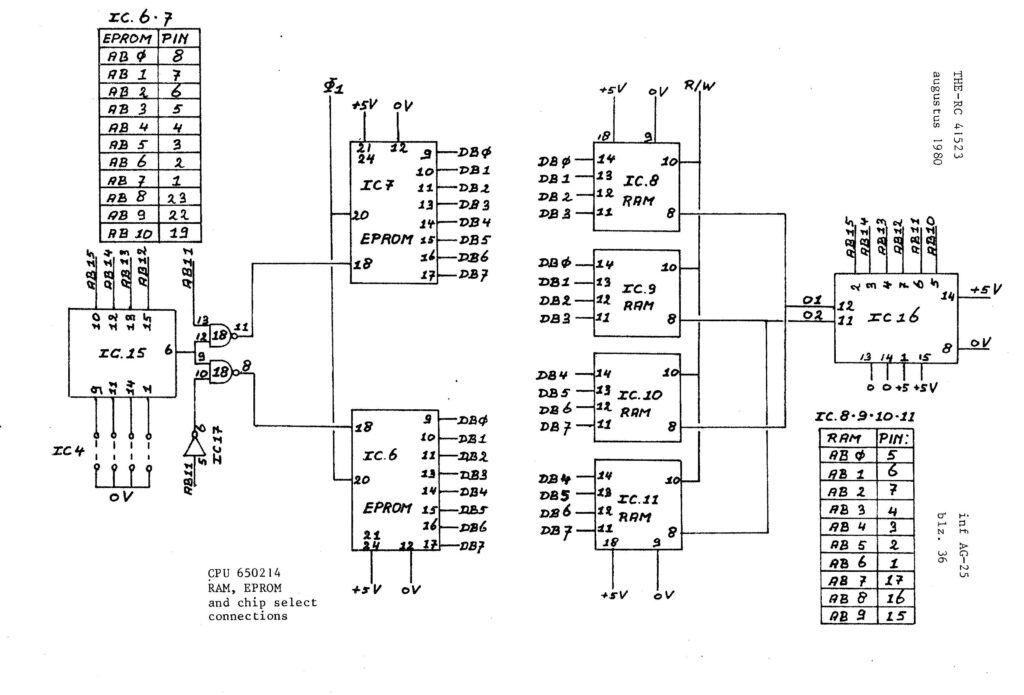

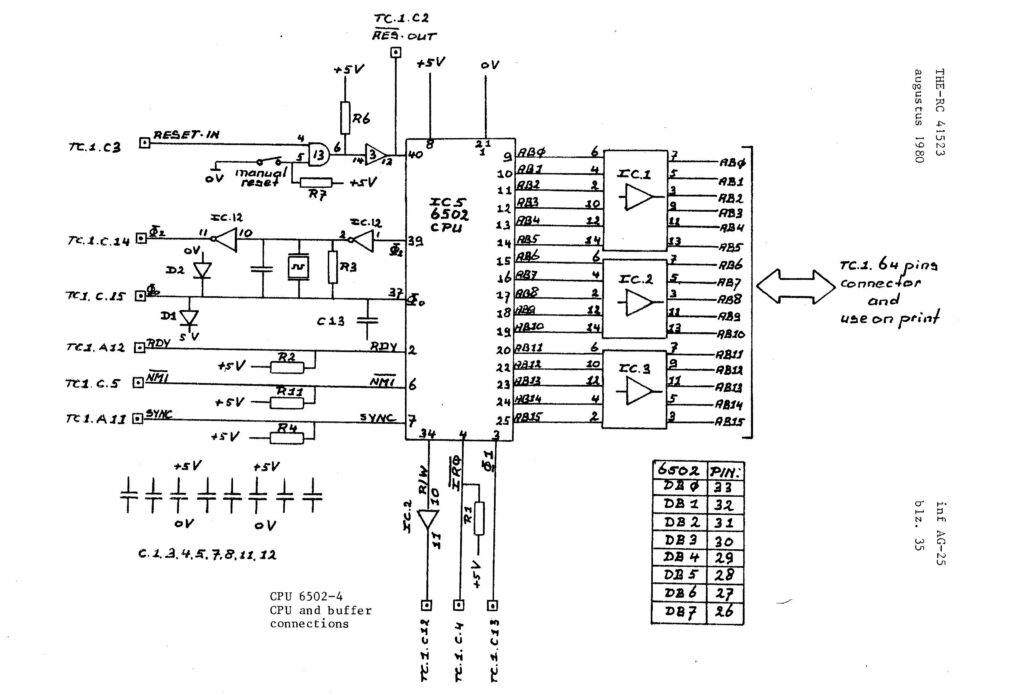

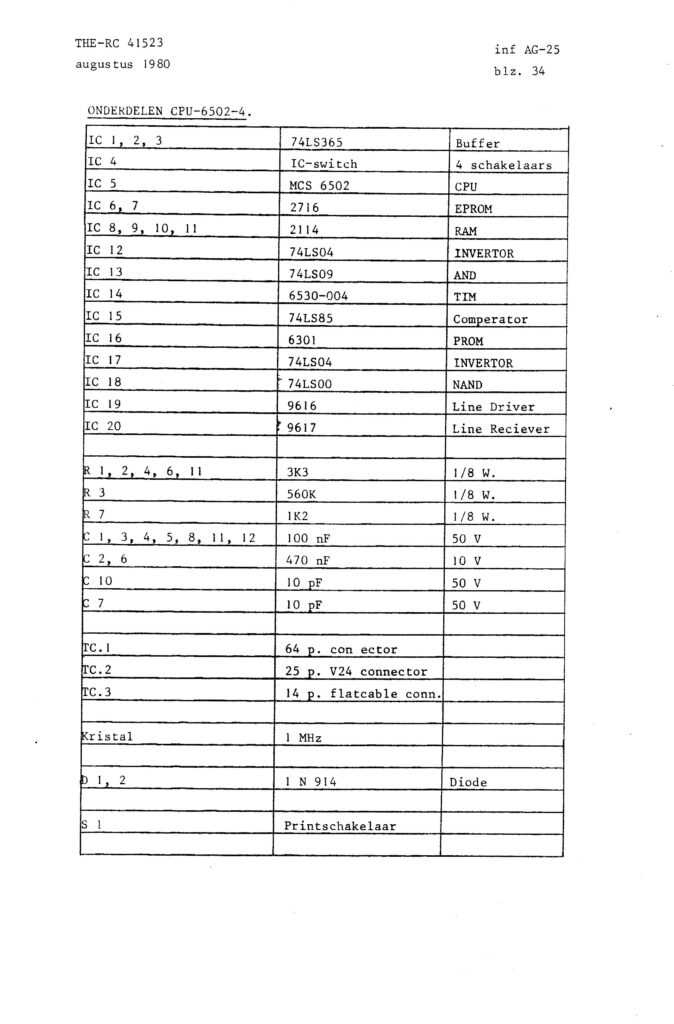

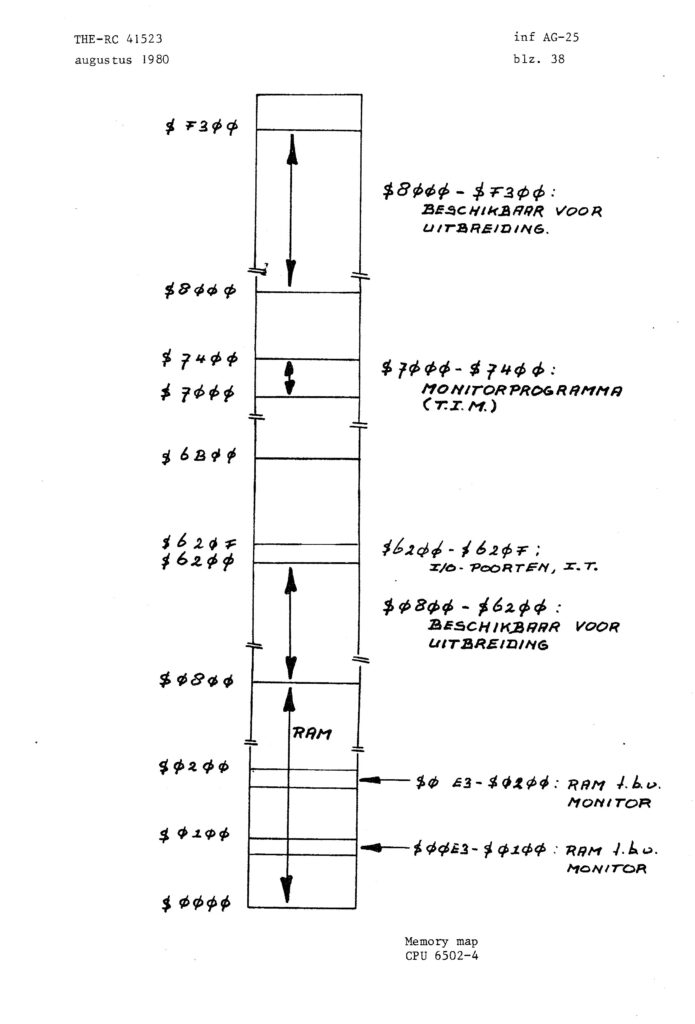

CPU-4 is a 6502 SBC based upon the TIM 6530-004. Developed for teaching on the Technical University Eindhoven.

The only surviving part of the system is a 40 page Dutch manual.

Described are the function of TIM, Tiny Basic and Resident Assembler Program, same as the Jolt and Superjolt.

|

Dutch manual of RC41523 CPU-4 |

Some excerpts from the manual:

6530-002 ROM at $1C00 dump of ROM

$1C00-$1FFF KIM-1 listing in KIM-1 Users manual

6530-003 ROM at $1800 dump of ROM

$1800-$1BFF KIM-1 listing in KIM-1 Users manual

On the 6530-002 and -003 PB6 is CS1. PB5 is a normal I/O pin.

6530-004 ROM at $7000 dump of ROM

$7000-$73FF TIM Terminal Monitor, see the TIM page

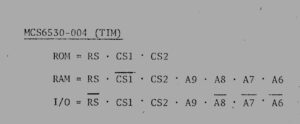

On the TIM 65330-004 PB6 is CS1 and PB5 is CS2.

MCS6530-004 Chip Select Equations (thanks Scott Barnes)

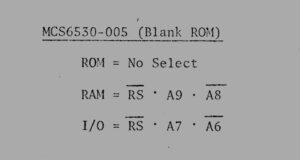

6530-005 or R3005-12, no ROM dump

According to this OSI appnote this is an unprogrammed version of the 6530 TIM.

The text in the appnote says:

The 6530-005 is an unprogrammed version of the TIM-1. It has 16 parallel lines as the 6820 but also has a 64 word RAM and a programmable interval timer which can generate an IRQ. The 6530-005 is available from MOS Technology at a cost slightly higher then that of a 6820 PIA.

I have several real 6530-005 IC’s in my stock

MCS6530-005 Chip Select Equations (thanks Scott Barnes)

6530-006 ROM at $1800 Allied Leisure pinball version 1 (IC6)

6530-007 ROM at 1C00 Allied Leisure pinball version 1 (IC3)

6530-008 ROM at $1400 Allied Leisure pinball version 1 (IC5)

Version 2/3 of Allied Leisure Pinball

6530-009 or R0008-11 IC5 ROM at $1400 dump of ROM

6530-010 or R0006-11 IC6 ROM at $1800 dump of ROM

6530-011 or R0007-11 IC3 ROM at $1C00 dump of ROM

6530P R3004-11 ROM dump, probably also a pinball machine part.

R3014-3 System 1 Sound board

6530-012 Gottlieb System 1 sound board (R3014-12)

6530-013 Gottlieb System 1 sound board (R3014-13)

6530-014 Gottlieb System 80 series sound board (R3016-11)

6530-016 Used in Gottlieb system 80/80A/80B sound boards

6530-024 ROM at $8C00 dump of ROM

Commodore Chessmate (based upon Peter Jenning’s MicroChess)

6530-0210 dump of ROM

6530-241 MIOT in pinball machines

6530-243 MIOT in pinball machines

Commodore diskdrives ROM at $FC00-$FFFF

901466-01 6530-??? 2040 DOS 1.0 Shugart SA390 2040, 3040 and 4040

901466-02 6530-028 4040 DOS 1.2 Shugart SA390 2040, 3040 and 4040

901466-04 6530-034 8050 DOS 2.0 DOS 2.1 Shugart SA390

901483-02 6530-036 8050 DOS 2.5

901483-03 6530-038 8050 DOS 2.5 Micropolis 1006-II (8050)

901483-04 6530-039 8050 DOS 2.5 Tandon TM100-3M (8050)

901884-01 6530-040 8X50 DOS 2.7 Tandon TM100-3M (8050) Tandon TM100-4M (8250)

901885-01 6530-044 8X50 DOS 2.7 Micropolis ???

901885-04 6530-047 8X50 DOS 2.7 Micropolis 1006-II (8050) Micropolis 1006-IV (8250) Micropolis 1106-II (Safari, 8050) Micropolis 1106-IV (Safari, 8250)

901869-01 6530-048 DOS 2.7 M.P.I. 101SM (8050)M.P.I. 102?? (8250)

251256-02 6530-050 8250 DOS 2.7 Matsushita JU-570-2 (8250LP)

Most of the information on this pages is also found on the pages of Martin Hoffman Vetter

On this page:

The 6530 was produced by most licensed 6502 manufacturers, from MOS Technology/Commodore SG to Rockwell and Synertek. All production datasheets that I have seen are identical

The oldest one is a preliminary MOS datasheet for the MCS6530, missing the ordering pages of the production version.

The most complete datasheet of the 6530 are the Synertek and Rockwell versiona, first in next table.

The 6532 exists in CMOS variants, I have only seen the California Micro Devices GTE 65SC32 variant.

|

Synertek 65C32 preliminary |

|

GTE G65SC32 |

|

CMD G65SC32 |

|

GTE G65SC32 |

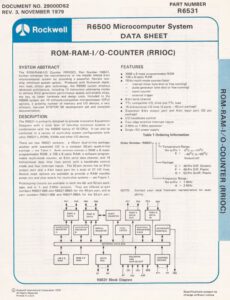

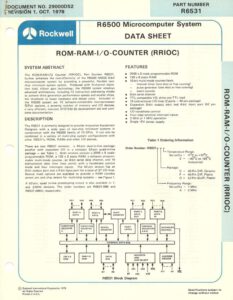

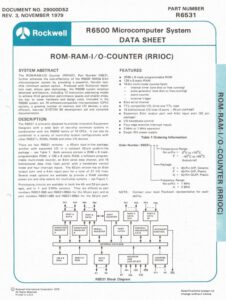

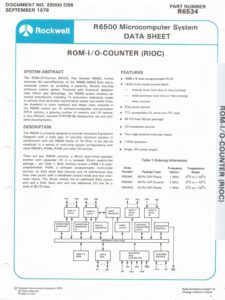

In Rockwell databooks there are more RIOTs described. 6531, 6534. Never seen in the wild, a mention here and there of being used in pinball machines.

The timer/counter is a lot more capable, 16 bits etc.

|

R6531 ROM-RAM-I/O-Counter (RRIOC) |

|

R6531 ROM-RAM-I/O-Counter (RRIOC) |

|

R6531 ROM-RAM-I/O-Counter (RRIOC) |

|

Rockwell R6534 ROM-IO-Counter (RIOC) |

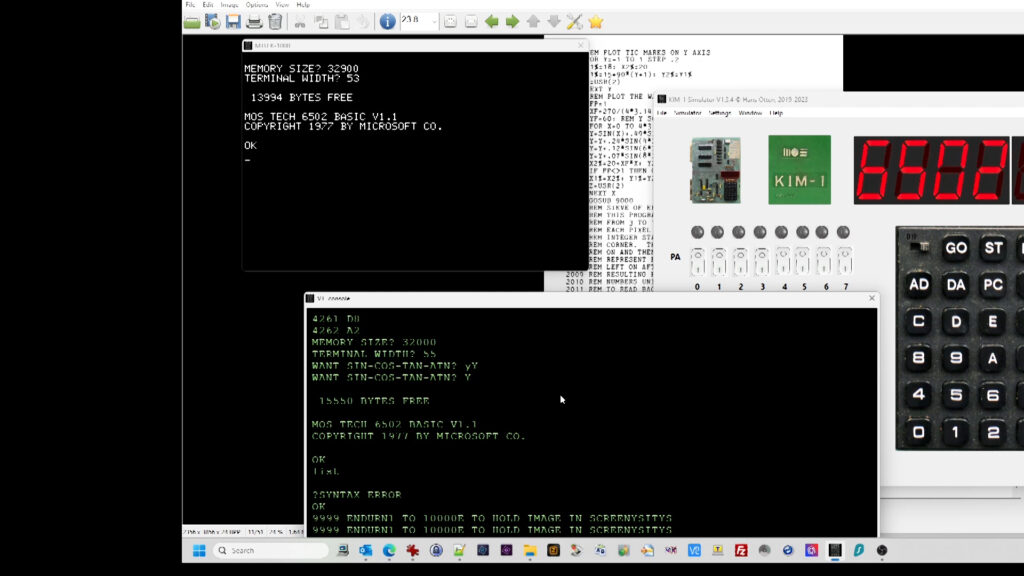

New version of the KIM-1 Simulator. Now version 1.3.5. 3 oktober, and now 9 oktober 1.3.7!

– text file upload in console also accepts UNIX style line endings and DOS type

– Debugger more visible in main form, and new menu with Search, Fill, Move/copy in memory

– added PRG Commodore binary file load and save (for the IEC users!)

– debugged and tested the VT100 codes of the console

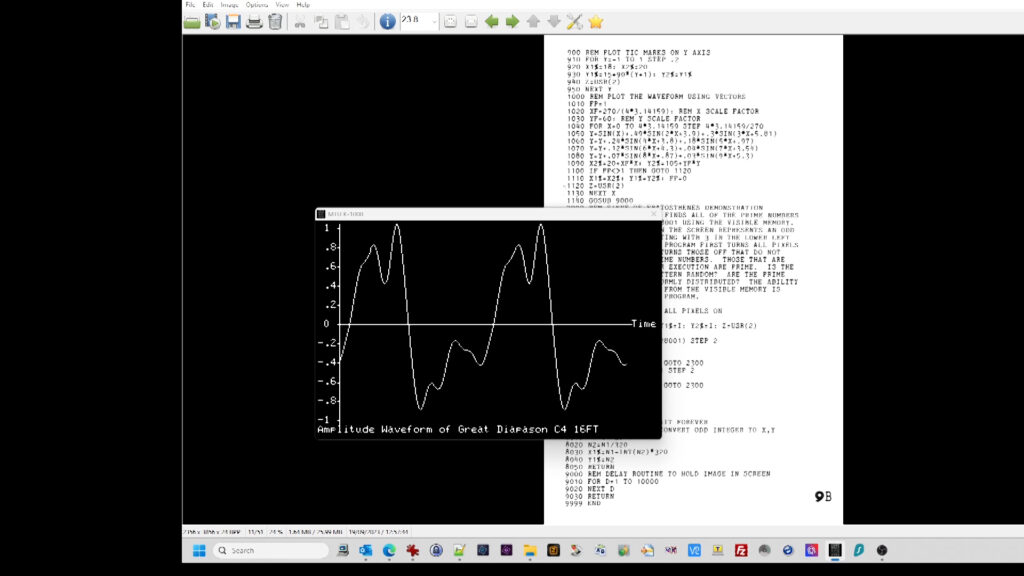

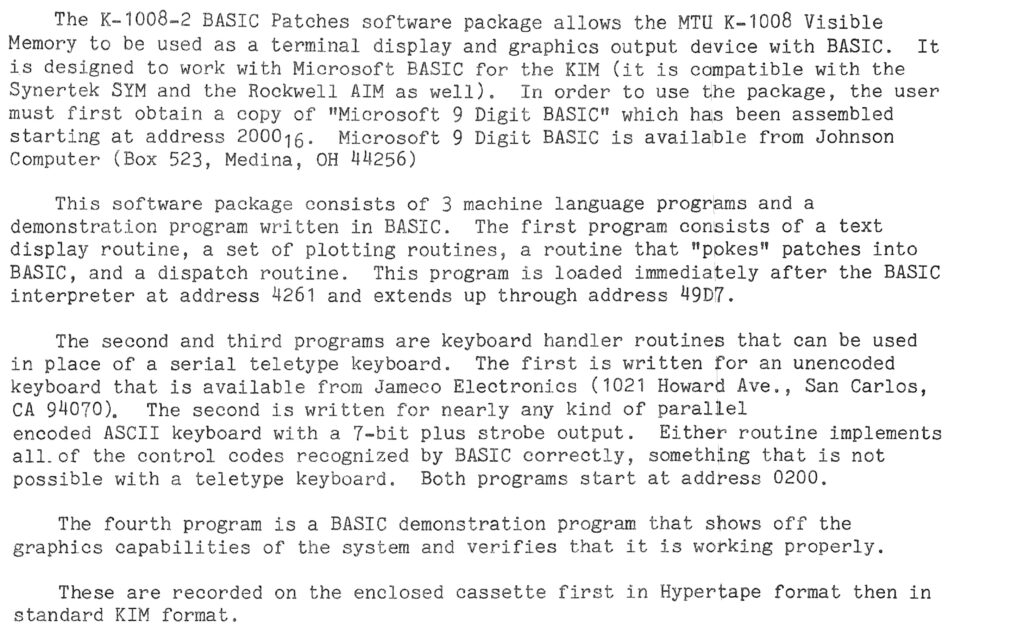

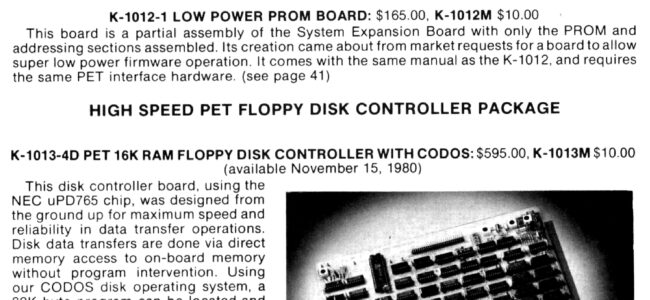

Added to the MTU pages:Patches to Microsoft Basic K-1008-2L sources and binaries, ready to run!

This package was distributed as a manual and a cassette with some binaries. The user is supposed to type in and adapt the sources himself.

|

K-1008-2L Patches to Microsoft BASIC manual, cleaned up |

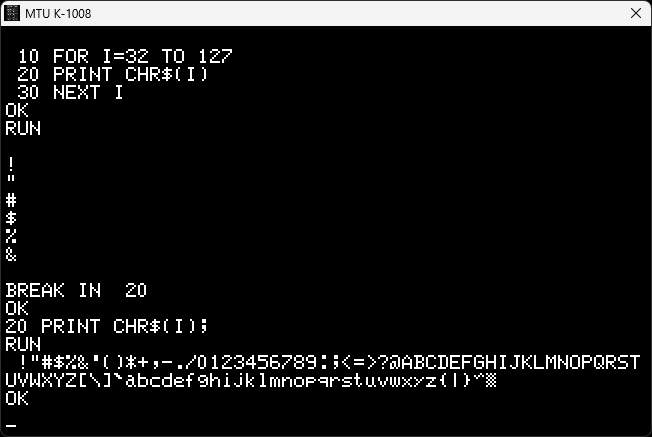

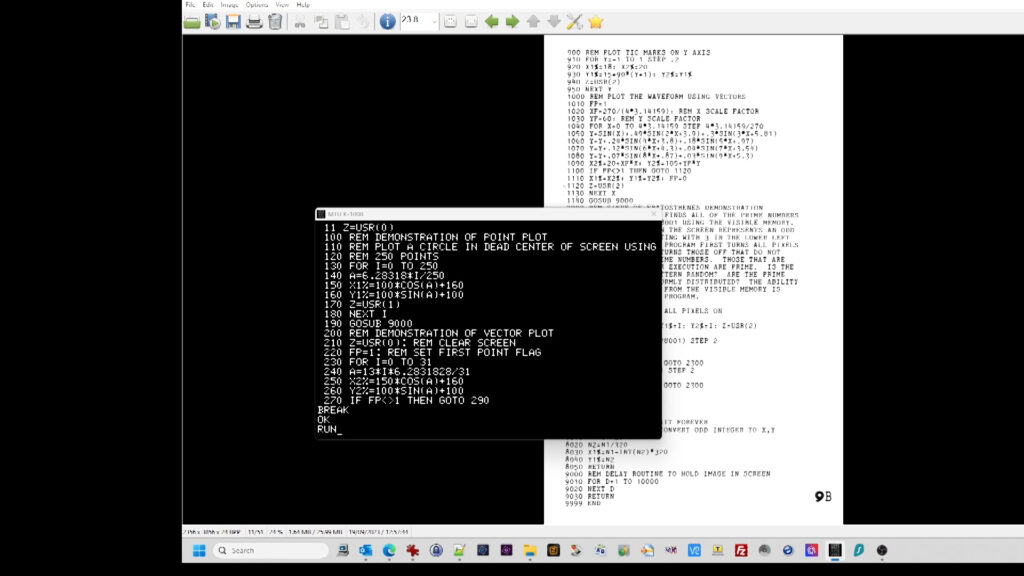

The original sources of the Basic patches, the Basic demonstration program and the parallel keyboard routine are typed in by me in october 2023.

Assembler and binary versions of the Patches

Download here the assembler sources and binary versions of the K-1008-2L Patches to Microsoft BASIC

In this archive:

The manual: K-1008-2L Patches to Microsoft BASIC cleaned.pdf

Folders with running software typed in and assembled:

– vmbas kim1 tty lowercase: tested version of the patches to be used with the KIM-1 keyboard. Adapted for KB-9 V1.1, real lowercae characterset. see the readme.txt how to use, KB-9 included.

– vmbas Basic demo: tested with vmbas kim1 tty lowercase

Additional:

– vmbas original: original source in modern assembler format. to be used with a parallel keyboard routine

– vmbas parallel keyboard: addon to use a parallel keyboard connected to the free RRIOT port

The running software has been tested with the K-1008 emulation in the KIM-1 Simulator.

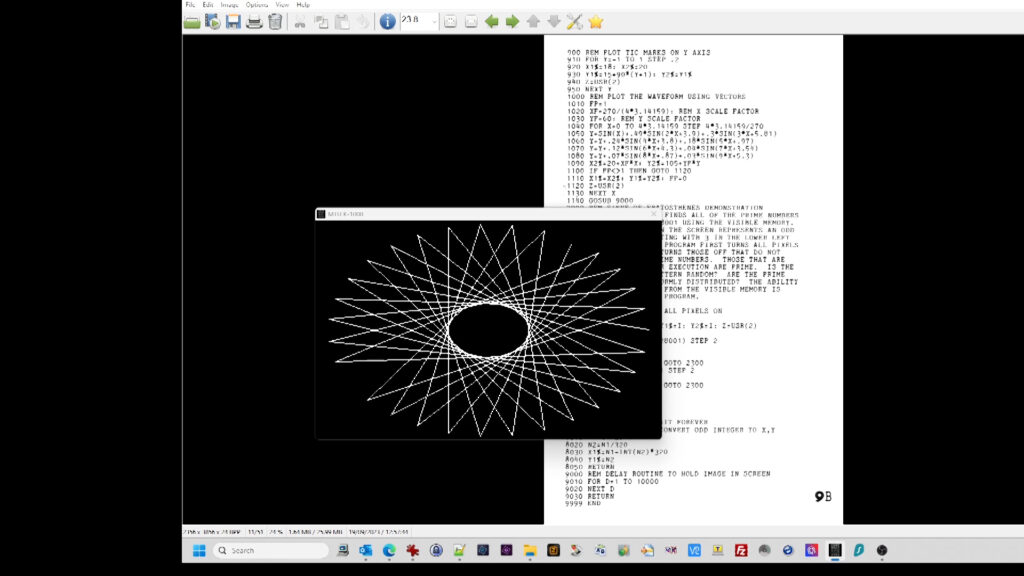

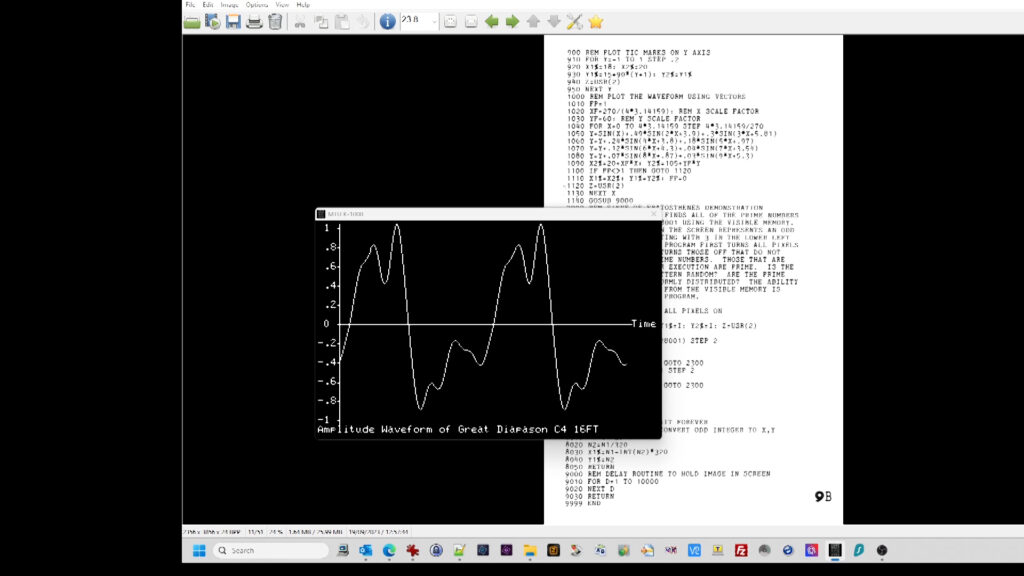

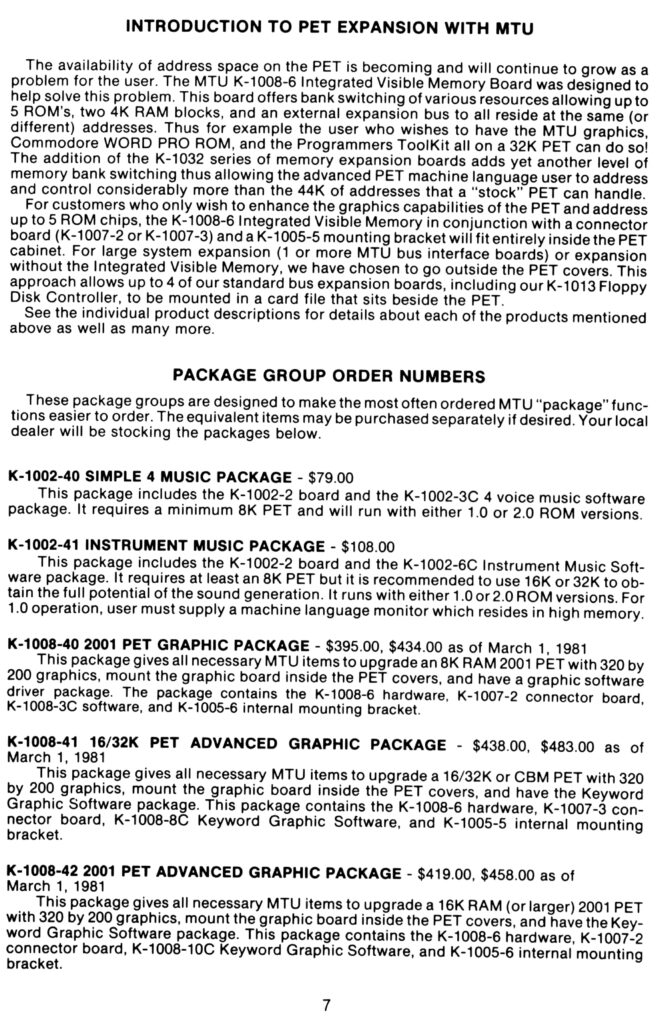

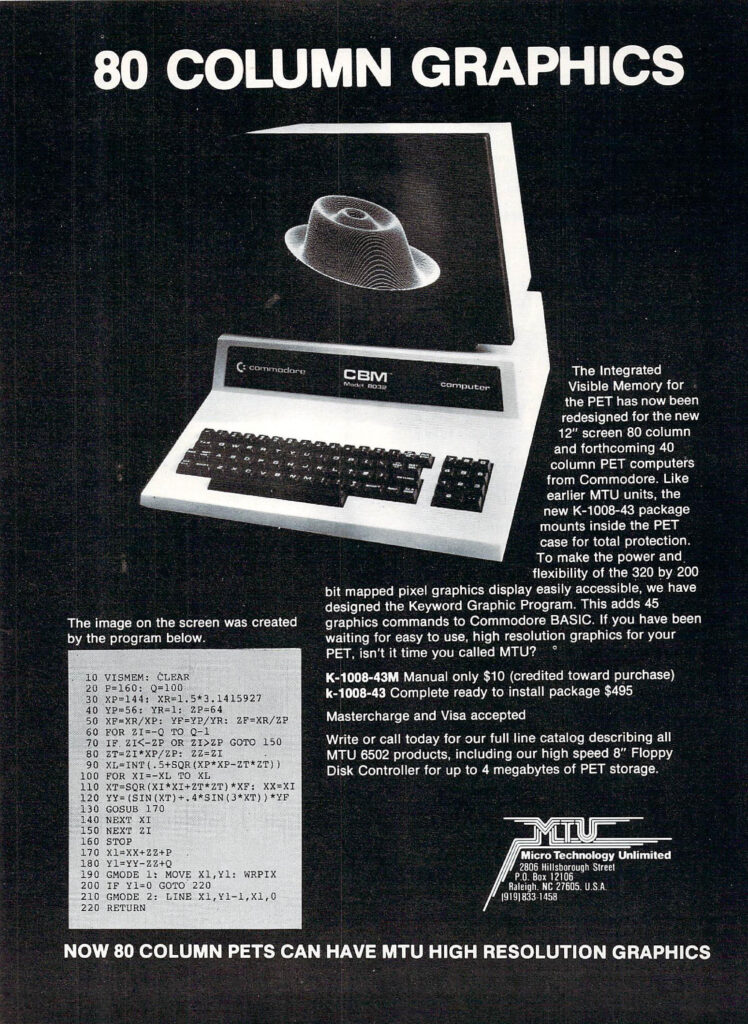

MTU produced also a number of products for the Commodore PET.

The K-1008 Visible Memory, original for the KIM-1, was also adapted to be used on the Commodore PET.

Same specifications, 320×200 bit mapped graphics, with a PET interface.

K-1008-6 Visible Memory board for the PET

Disk 1 of MTU K-1008-6 software.

Disk 2 of MTU K-1008-6 software.

\

\

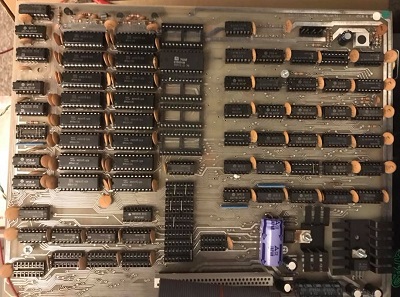

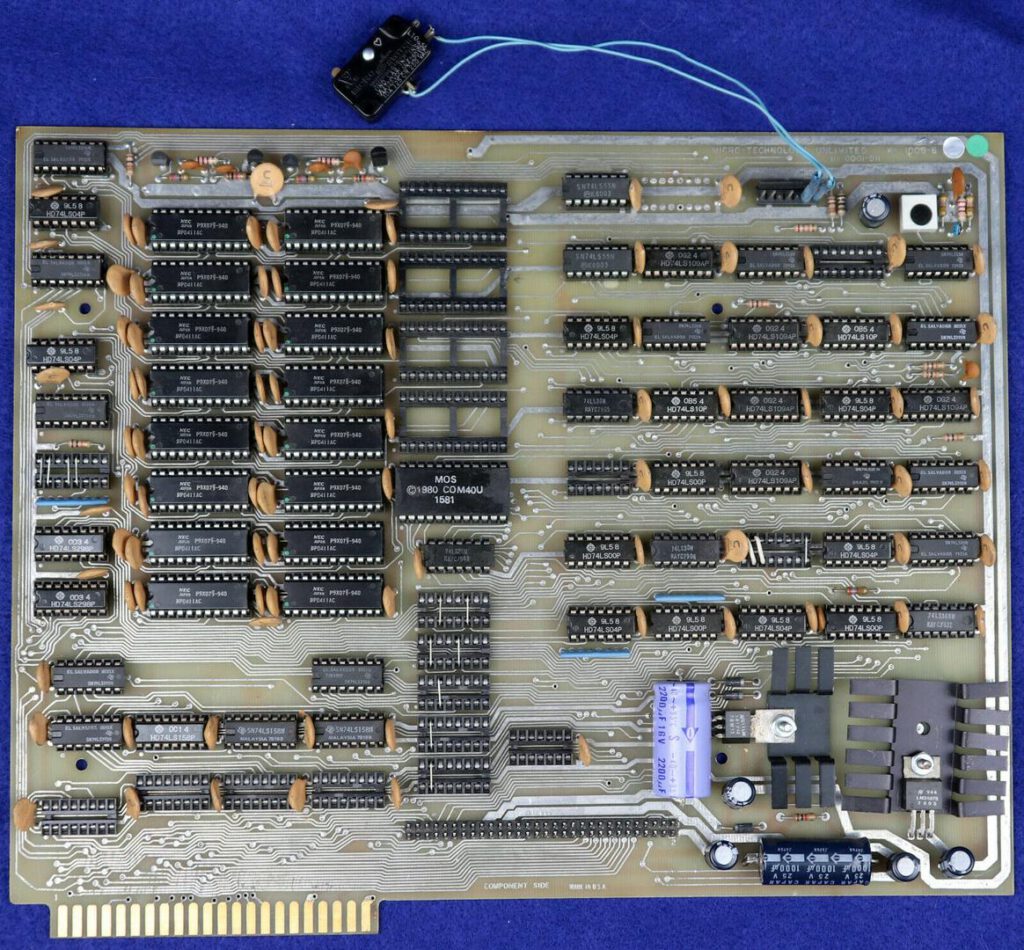

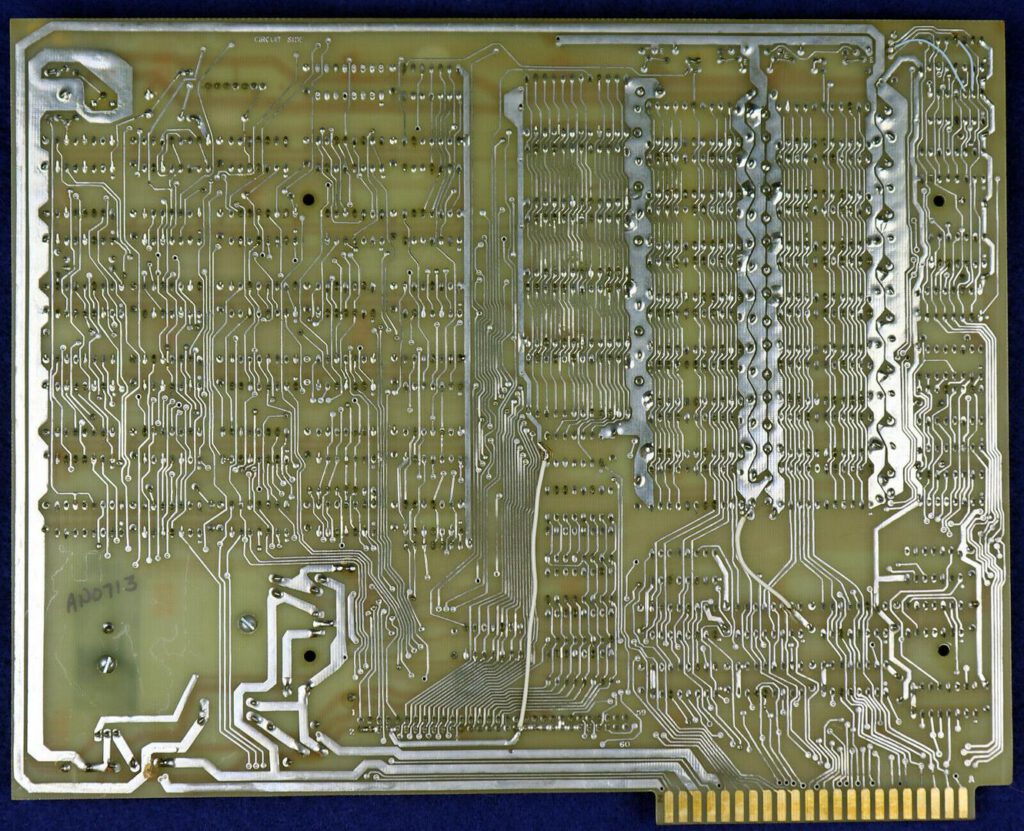

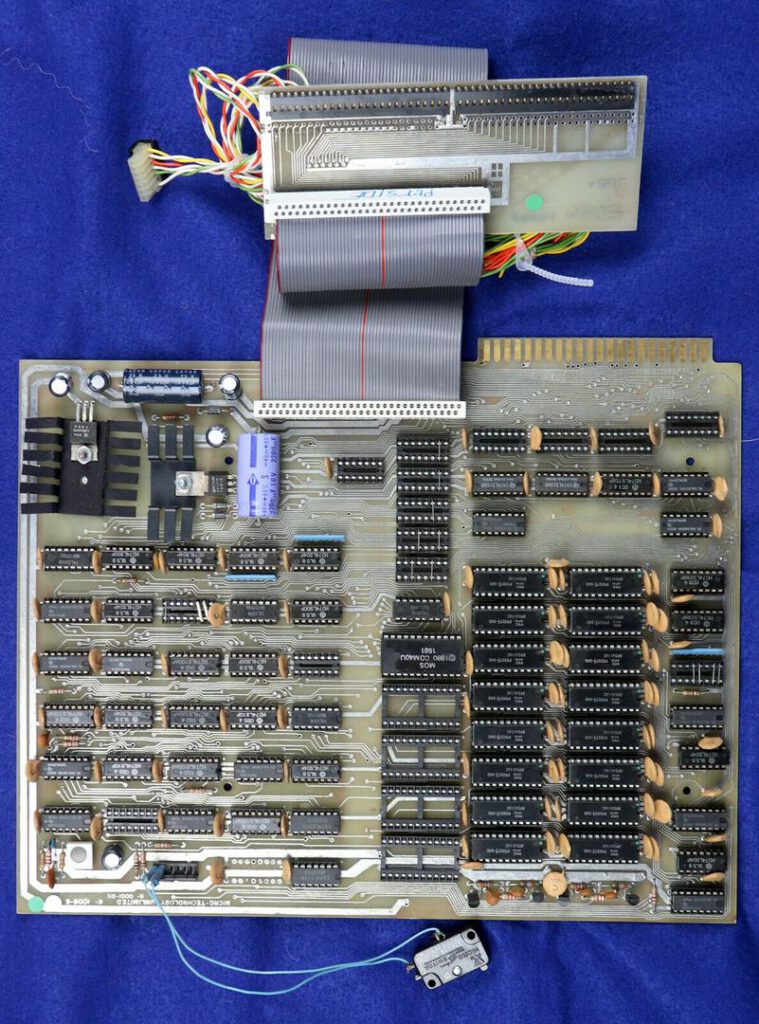

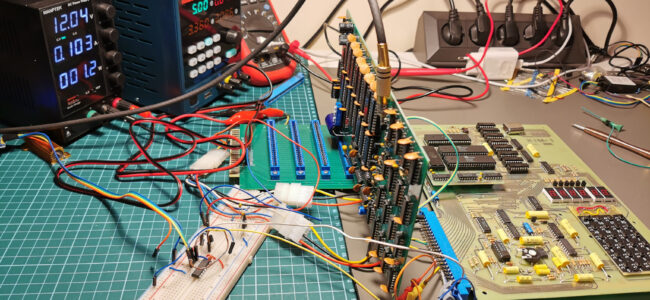

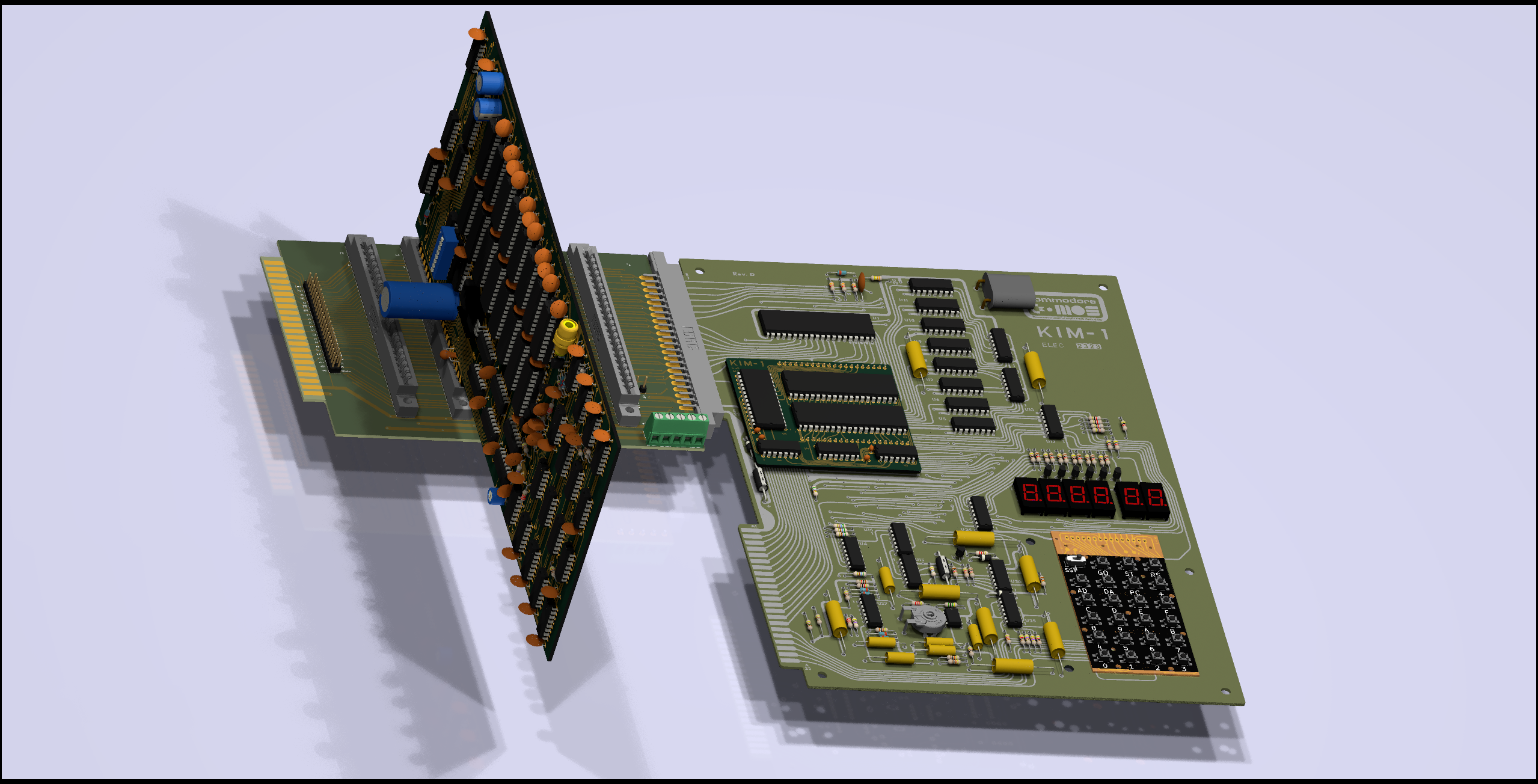

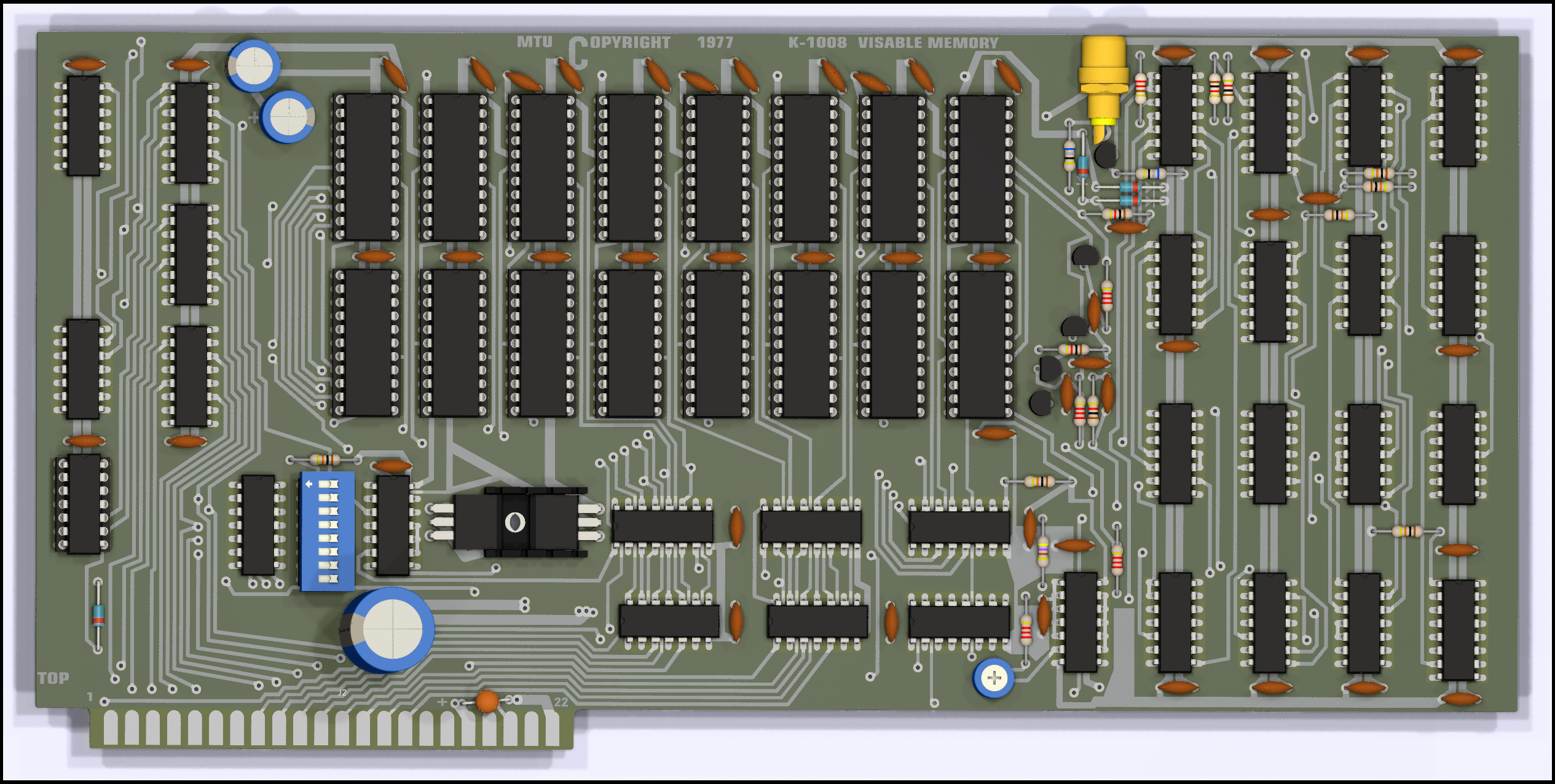

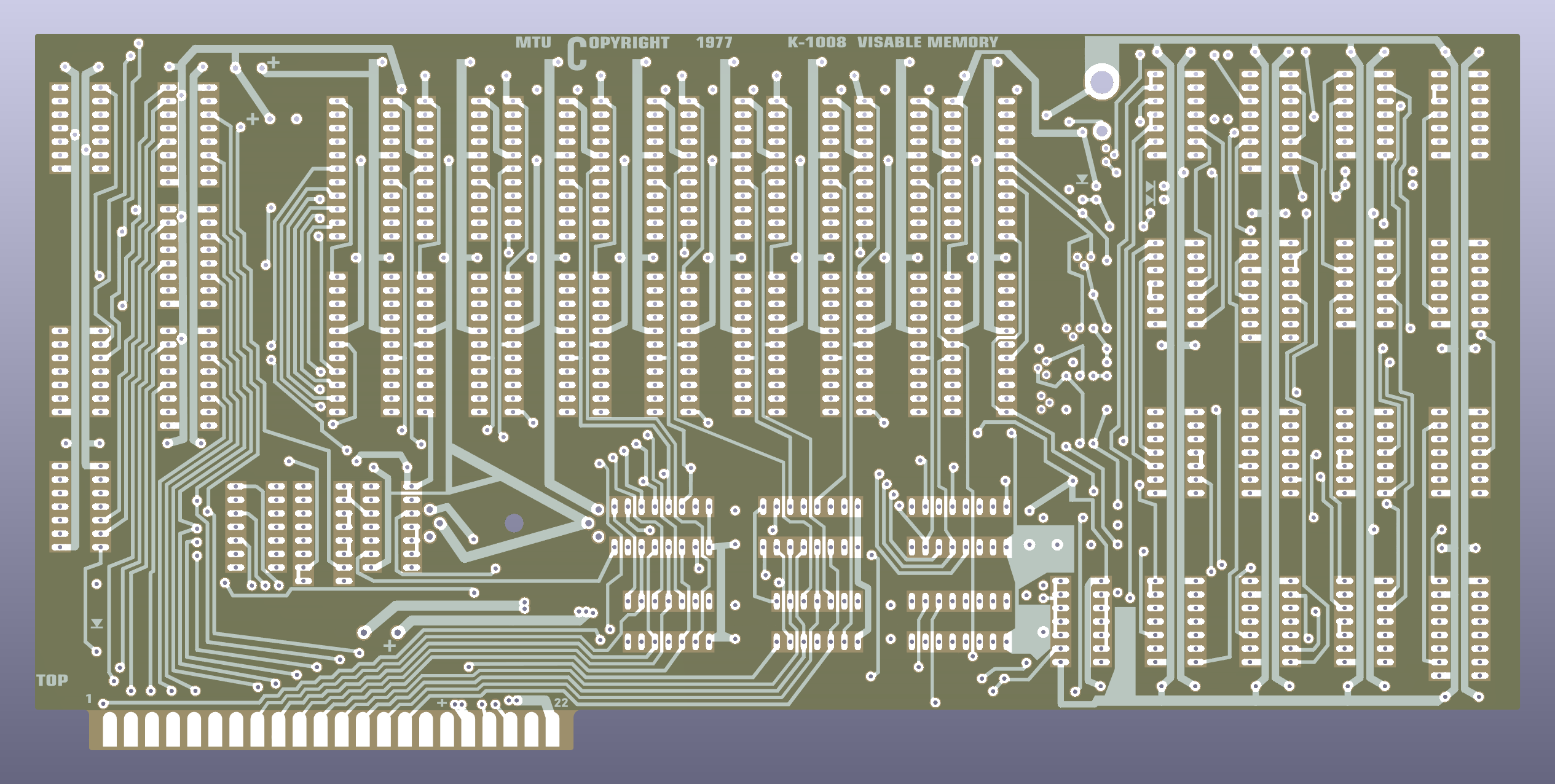

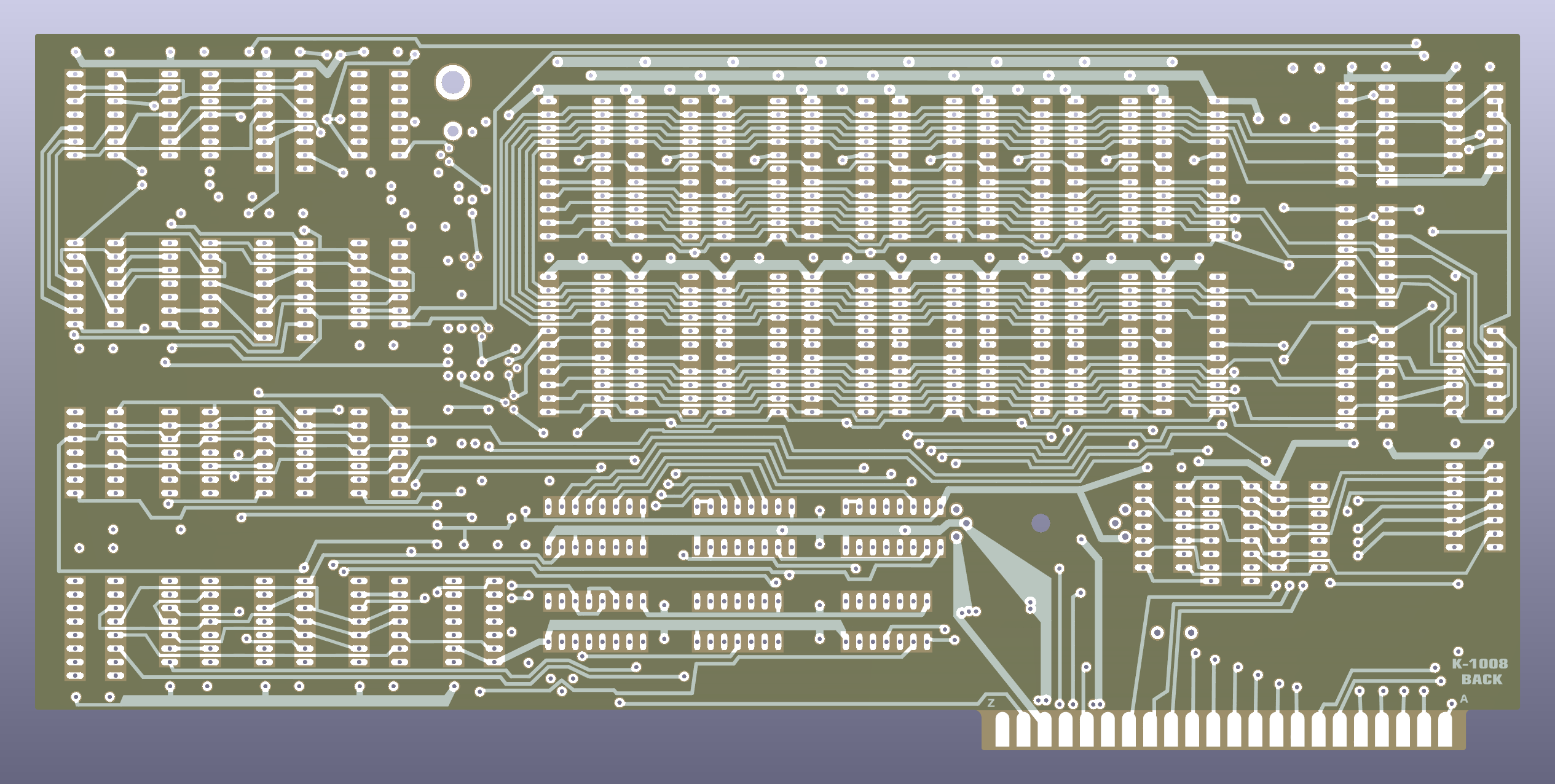

K-1008 Visable Memory Replica by Eduardo Casino

Eduardo Casino, see also his other work on KIM-1 projects, he is working on what aims to be a faithful replica of MTU’s K-1008 Visable Memory card for the KIM-1. He is following basically the same procedure as he did for the KIM-1 Rev. D replica: reproducing the schematics from the existing documentation and using photos of the original card to correct it and to replicate the PCB, and doing all of it just with open source tools.

As always, everything is available on his GitHub page.

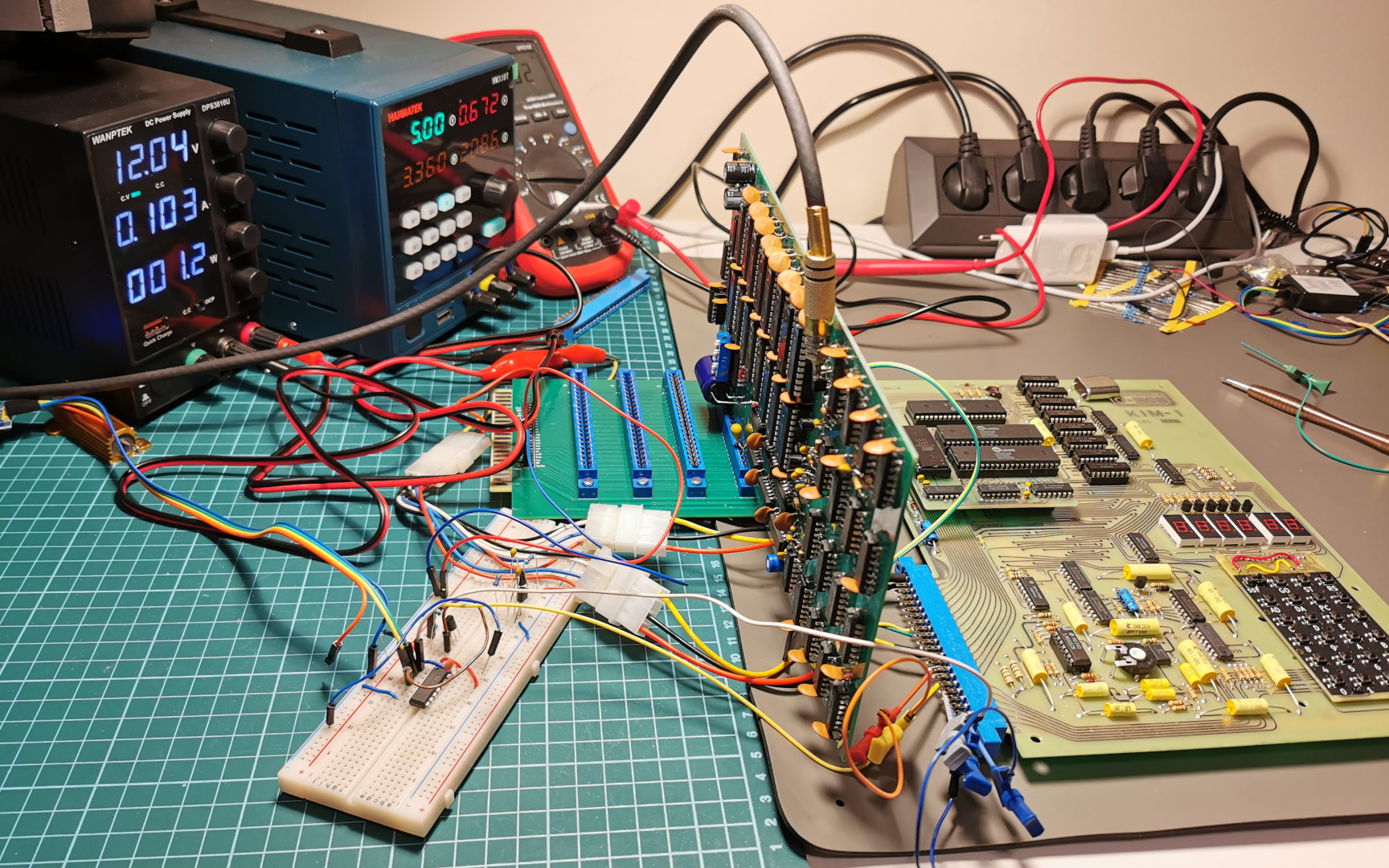

The first tests are good!

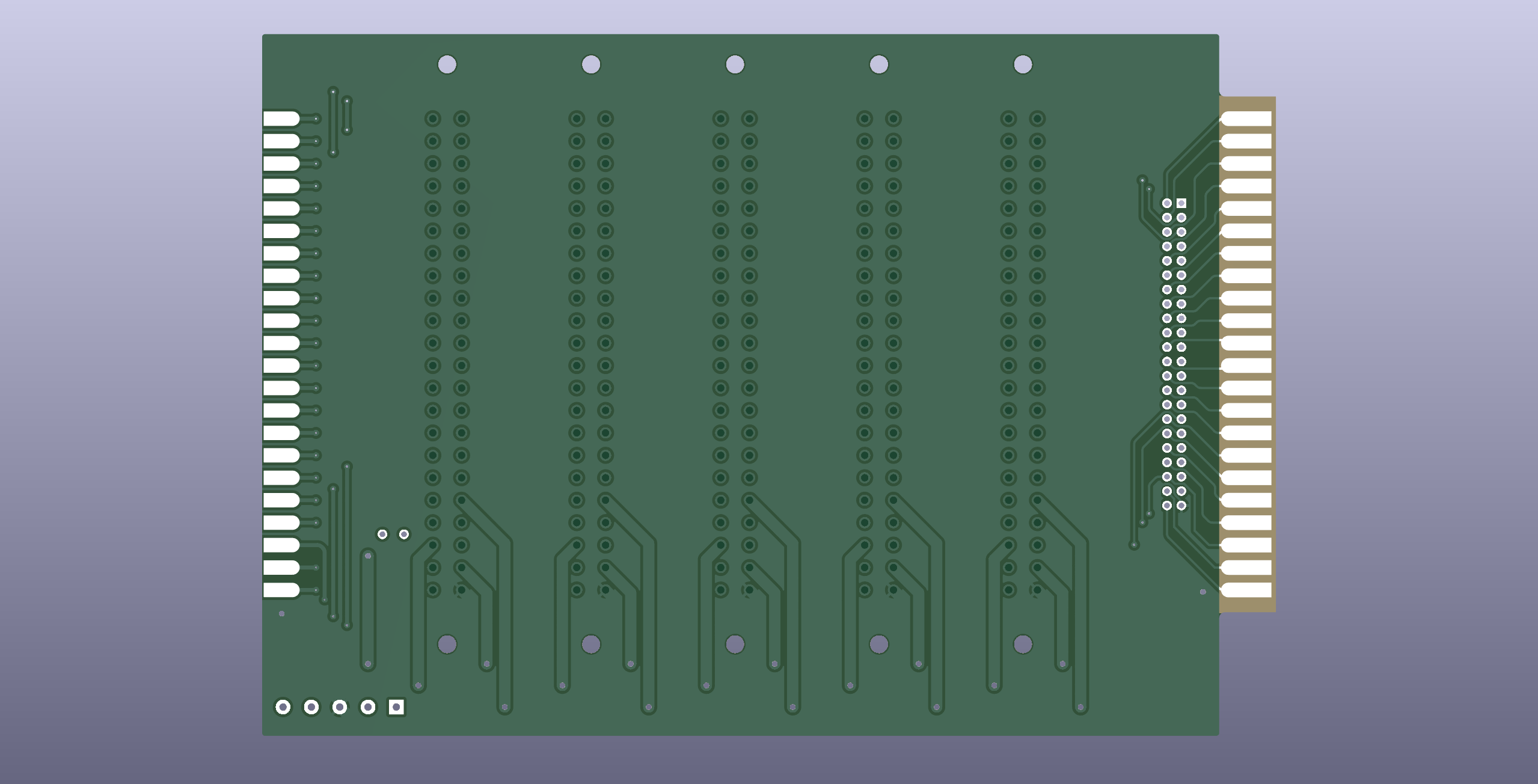

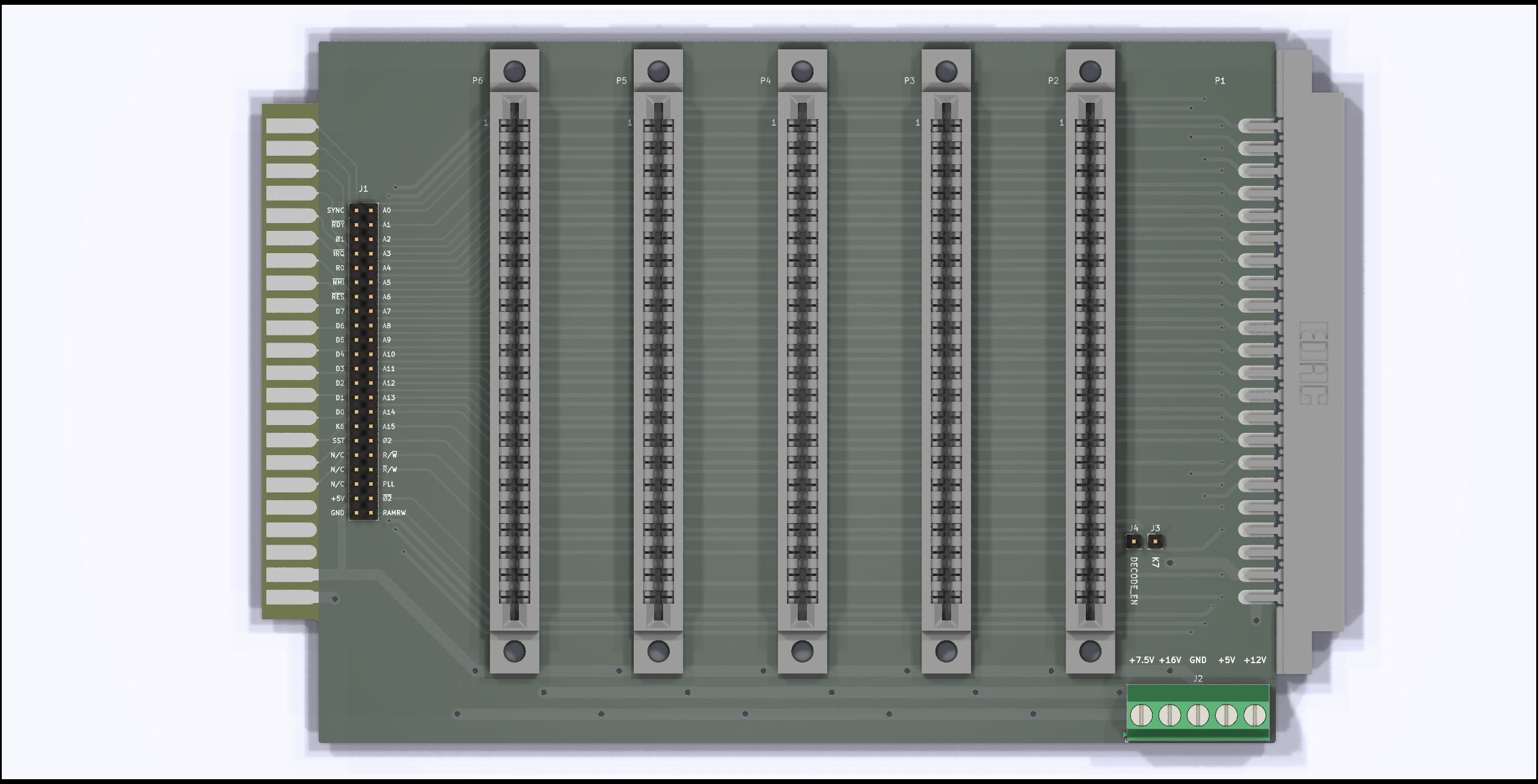

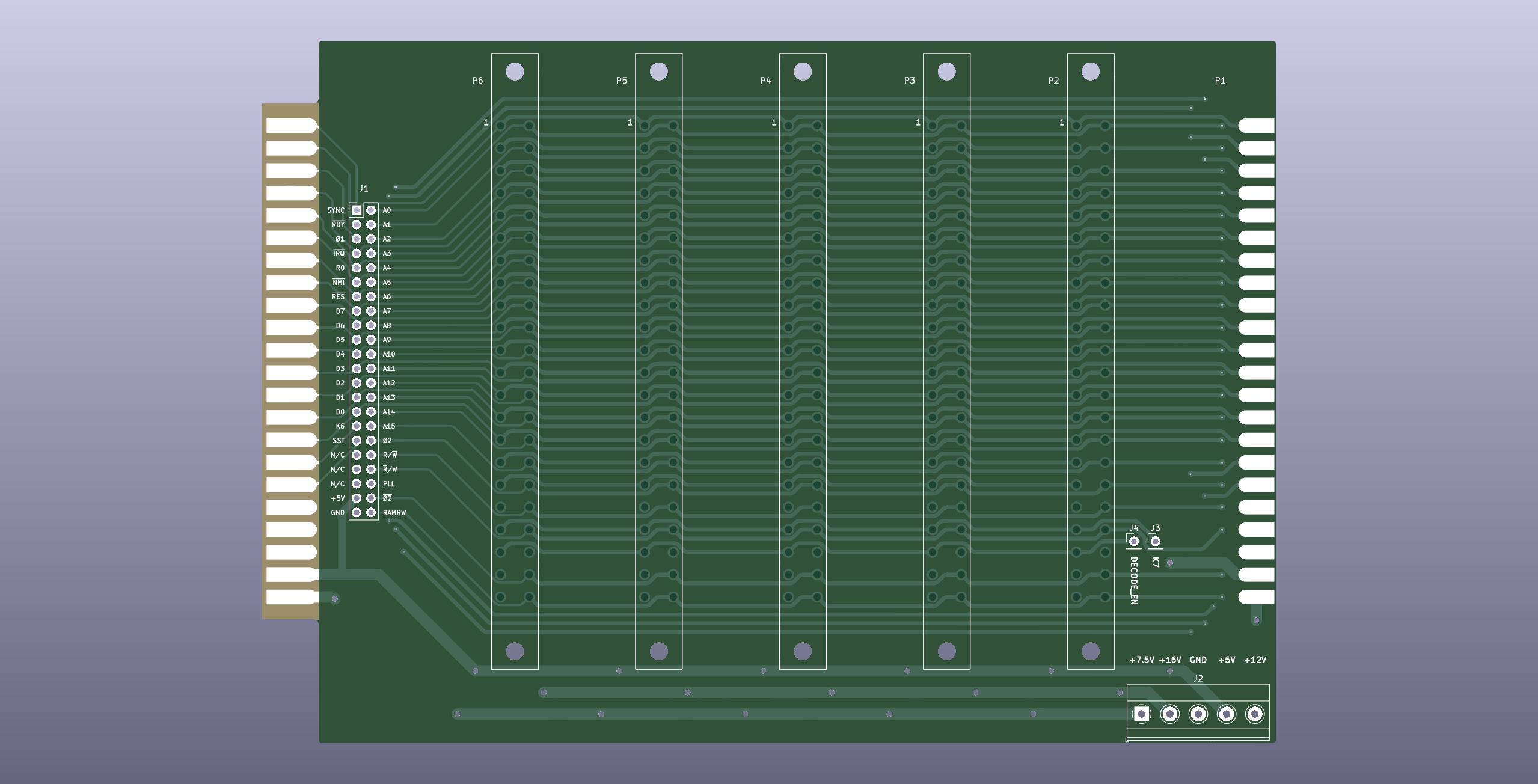

KIM-1 Expansion Board for MTU cards repository.

This board follows the MTU standard for the KIM-1 expansion bus and enables to connect up to five cards, like the K-1008 replica.

Additionally, all signals of the KIM-1 are replicated on an edge connector to allow further expansions and also on a pin header for easy breadboarding.

The MTU bus connects 1 to 1 to the KIM-1 expansion connector with the exception of pins 2,3, 16, 17, 18, 19, 20 and X, because MTU boards use some of these pins for power and expanded 18 bit address bus. See page 33 of the MTU Fall 1980 6502 Peripherals and Software catalog. Two pin connectors have to be wired to pins J (K7) and K (DECODE ENABLE) of the KIM-1 application connector.

Like in the original MTU’s bus motherboard, a five screw terminal block provides power connections for both the KIM-1 (GND, +5V and +12V regulated) and the expansion boards (+7.5V and +16V unregulated). Also, as in the original, the +12V terminal is not really connected to anything.

Everything is available on his GitHub page.

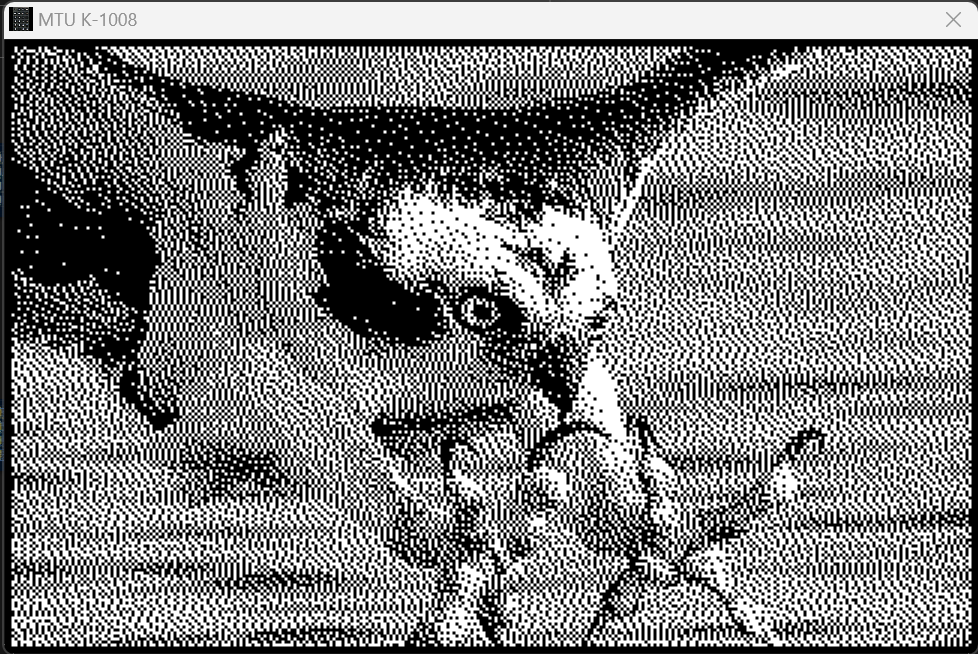

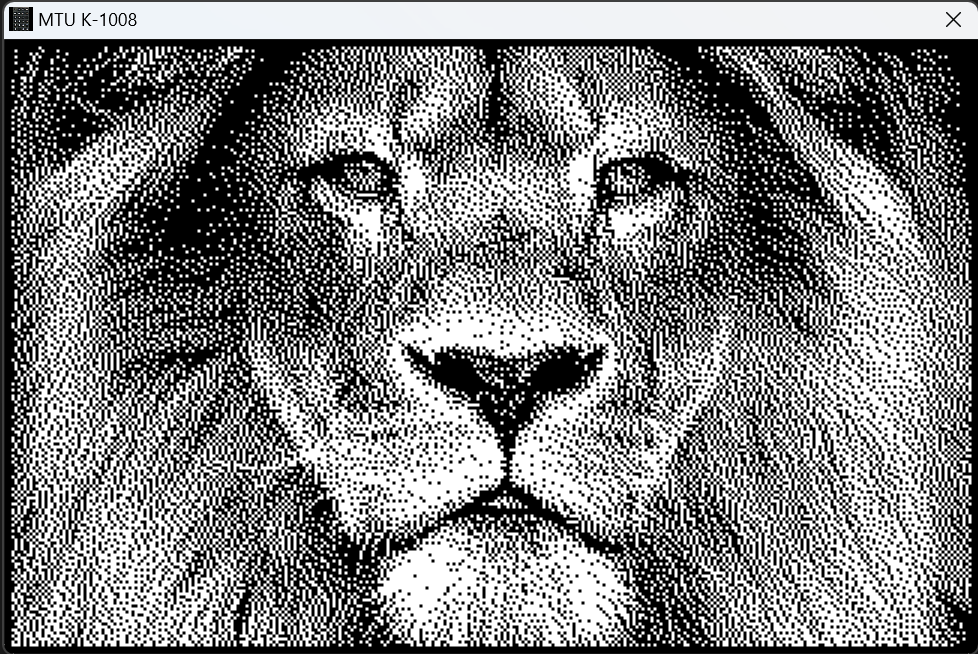

Dave Plummer asked me to add a K-1008 emulation to the KIM-1 Simulator. So I did in the spring of

2023, you can see the screenshots and video on this page made with the Simulator.

In August 2023 Eduardo Casino, who is making a K-108 replica (see below), asked me to enhance the emulator with loading binary images with images for the K-1008. That is added, load a file to memory and if that is K-1008 memory, the video display is shown.

There are several ways an image can be loaded to the K-1008 video display:

How to make a C Header image file with threshold

Make a C Header image file with dithered images

Note there is a command line program in the folder K-1008 load C Header , called LoadK1008 that converts a C header image file to a K-1008 formatted binary.

D:\k1008\LoadK1008.exe h LoadK1008 is a program to convert a 320x200 C header file from GIMP to MTU Visable memory K-1008 image LoadK1008 <C header filename> <K-1008 binary filename>

Prepare the C header file in GIMP as follows:

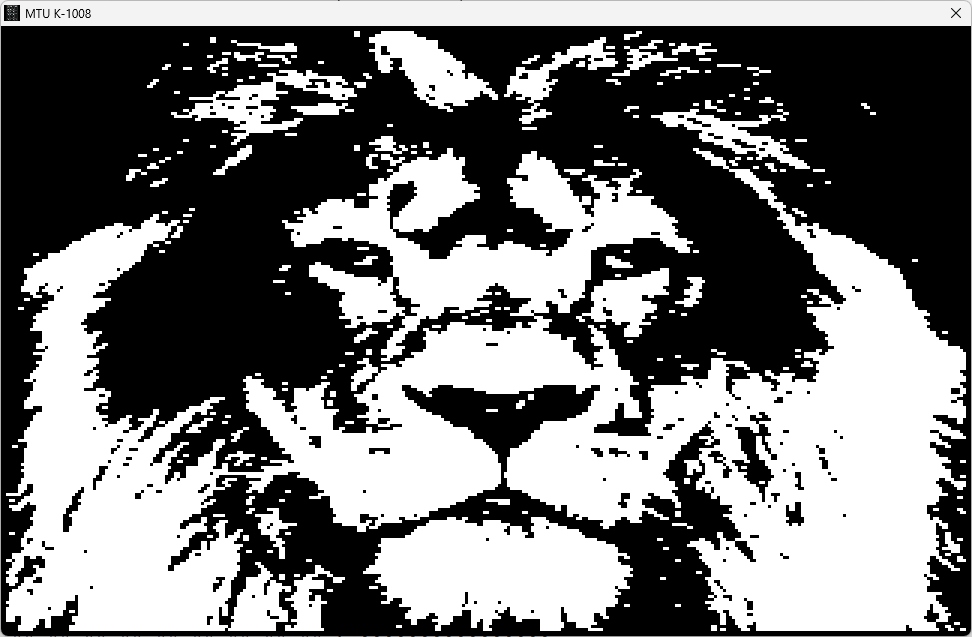

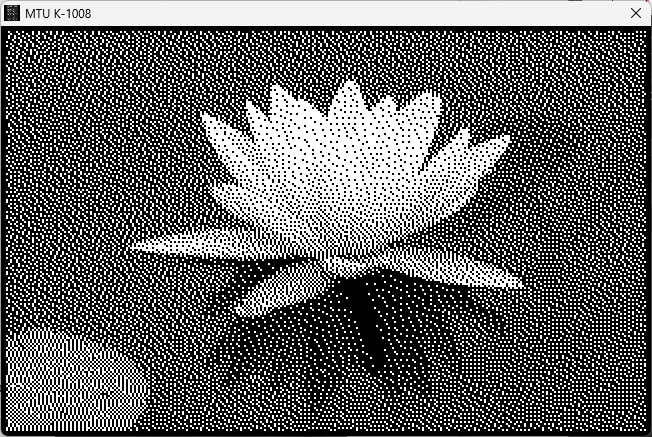

Screenshots of images imported:

Images done by Eduardo Casino with dithering.