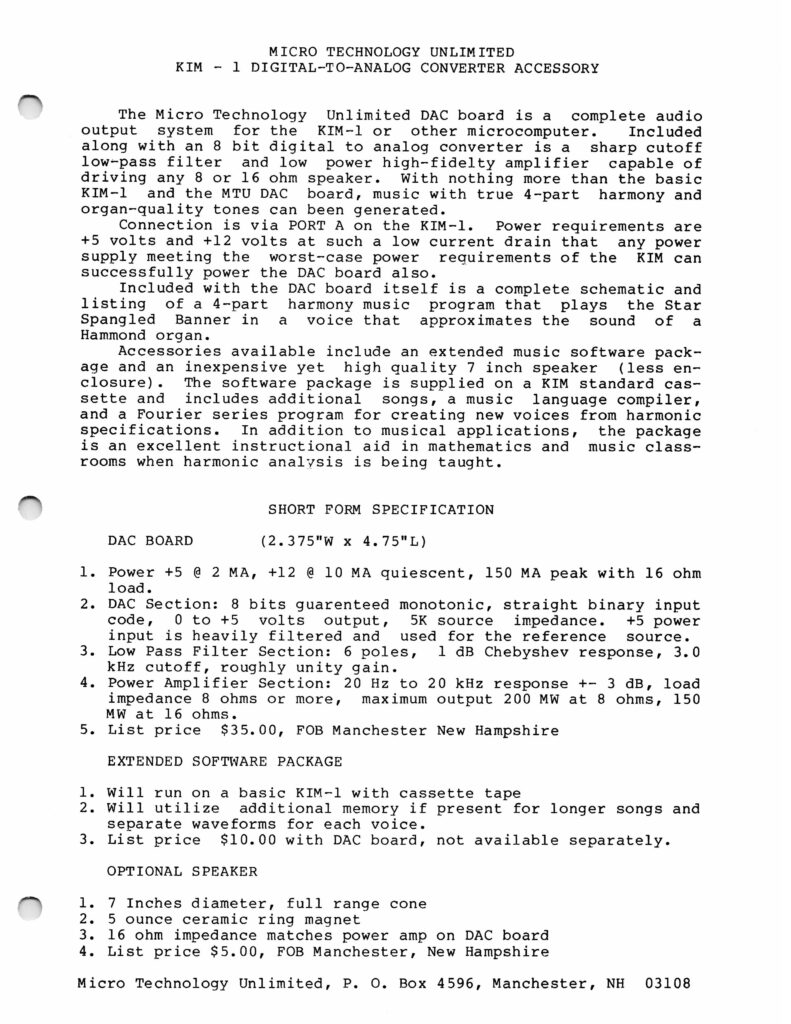

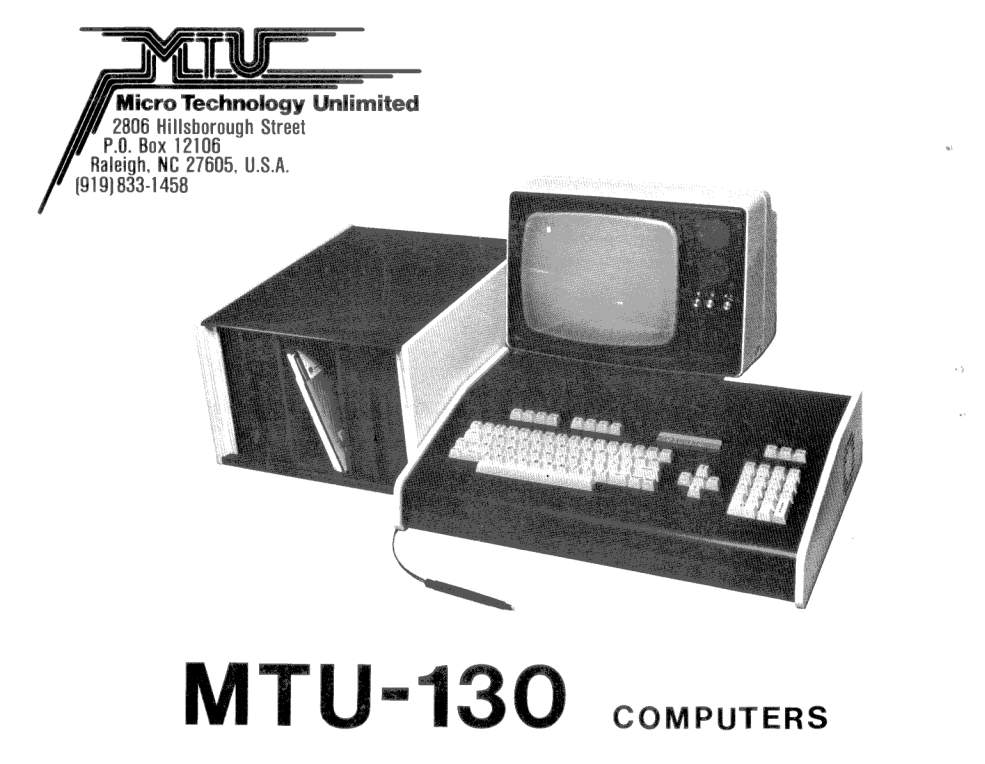

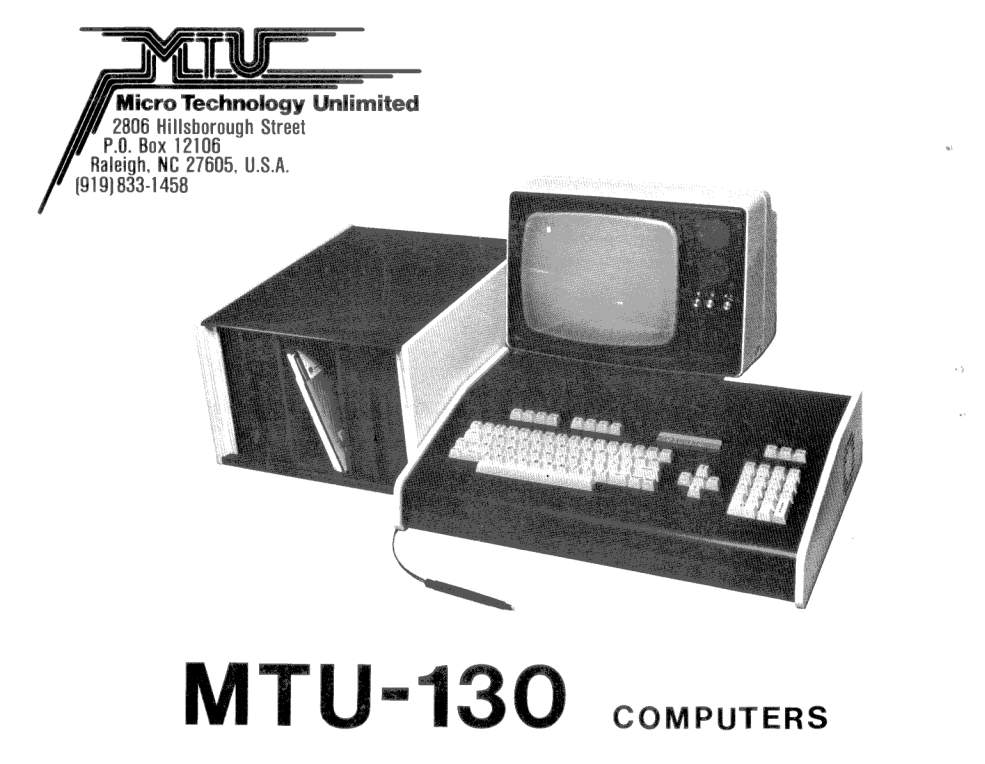

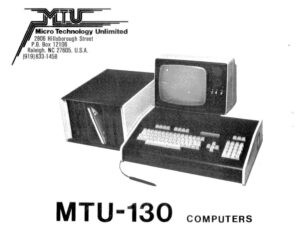

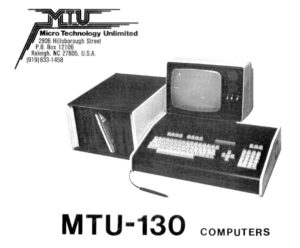

Micro Technology Unlimited MTU-130 specifications:

- CPU 6502 (8 Bit)/68000 (16 Bit)

- Operating System CODOS 2.0

- RAM 336 KB

- Storage Dual 8″ QumeTrak 842 Floppy Drives (1 MB each)

- Display Bit-mapped B&W graphics – 480×256

- Misc Peripherals Light Pen

- NEC PC-8023A-C Printer

- Datamover 68000 Co-processor

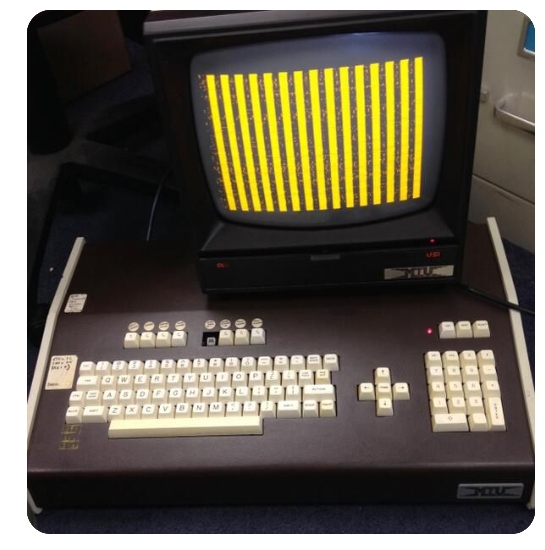

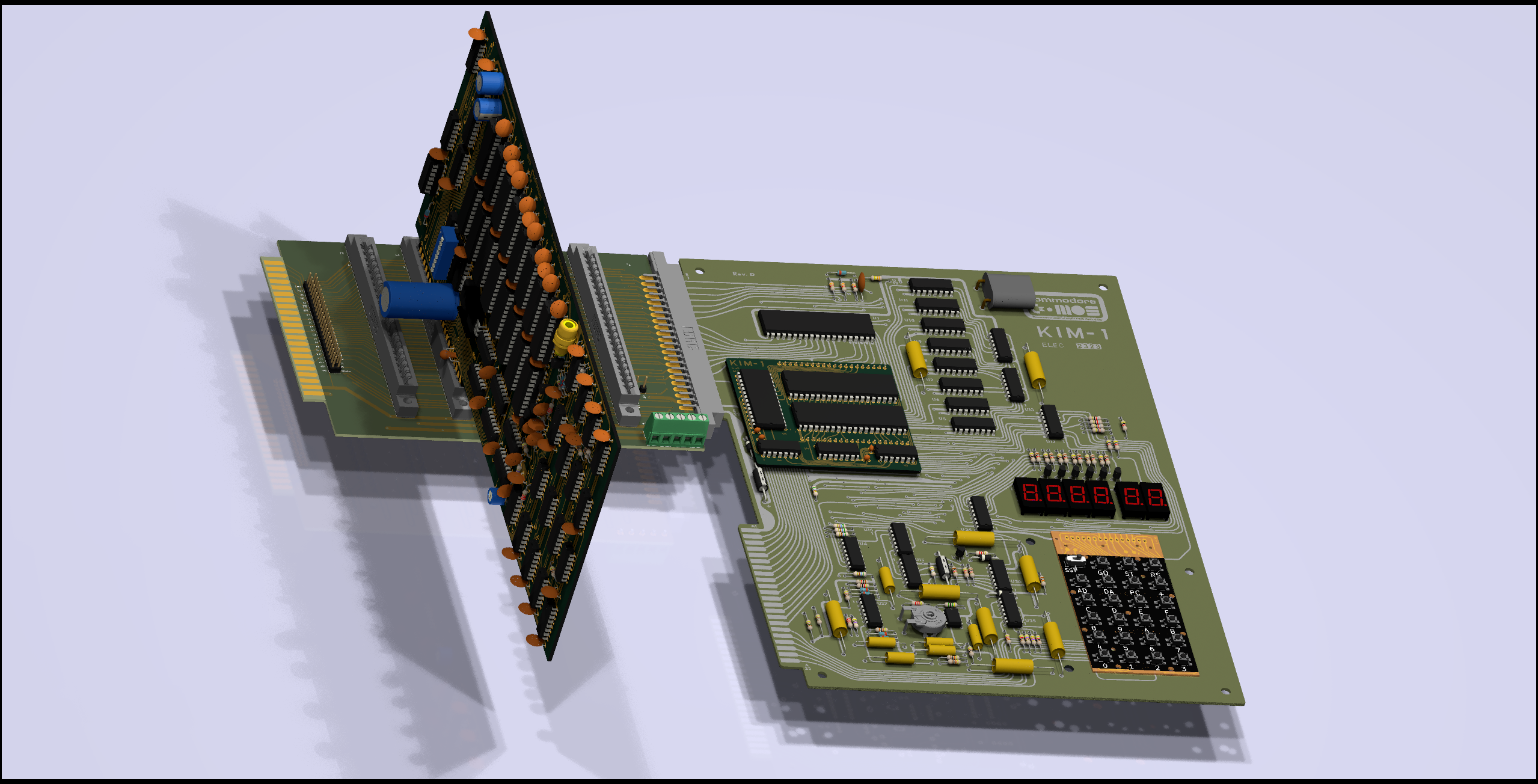

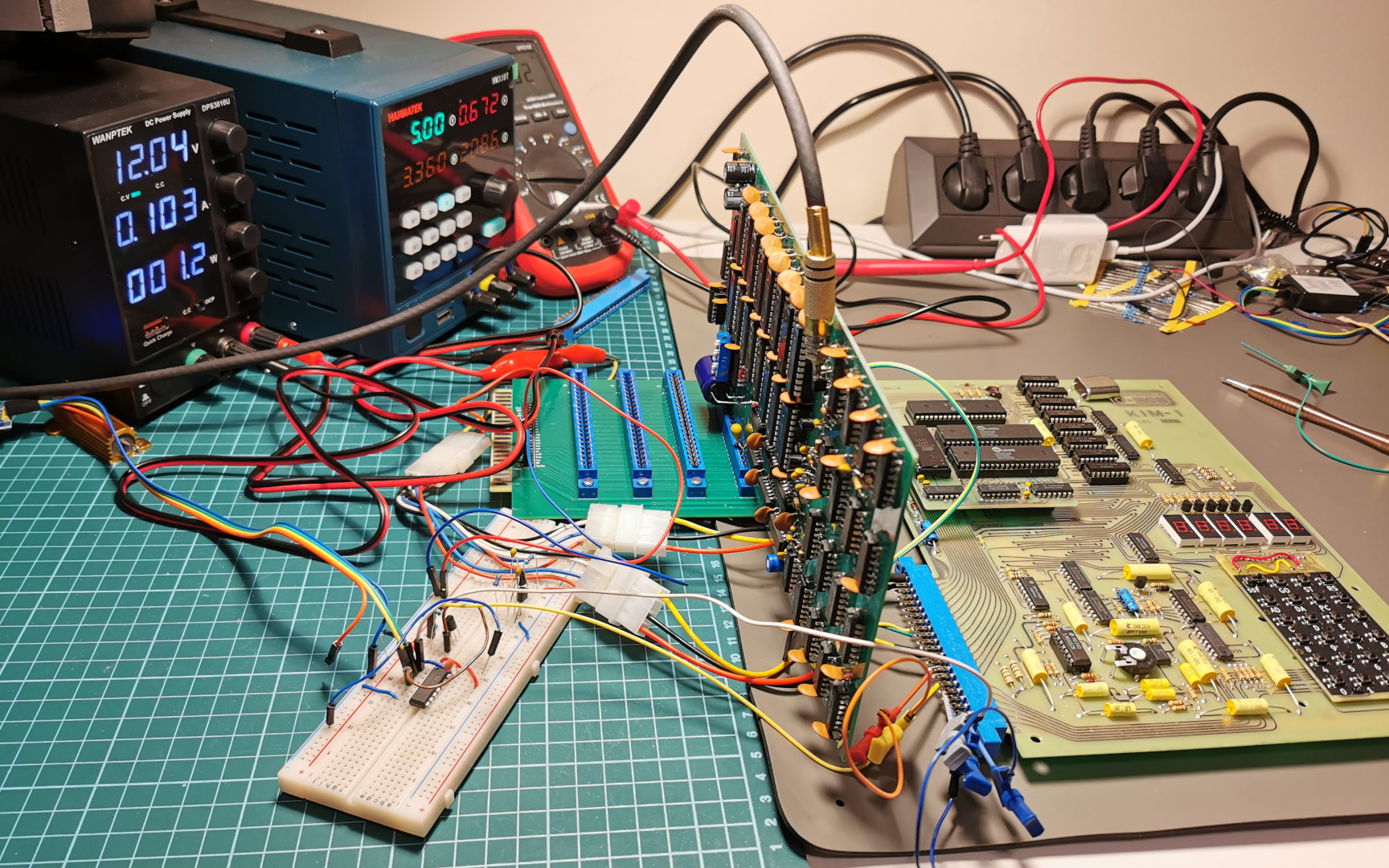

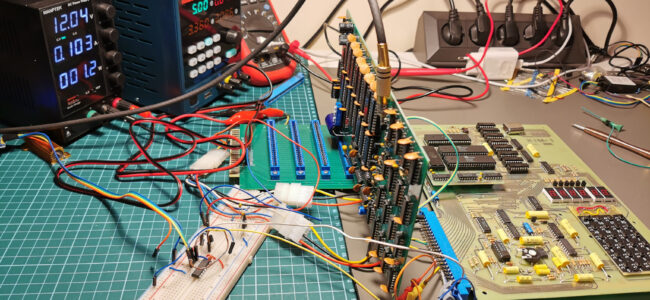

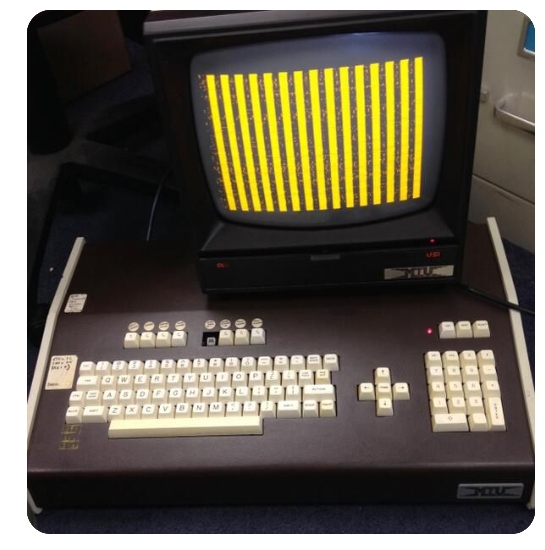

Photo from the only known to me existing MTU-130 system, owned by Dave Williams.

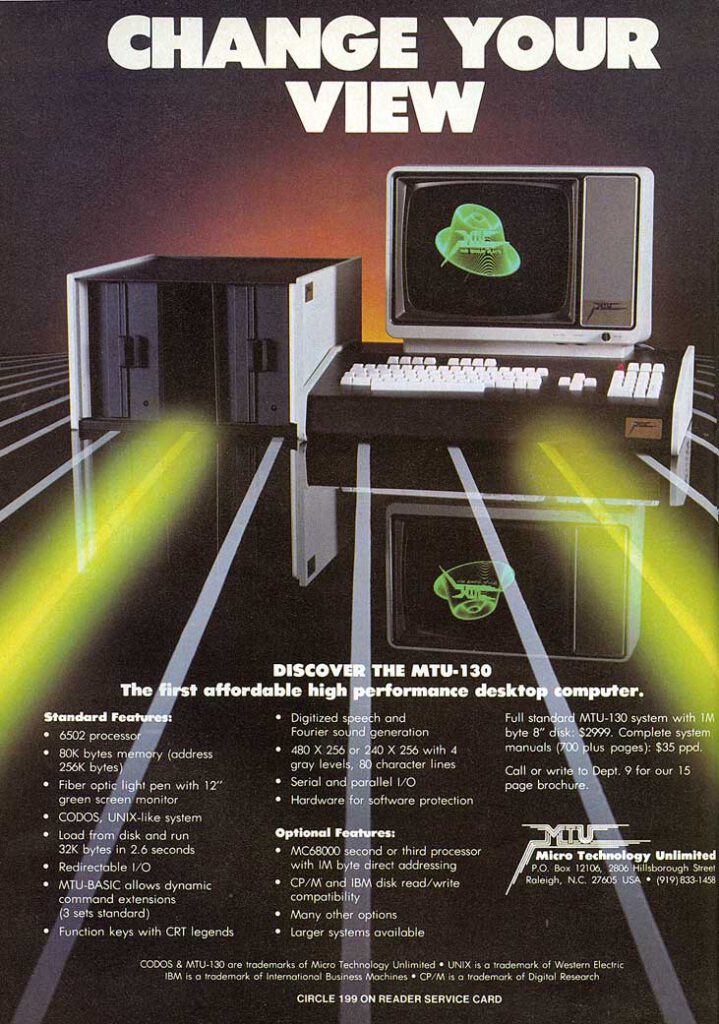

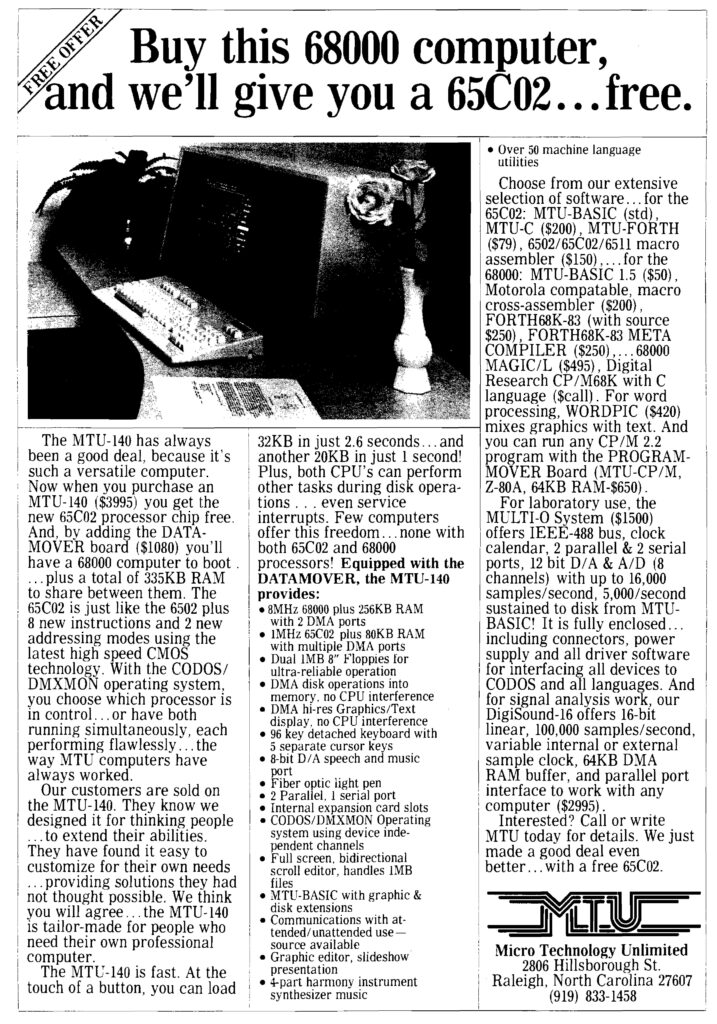

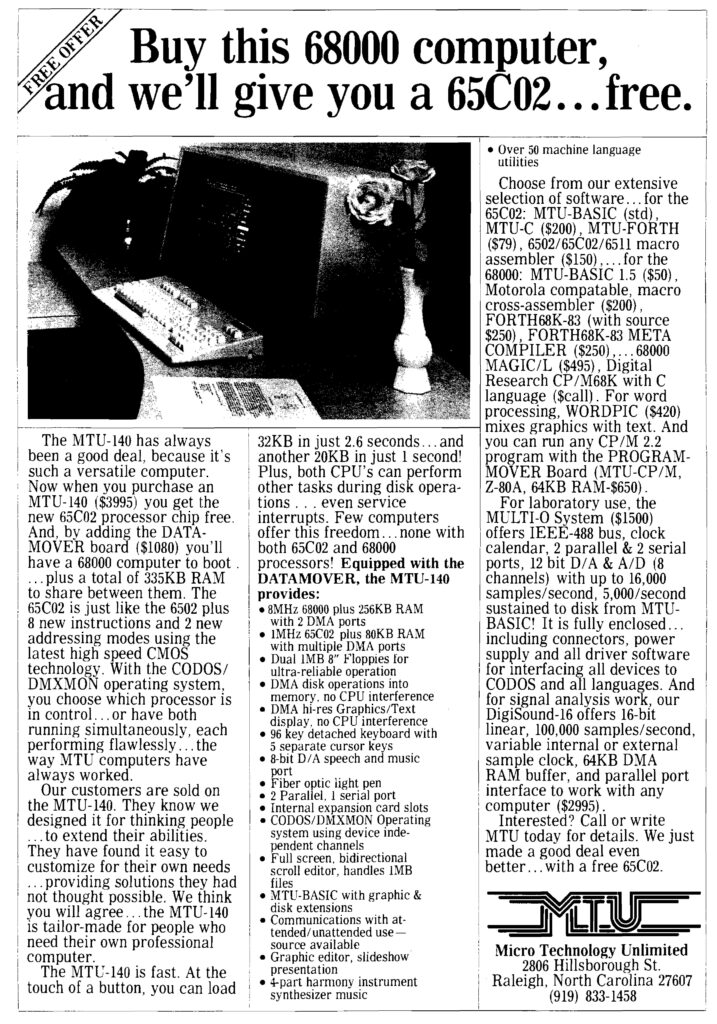

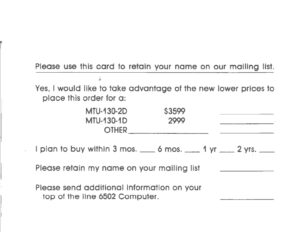

MT-140 adverts

Newsletters and brochures

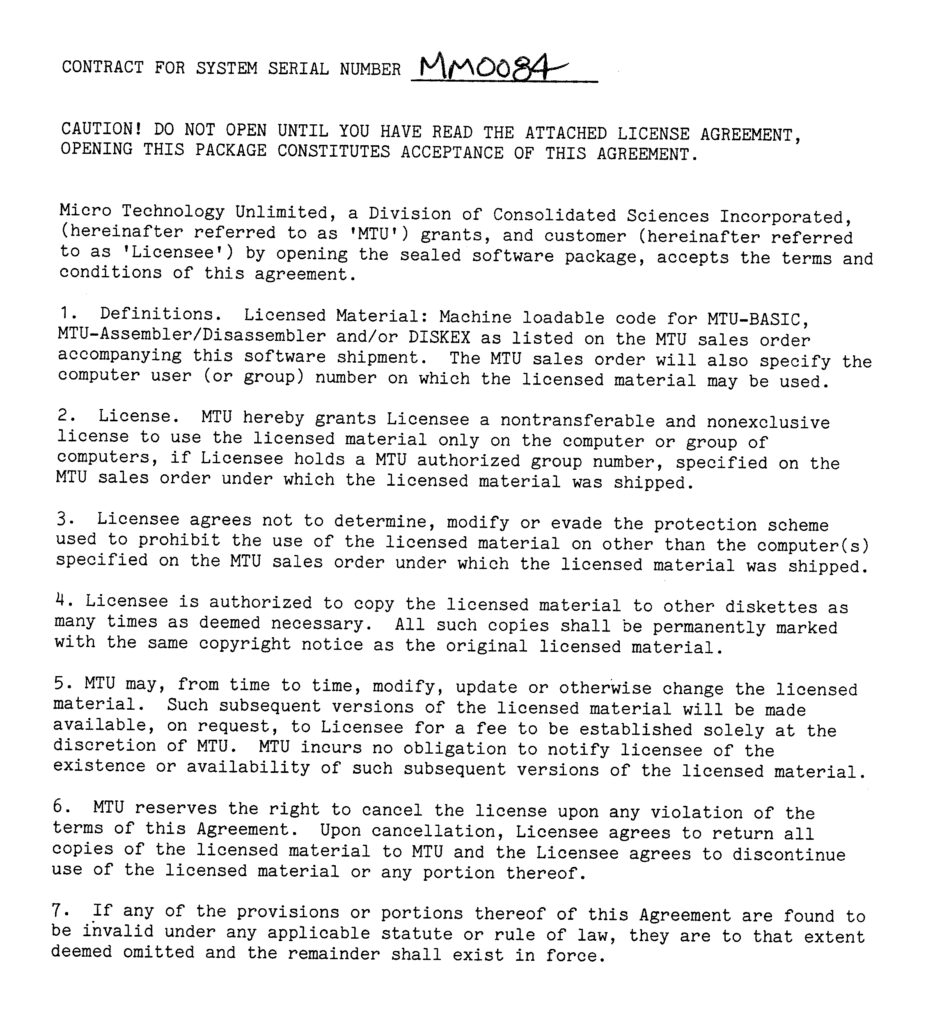

Manuals and documents

See also the other MTU pages.

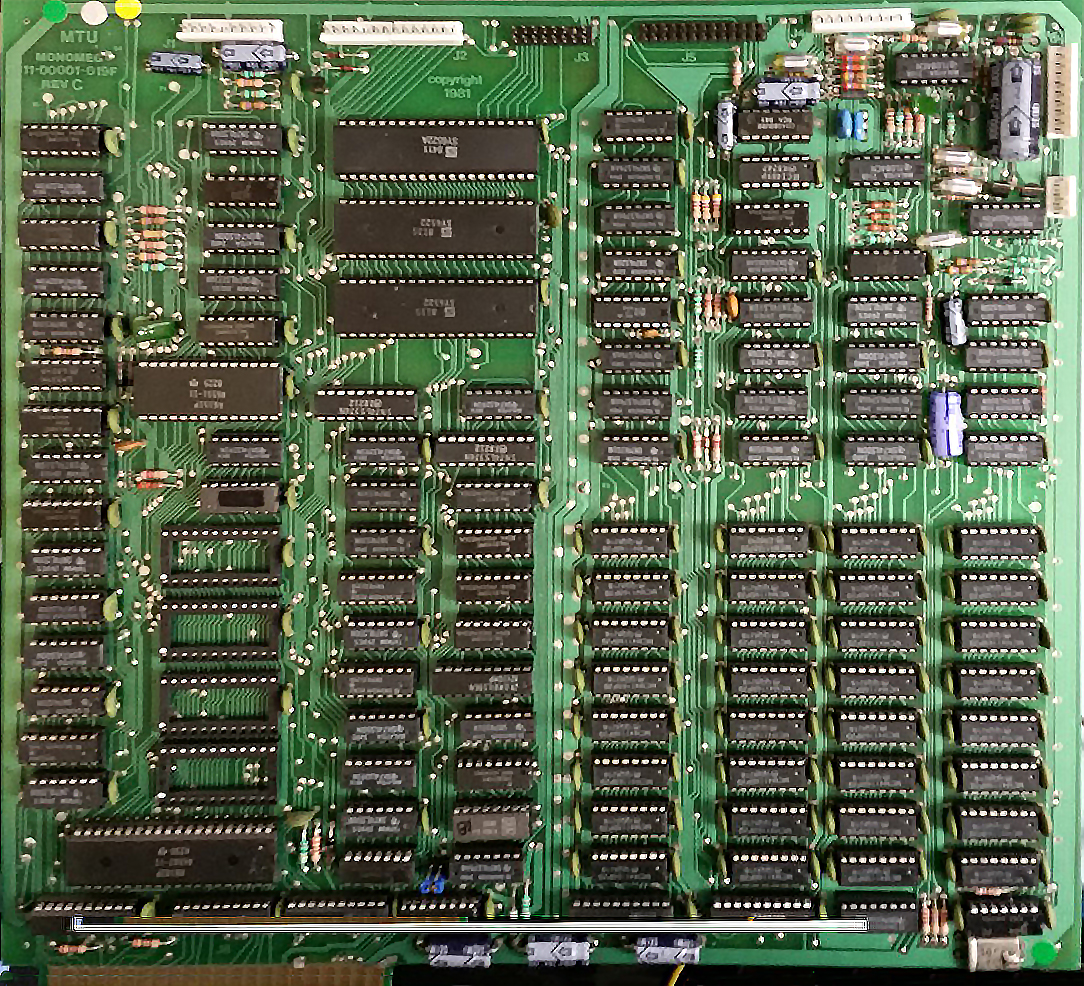

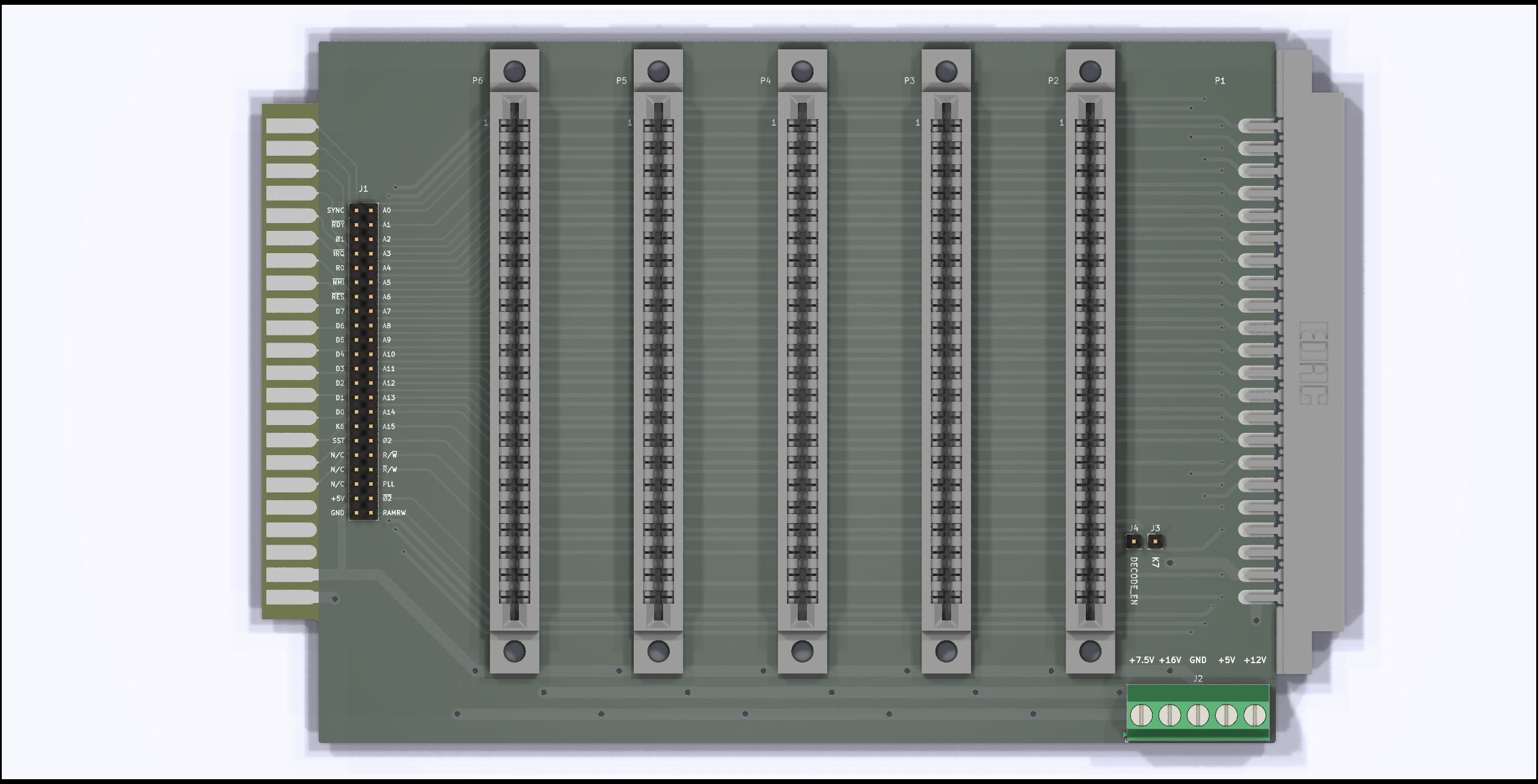

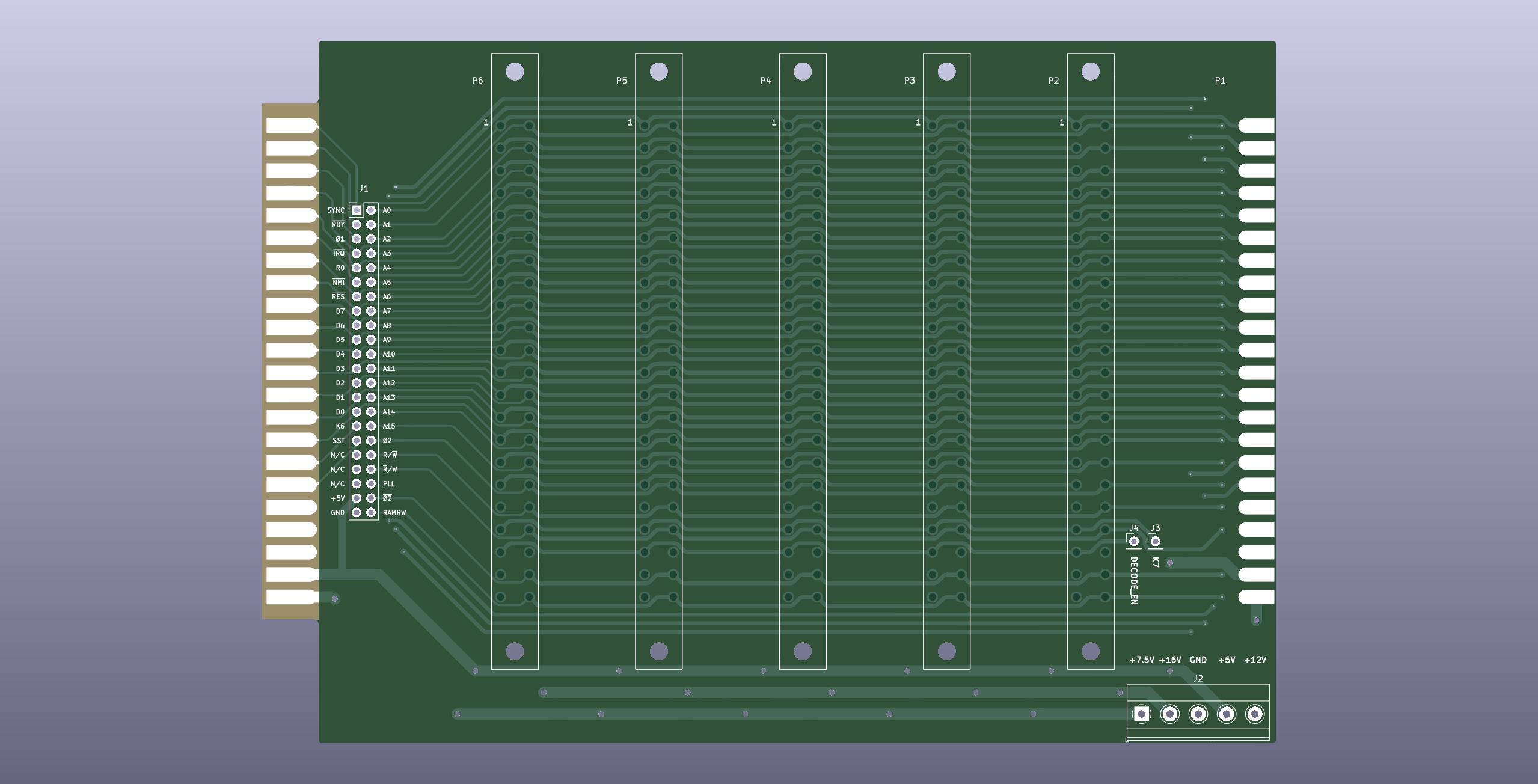

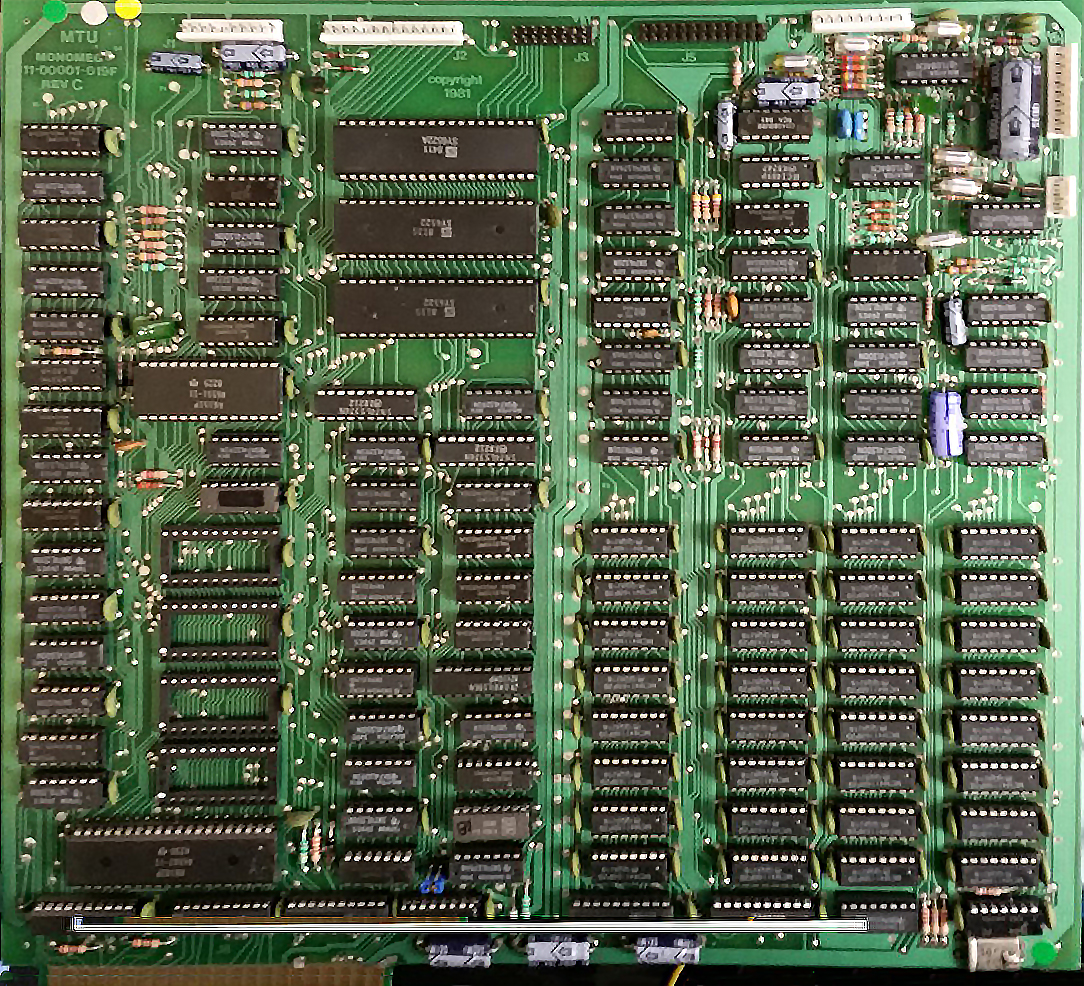

Monomeg CPU board

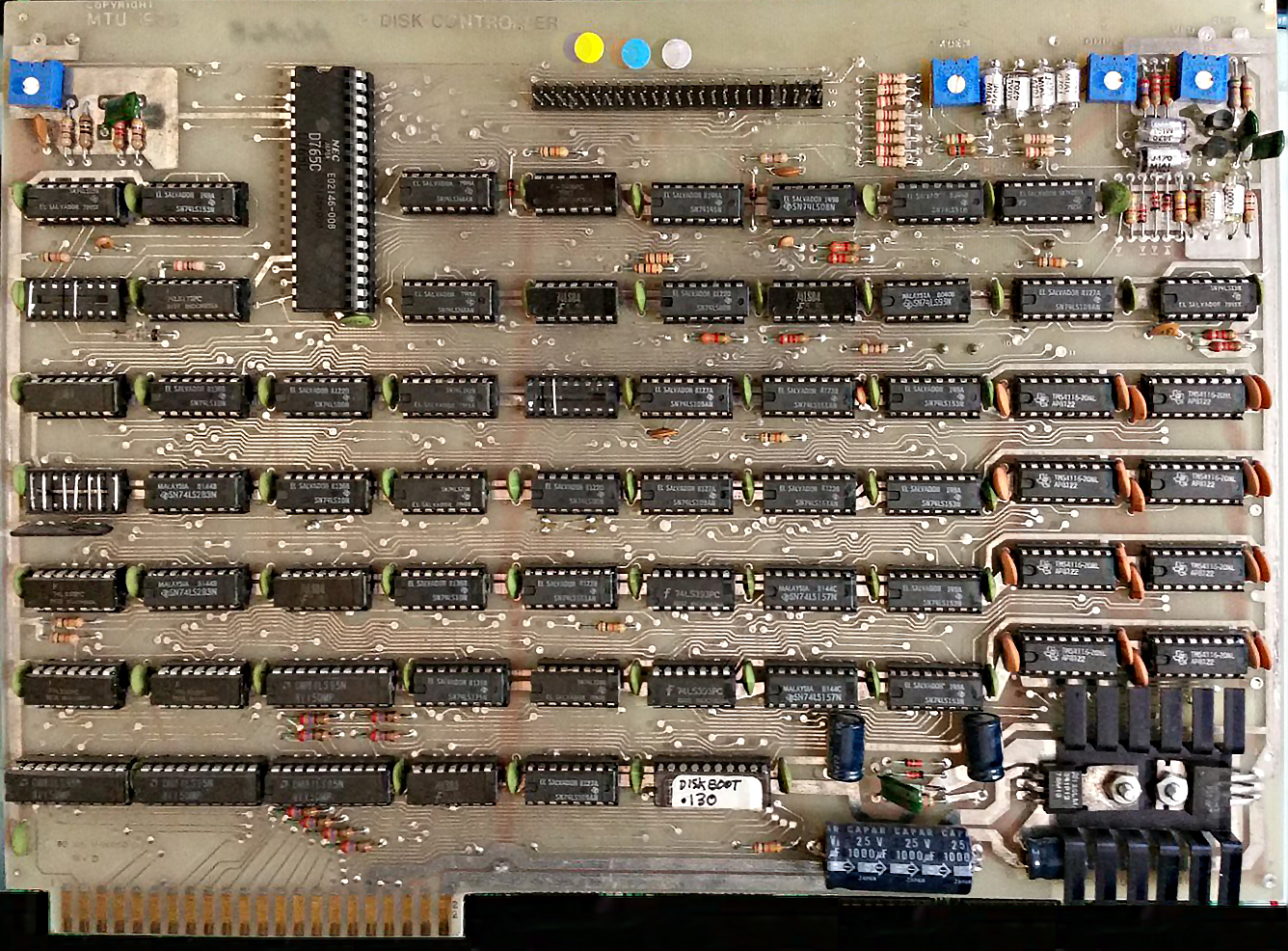

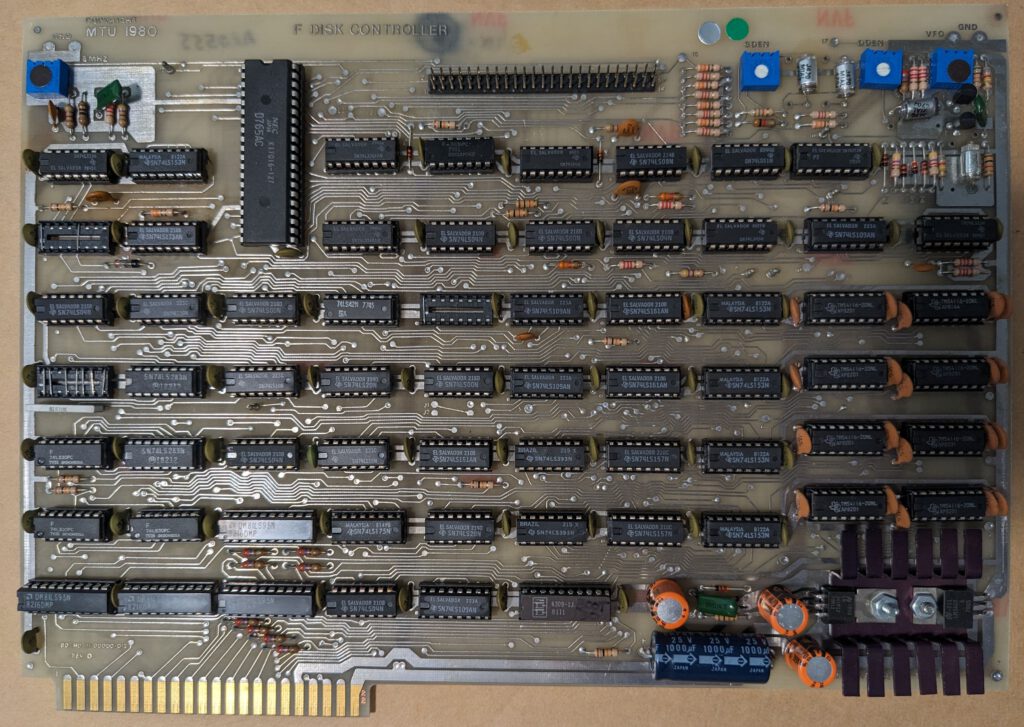

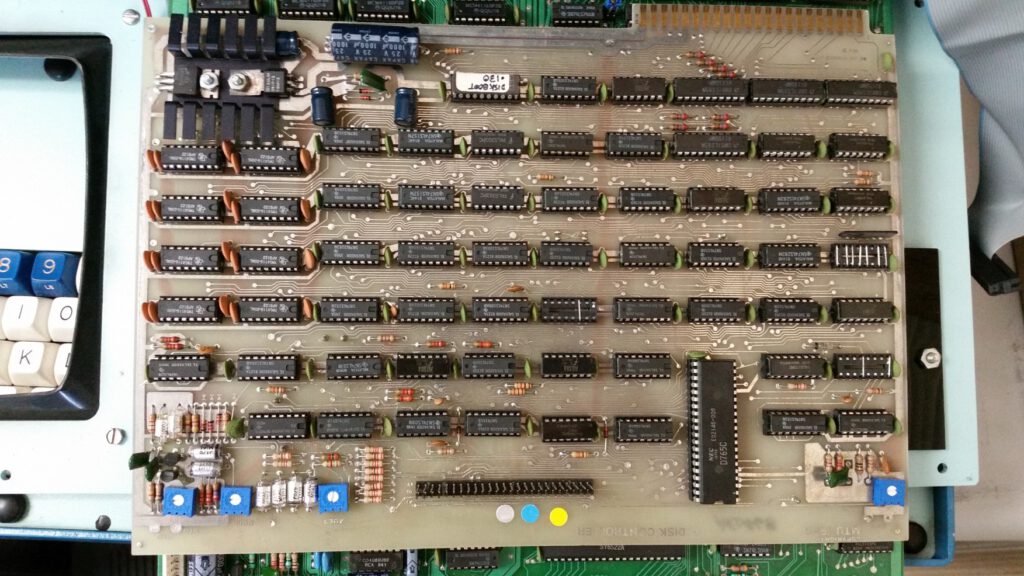

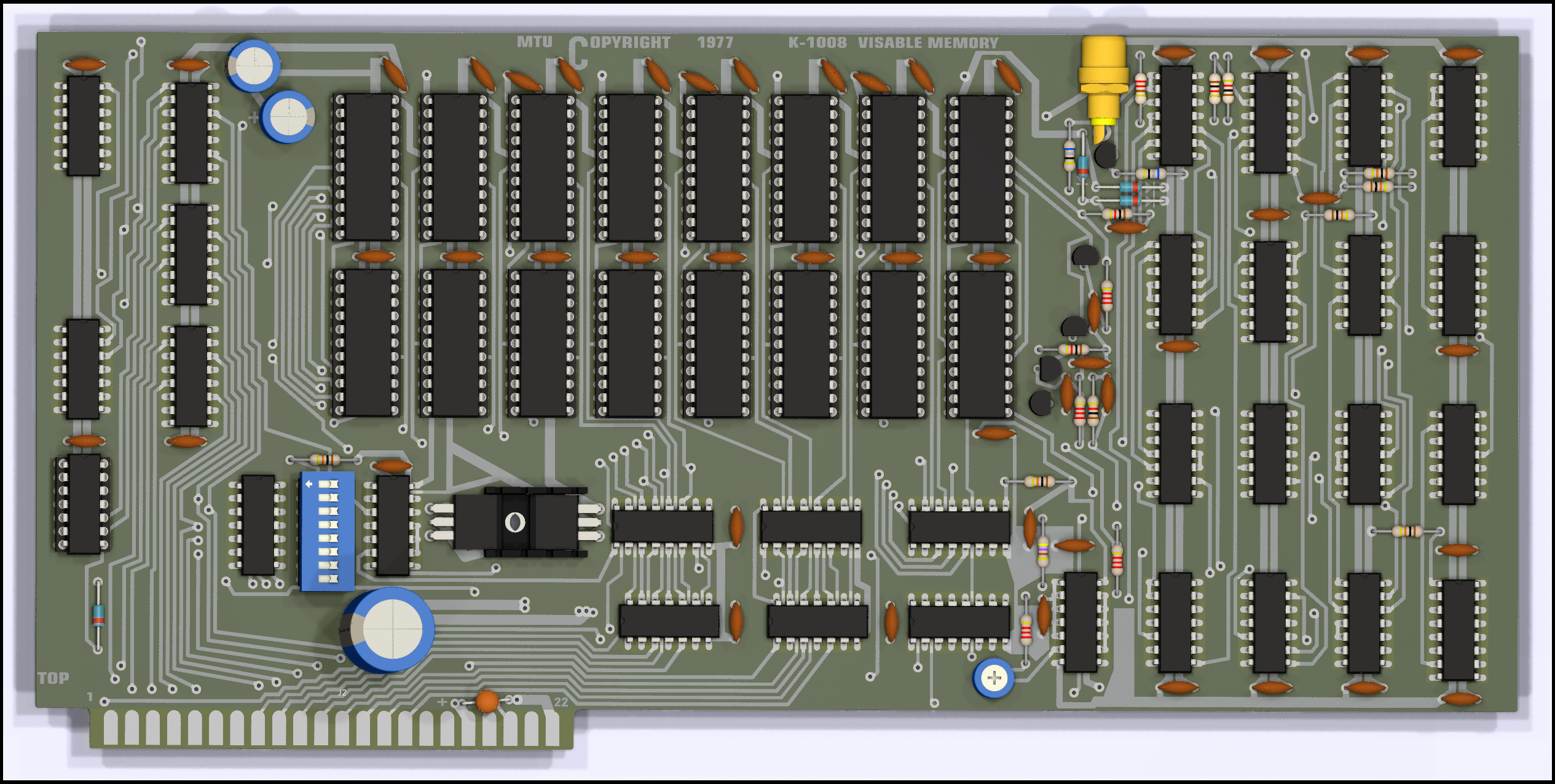

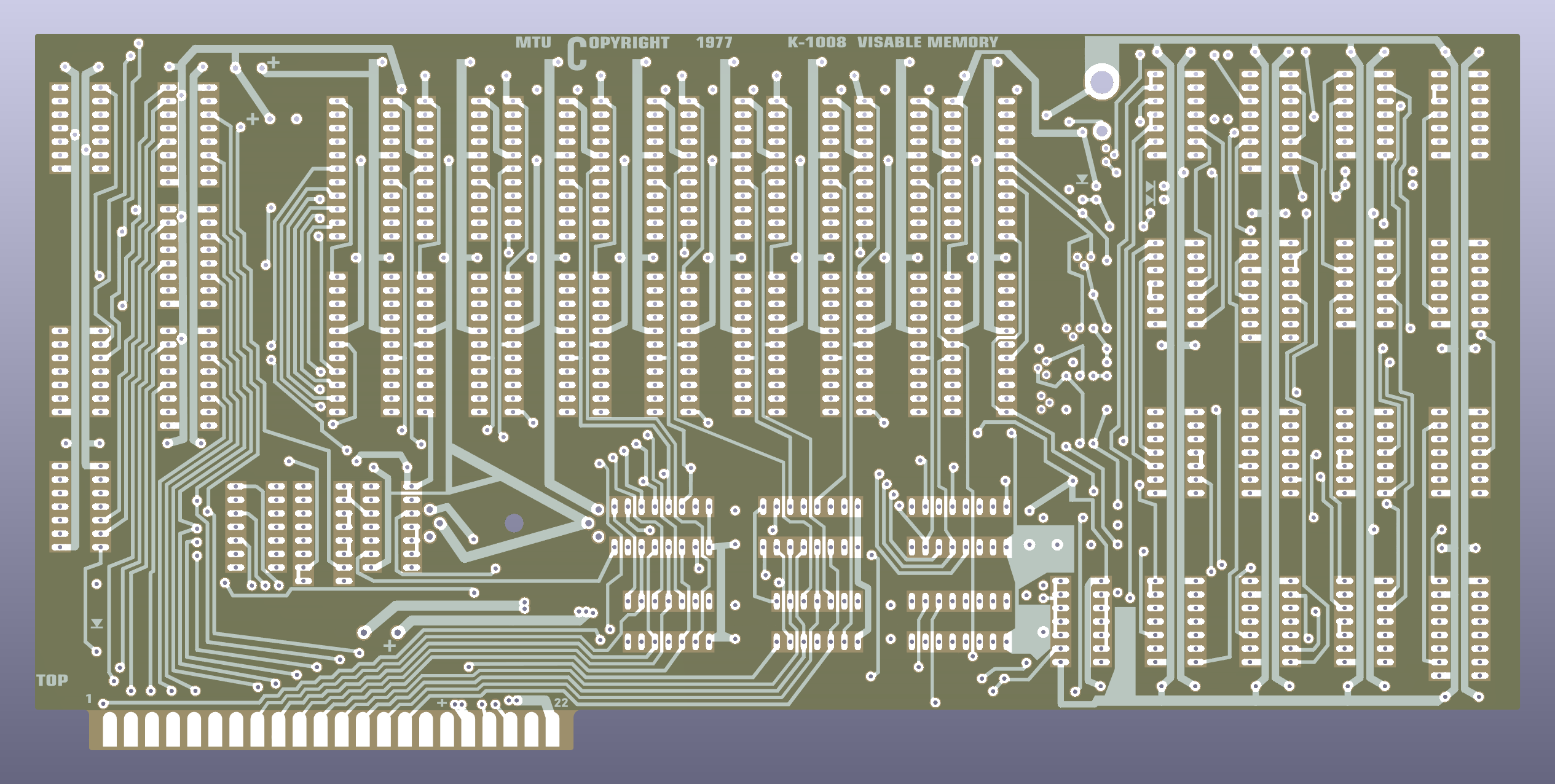

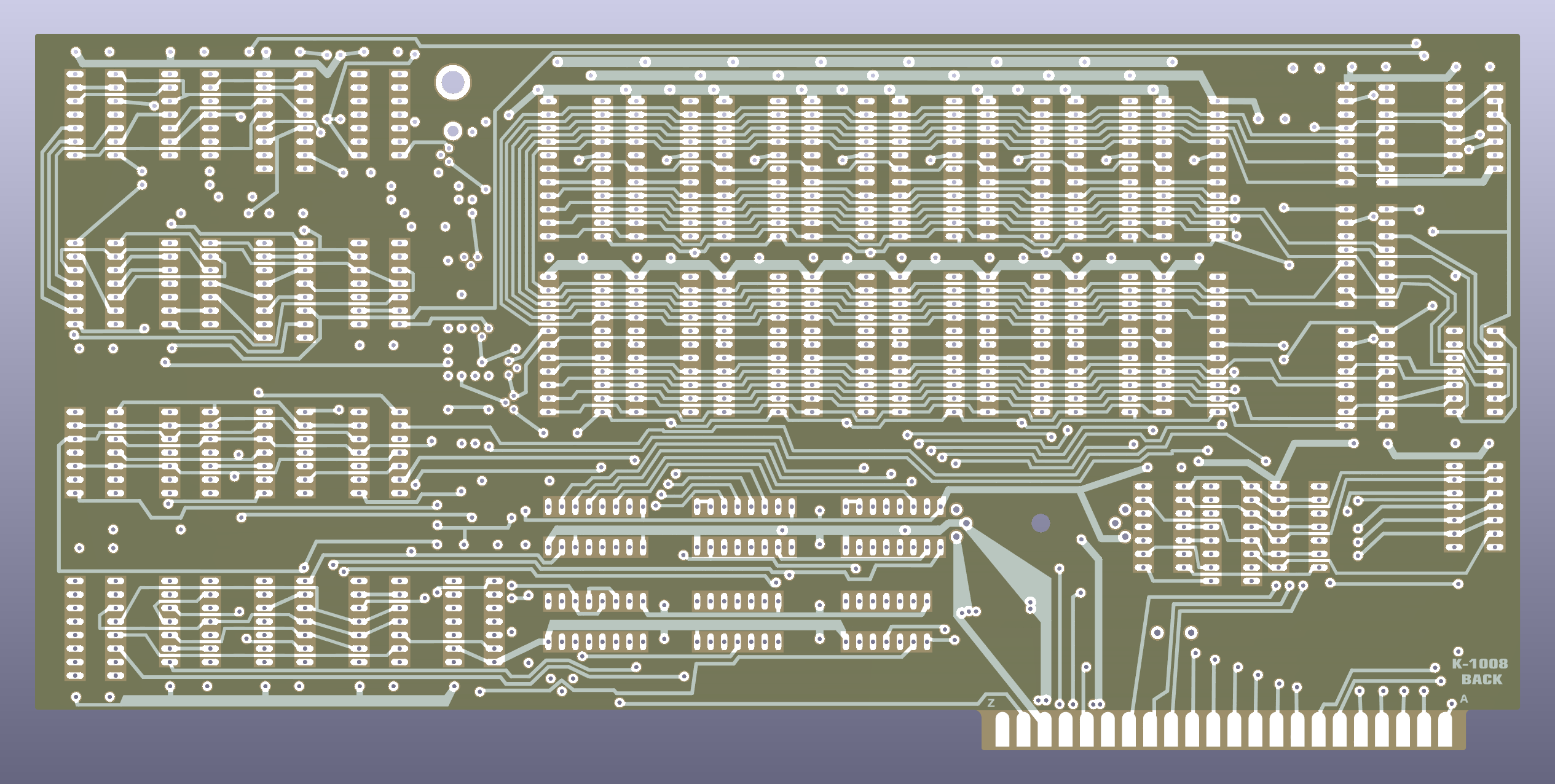

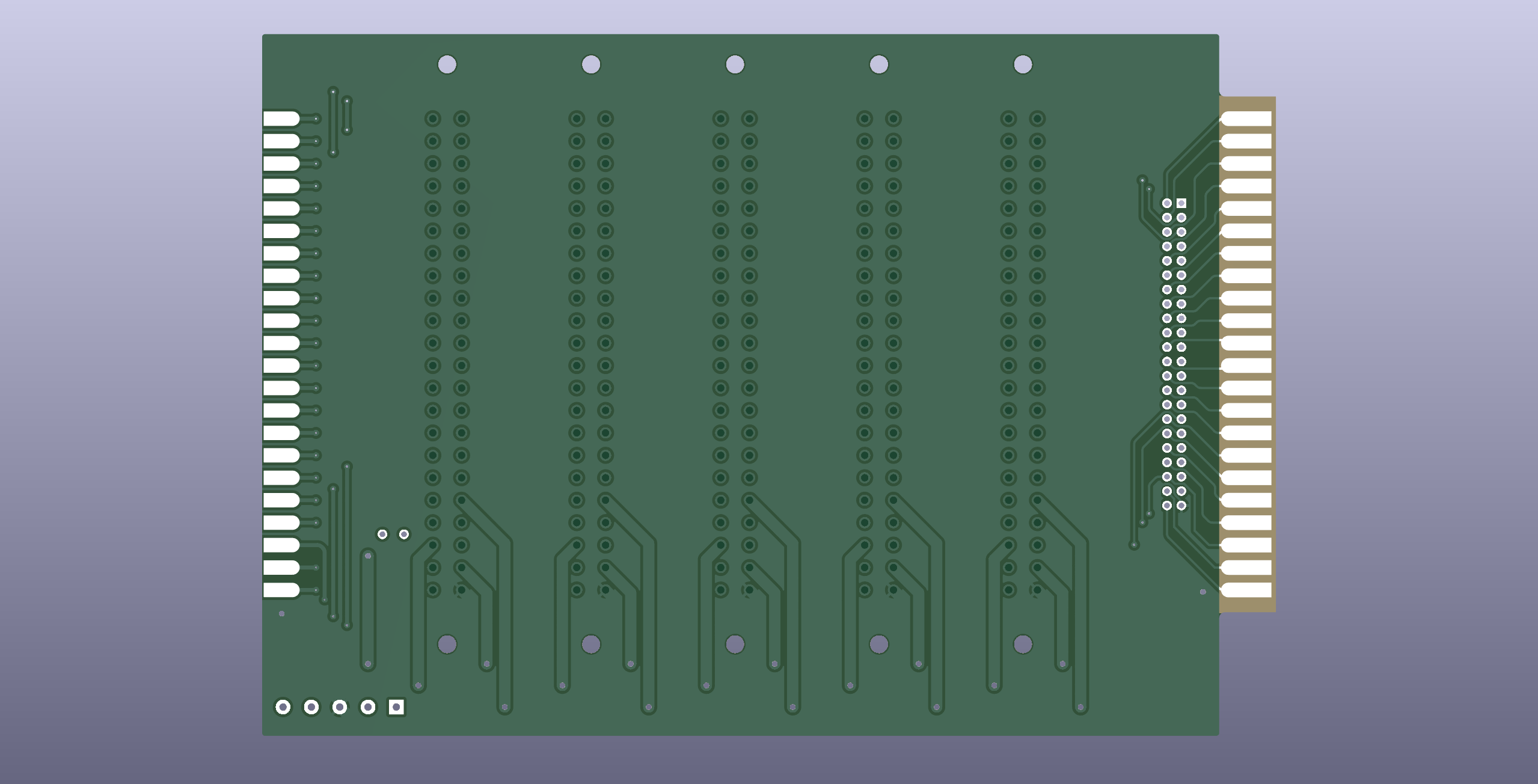

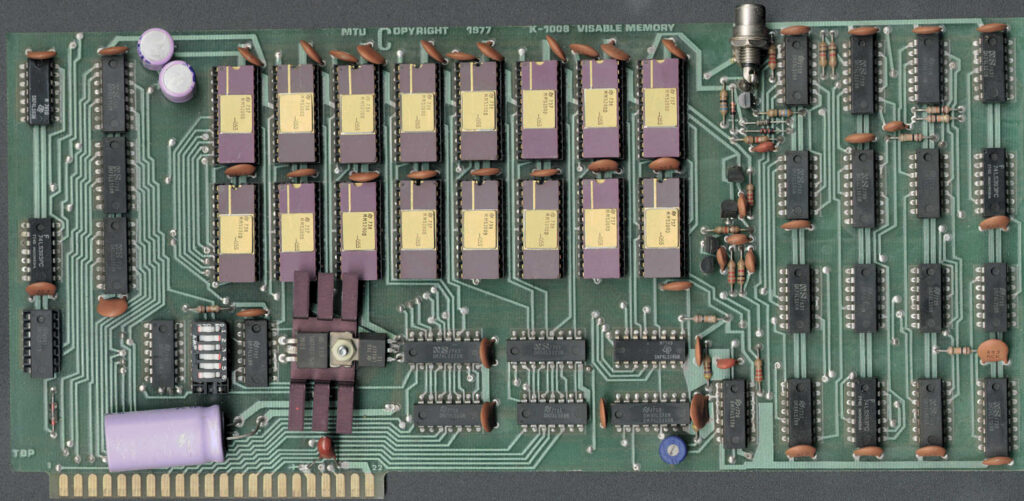

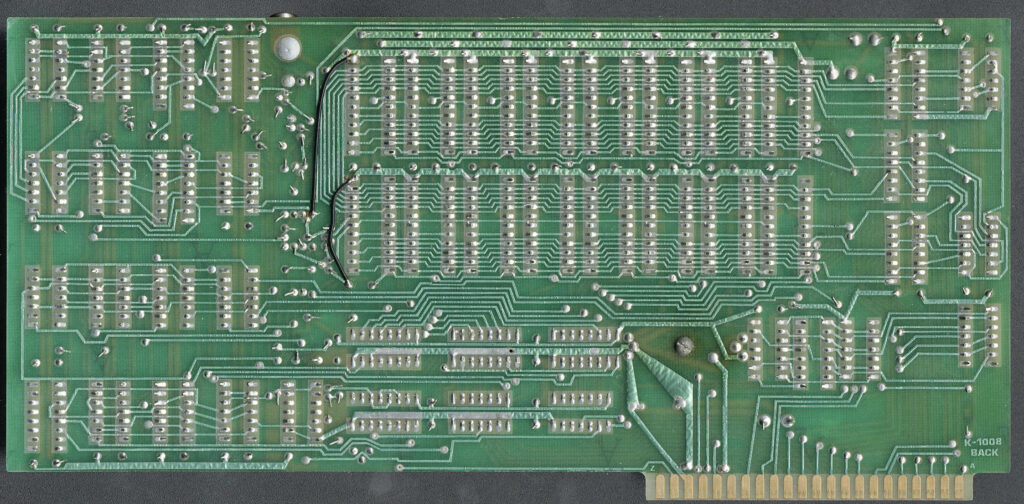

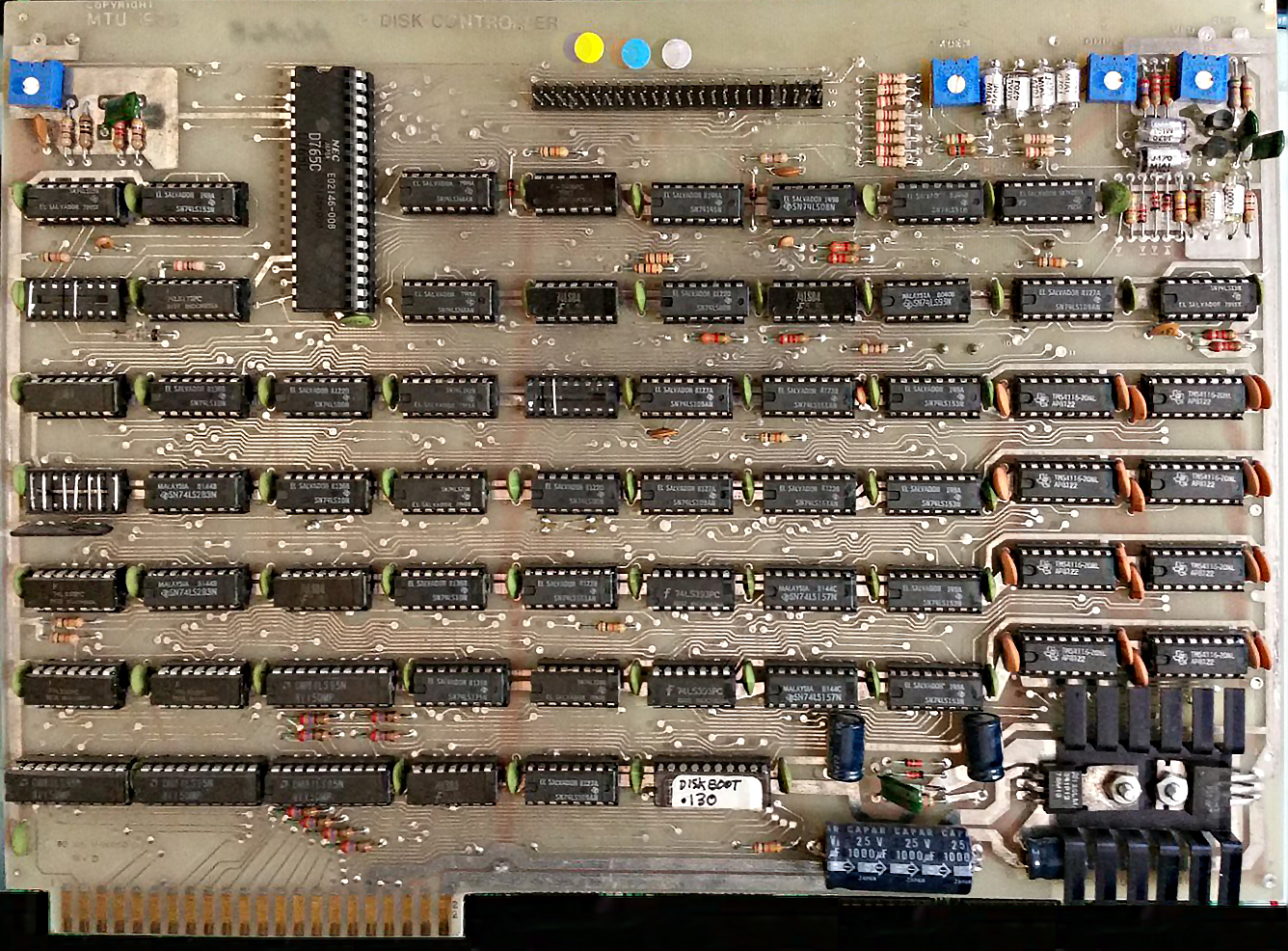

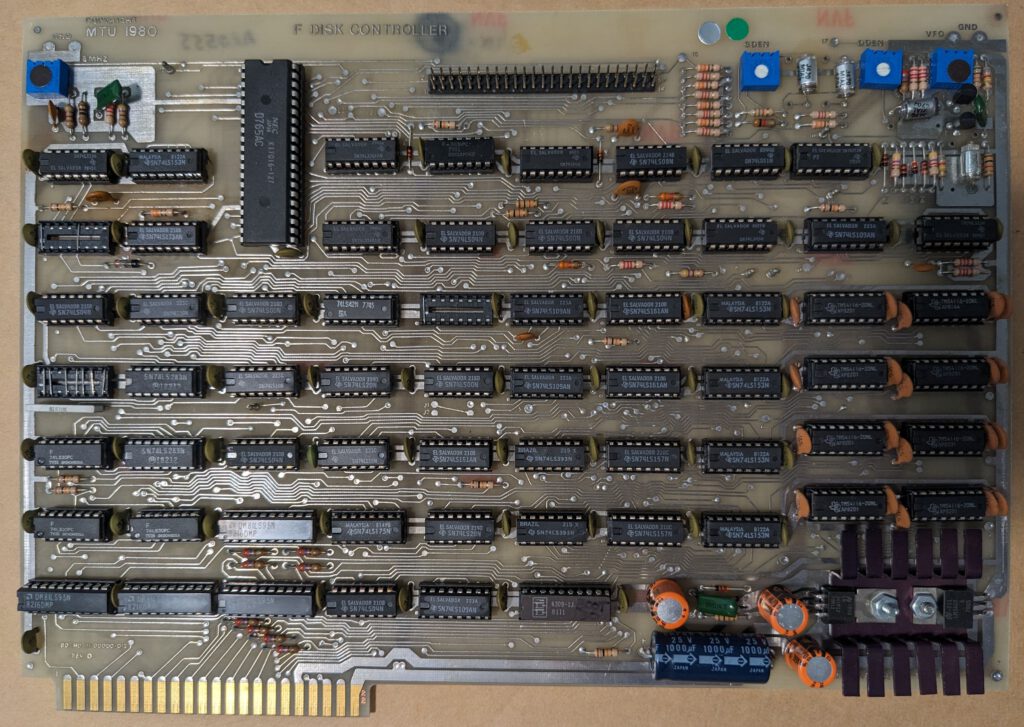

MT-130 floppy disk controller

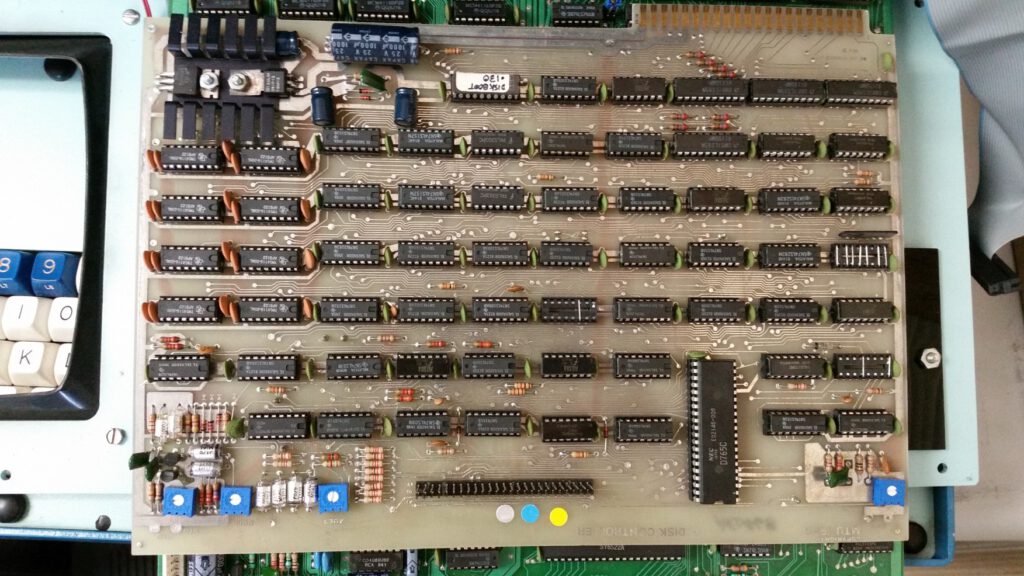

MTU-130 Disk controller front (Dave Williams)

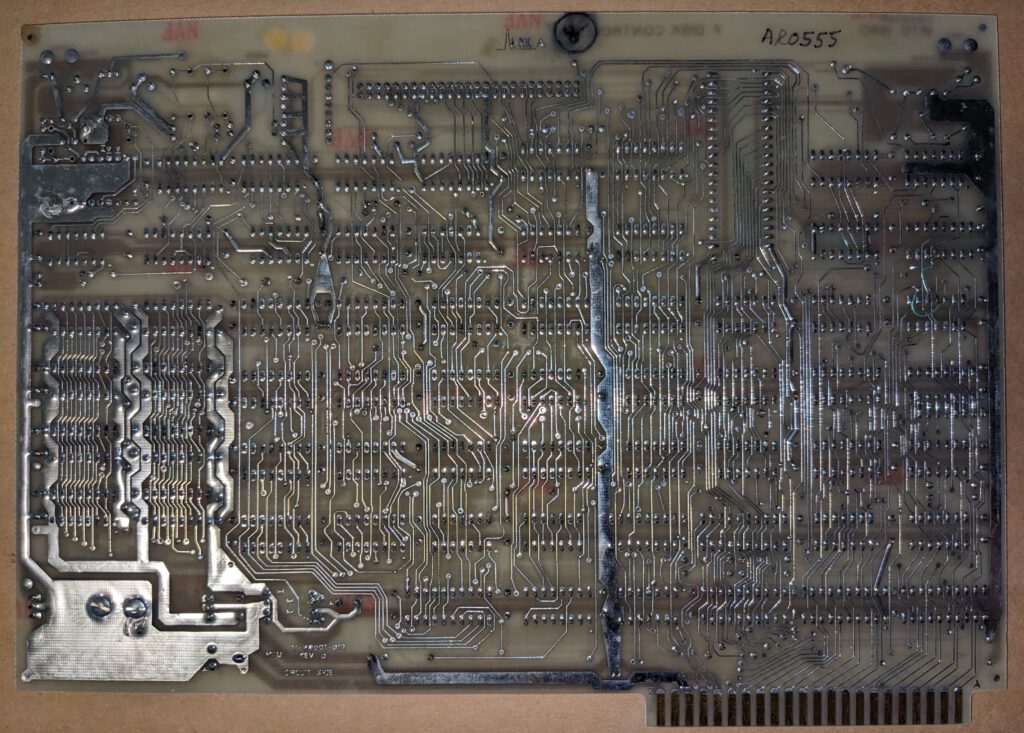

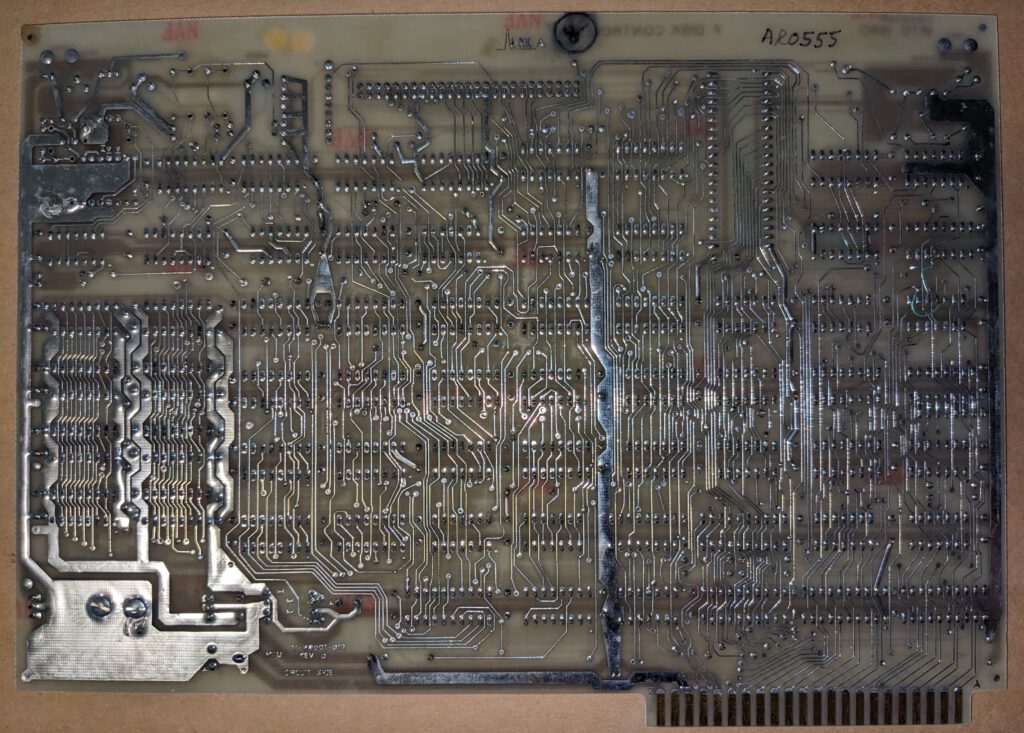

MTU-130 Disk controller back (Dave Williams

(Scans contributed by a.o. by Eric Wright, Dave Plummer and Dave Williams)

Accupath 1000

Original article by Eric Wright.

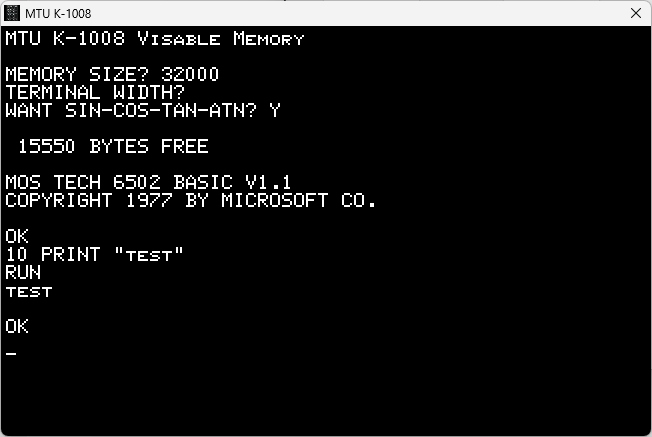

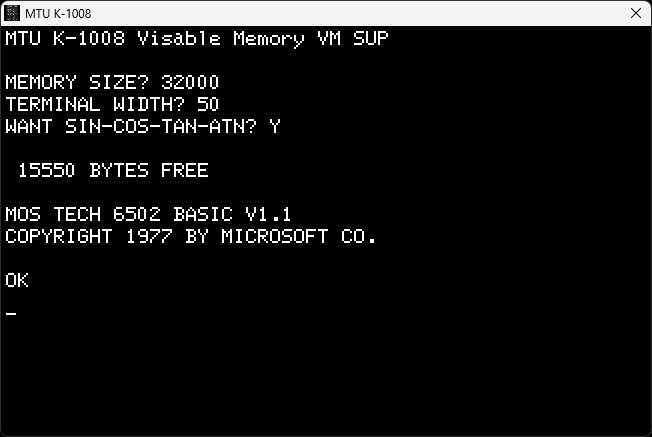

I (Eric) found this at the local ewaste recycler (eCyclers of Idaho in Idaho Falls, Idaho) and took it home since I was curious about it. I could find very little about the computer online other than it was some sort of “BS medical device”. After a few quick fixes (blown fuse and a wiring issue), I powered the machine on to see what all it would do…. and it didnt do much. It started to seek on the floppy drive and the monitor showed garbage.

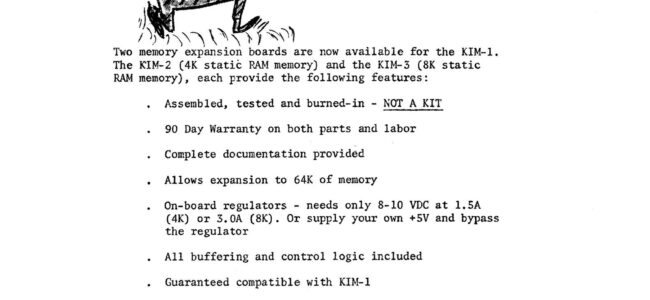

At this point, I decided to tear further in to the system. Inside, ther was a linear power supply, a monitor capable of displaying composite images, and two MTU boards. Doing a bit of searching on these two boards, I was able to determine that they came from an MTU-130 system. The main board is what MTU called “monomeg”, it was a neat 6502 based board featuring 80kb of RAM. One interesting thing that I read, is that this board has some sort of extended 18bit address bus allowing up to 256K of address space.

The boot ROM has been dumped

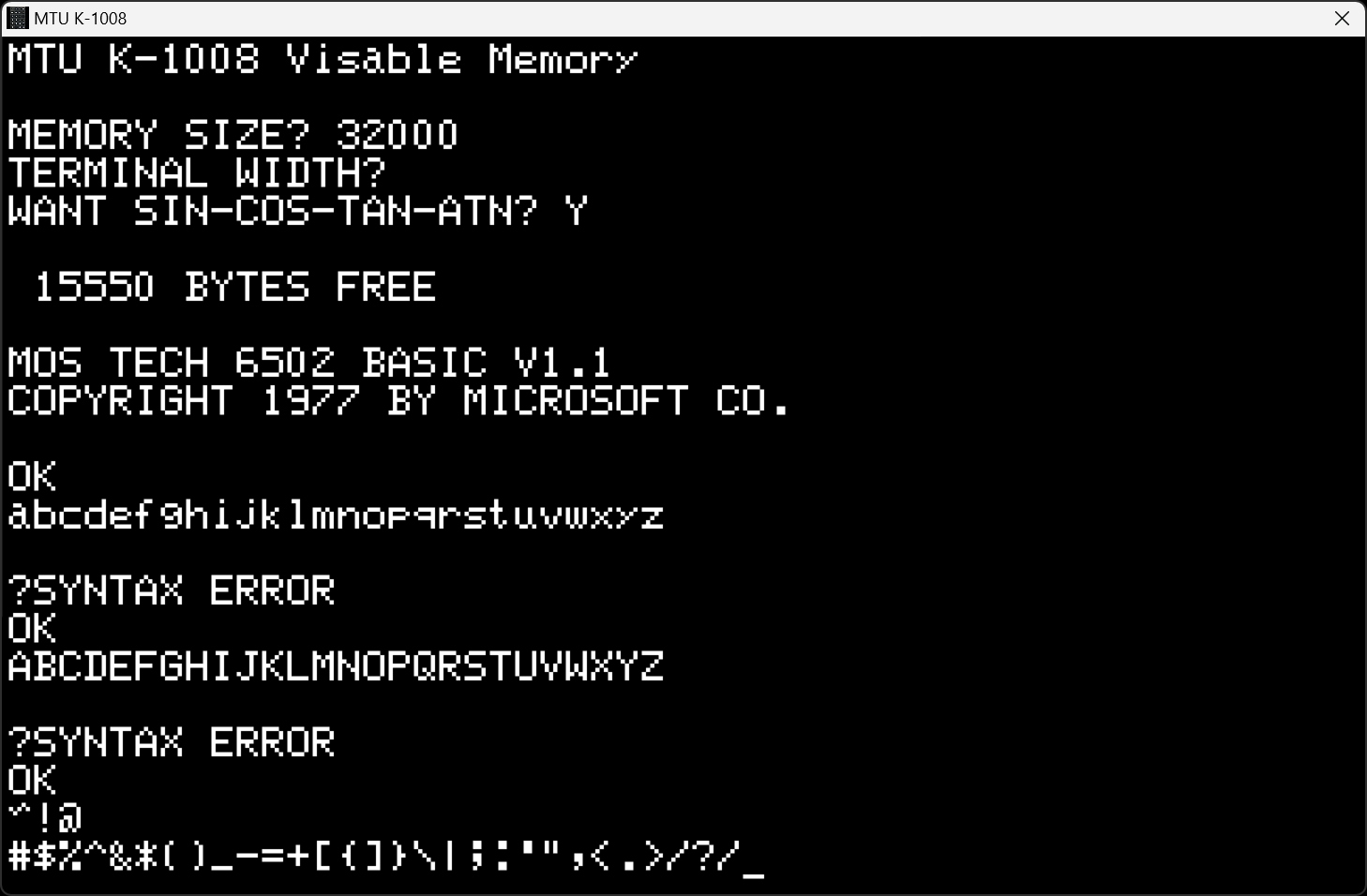

Judging from a quick look, it appears it is talking with the 765 floppy controller ia $FFE8-$FFEF. I will look at the floppy controller board and see if i can figure out how they have it mapped.

Some more info by Eric Wright Here is a little more information about the setup inside of the Accupath 1000:

There are three ROMs between the main board and floppy controller board. both of the ROMs on the main board are used as decoders (256×4, MMI6301) from what I can tell, while the ROM on the floppy drive controller (256×8) actually bootstraps the system.

During boot strap, nothing is show on the screen (they only have 256 bytes afterall) except the current RAM contents that the video system is using. The ROM seeks an image off of the floppy drive, loads it to RAM, and jumps to it. I will get this ROM dumped and disassembled soon.

The floppy disk drive is a Qume Qumetrak 542. After disassembling the ROM, I hope to be able to load some sort of monitor via floppy disk.

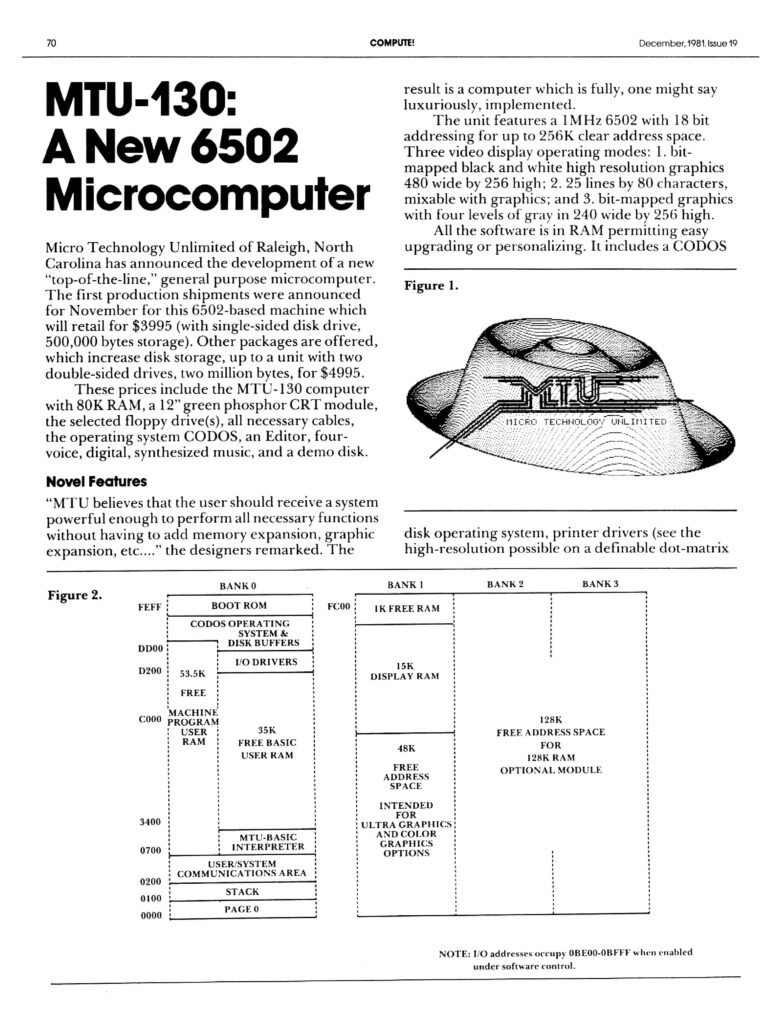

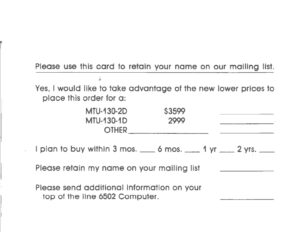

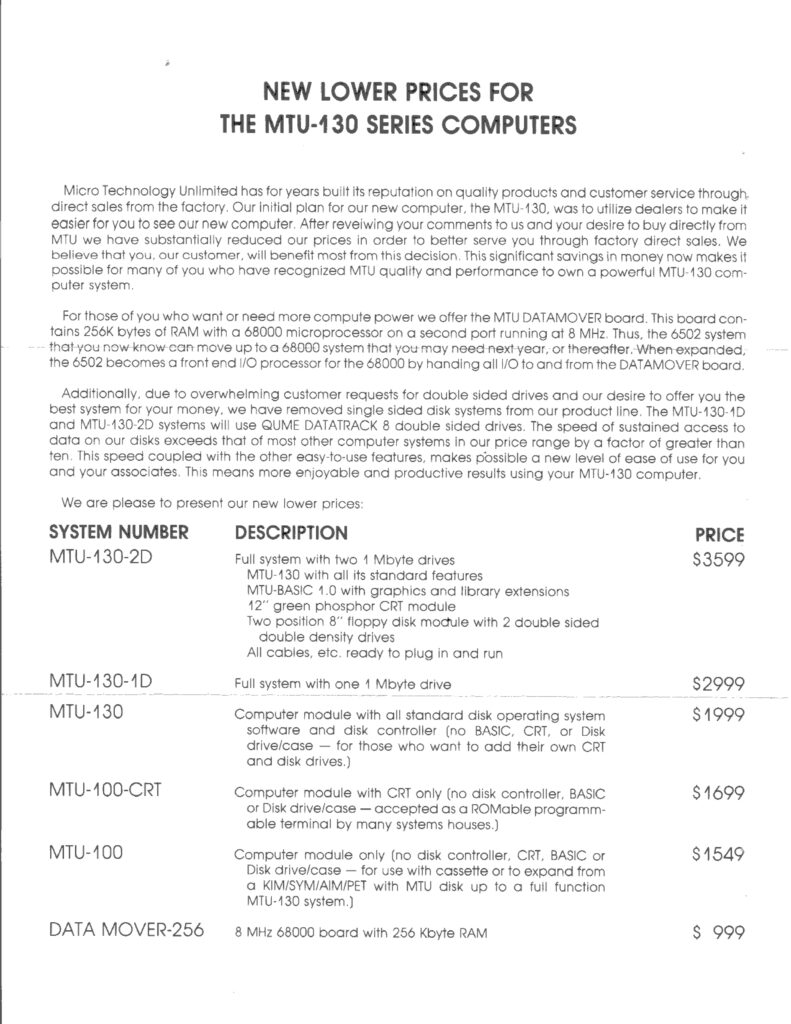

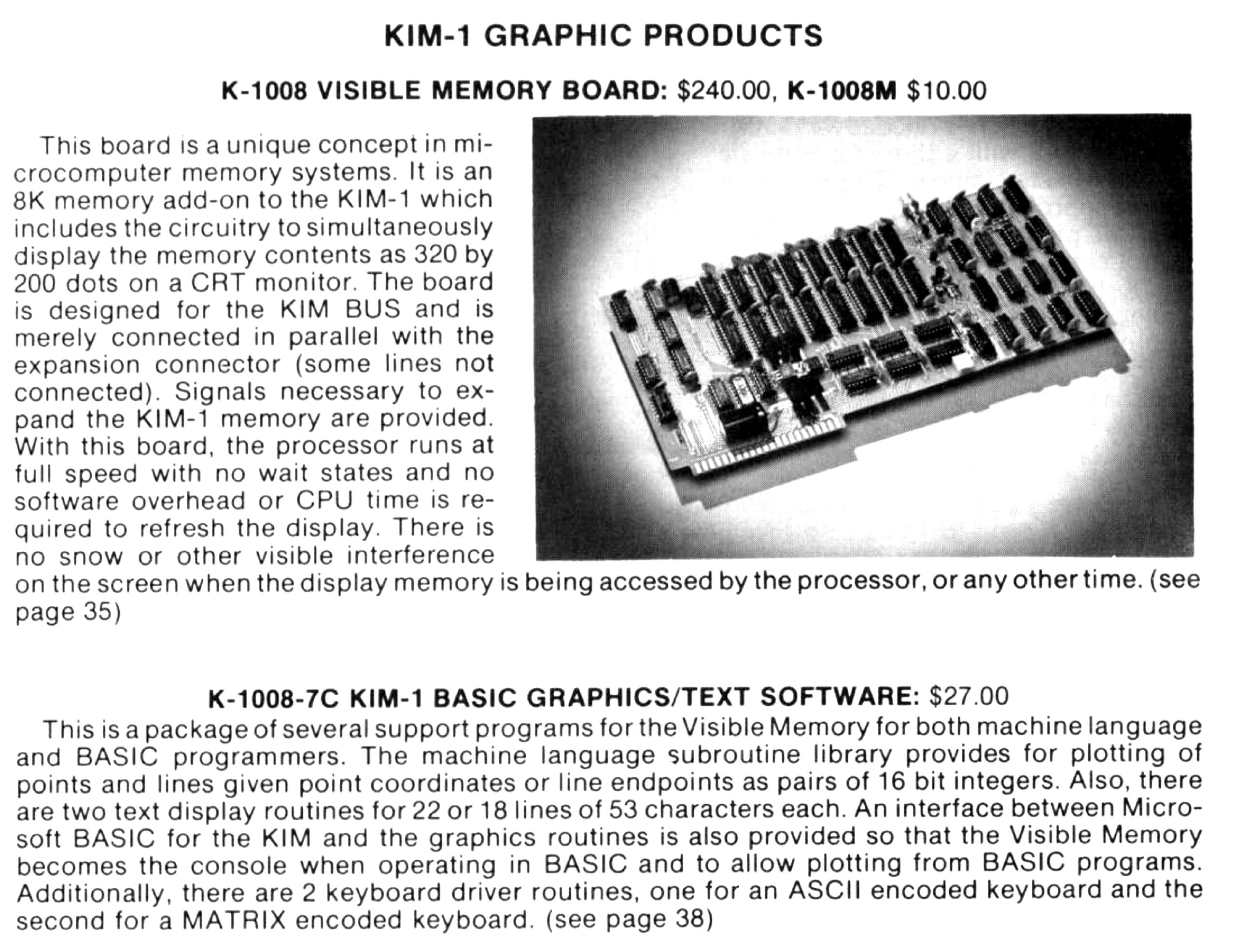

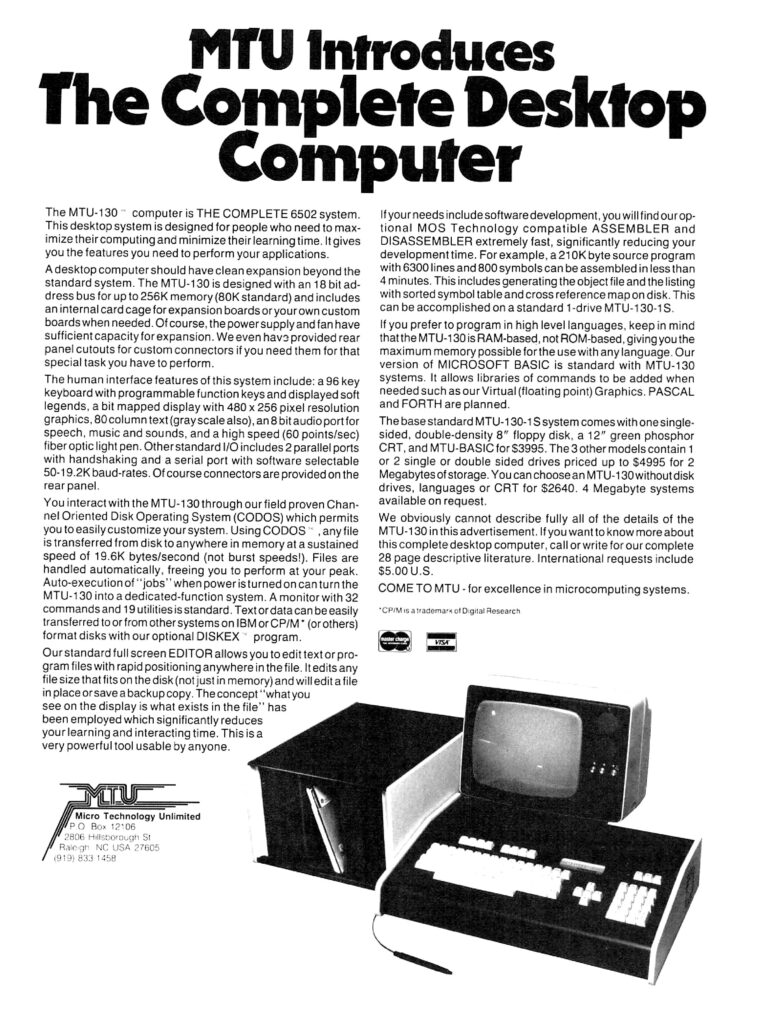

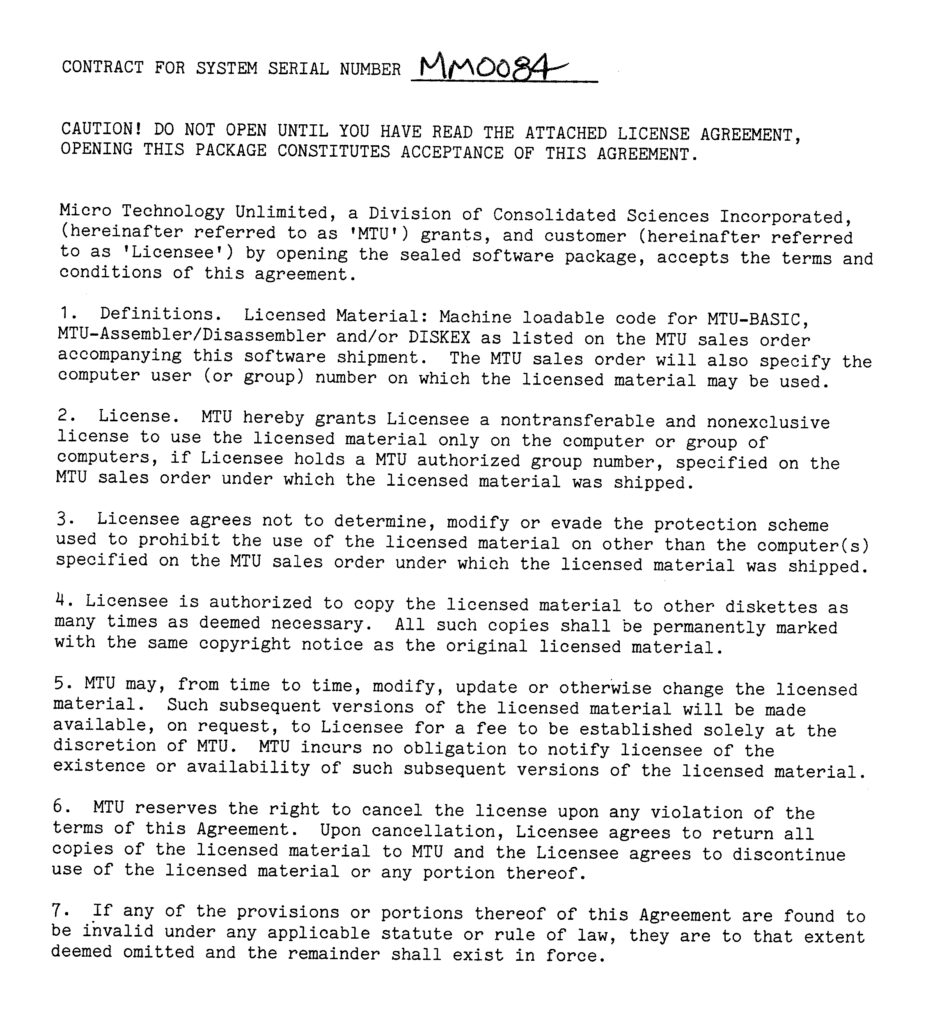

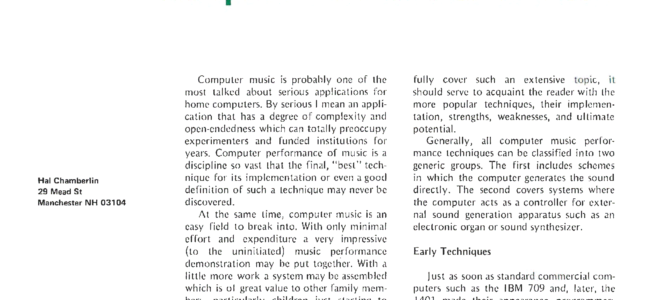

From COMPUTE! Issue 19 December1981

MTU-130: A New 6502 Microcomputer

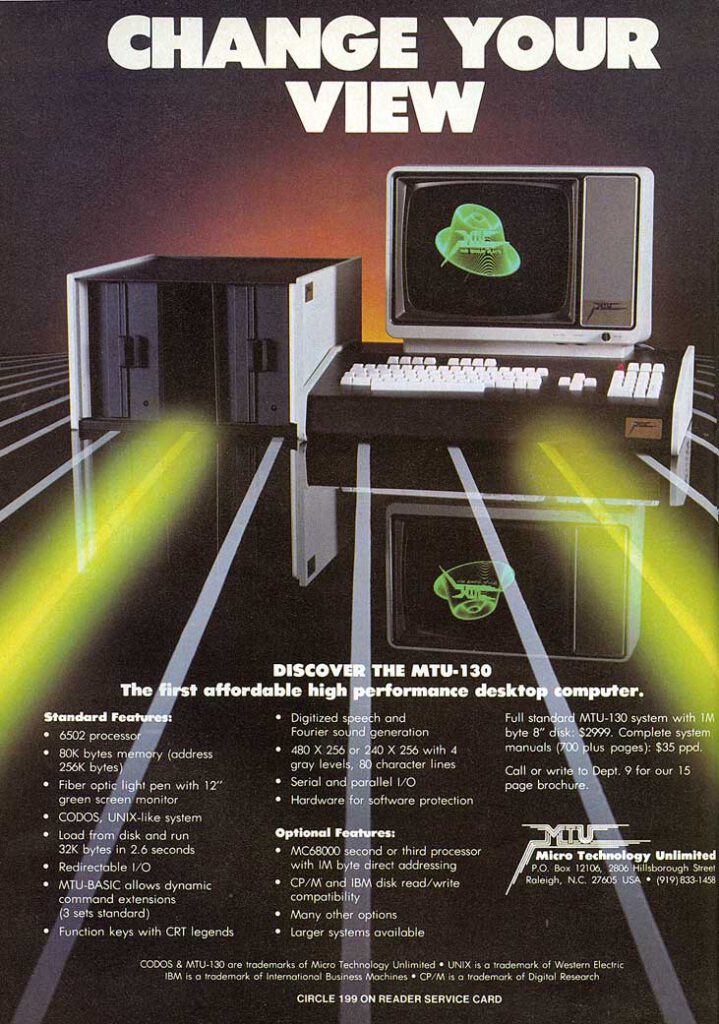

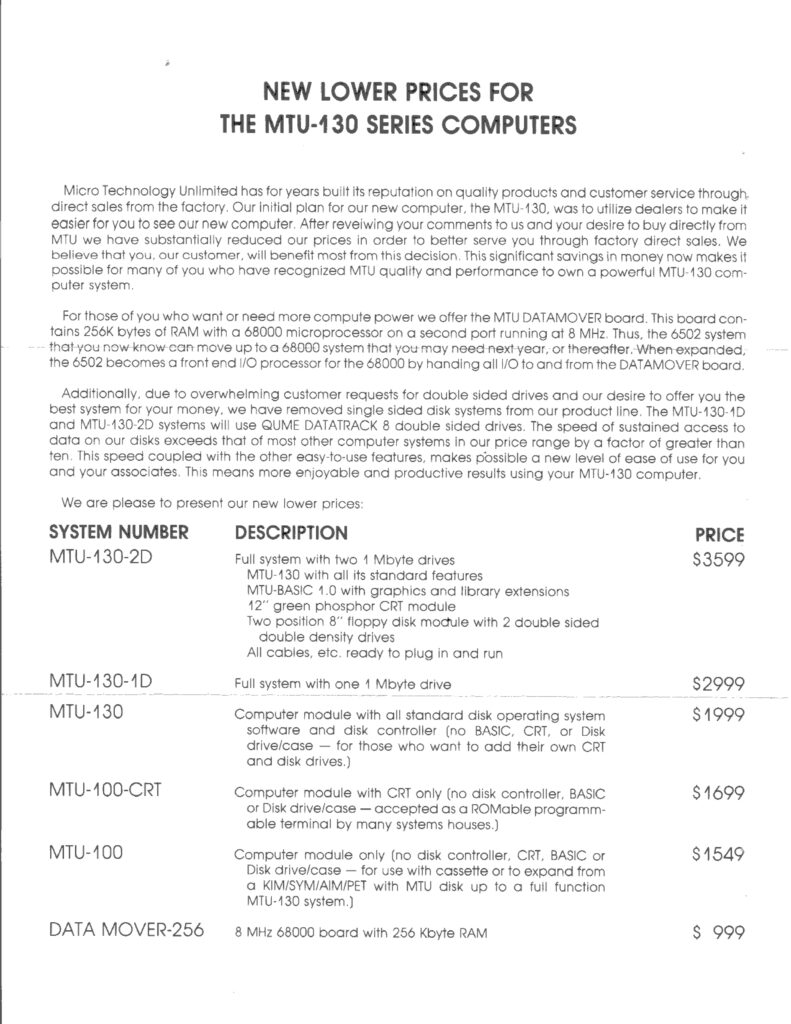

Micro Technology Unlimited of Raleigh, North Carolina has announced the development of a new “top-of-the-line,” general purpose microcomputer. The first production shipments were announced for November for this 6502-based machine which will retail for $3995 (with single-sided disk drive, 500,000 bytes storage). Other packages are offered, which increase disk storage, up to a unit with two double-sided drives, two million bytes, for $4995. These prices include the MTU-130 computer with 80K RAM, a 12″ green phosphor CRT module, the selected floppy drive(s), all necessary cables, the operating system CODOS, an Editor, four-voice, digital, synthesized music, and a demo disk.

Novel Features

“MTU believes that the user should receive a system powerful enough to perform all necessary functions without having to add memory expansion, graphic expansion, etc. . . .” the designers remarked. The result is a computer which is fully, one might say luxuriously, implemented.

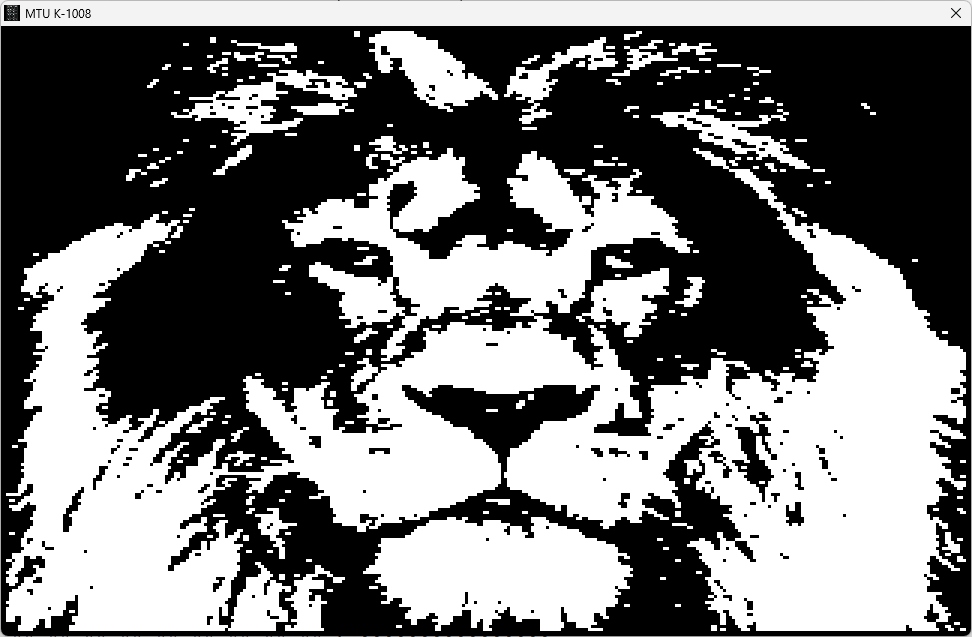

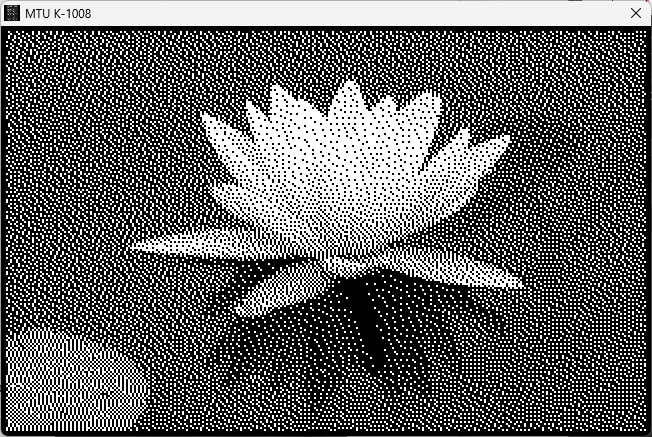

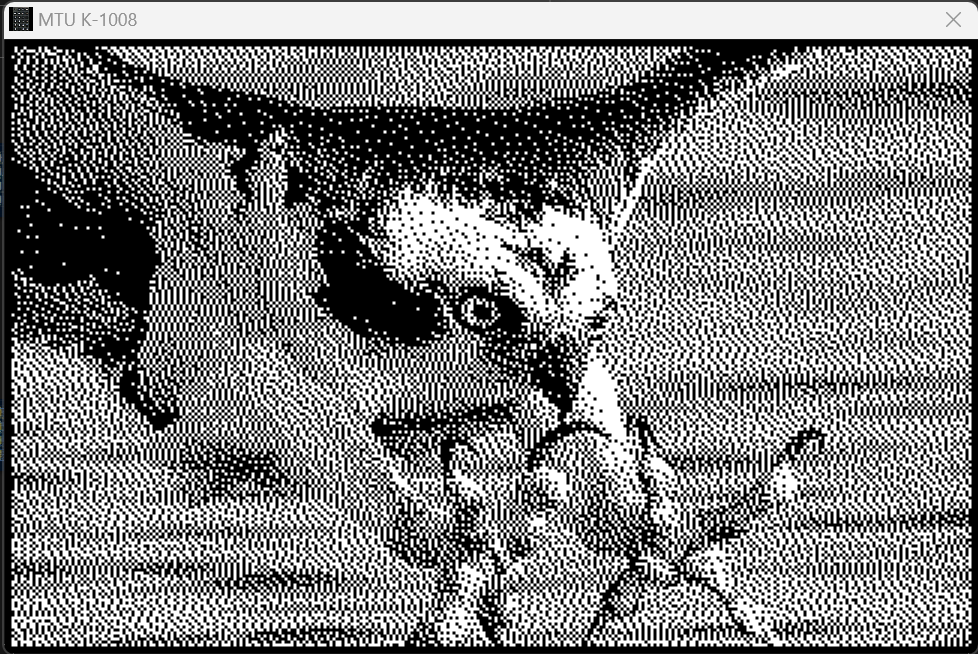

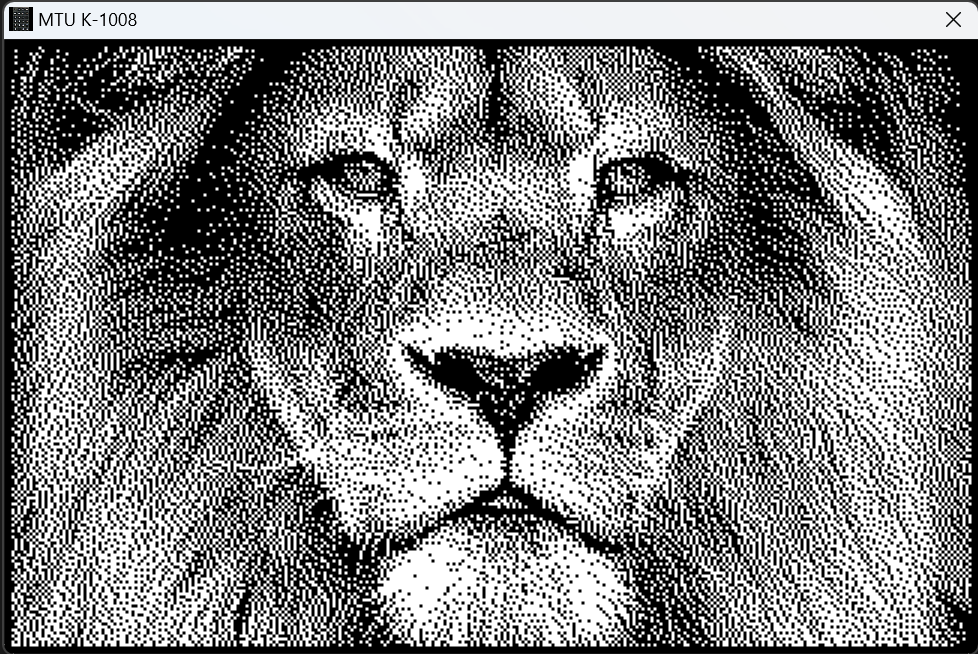

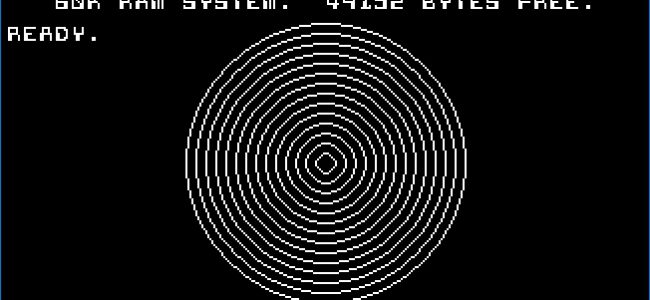

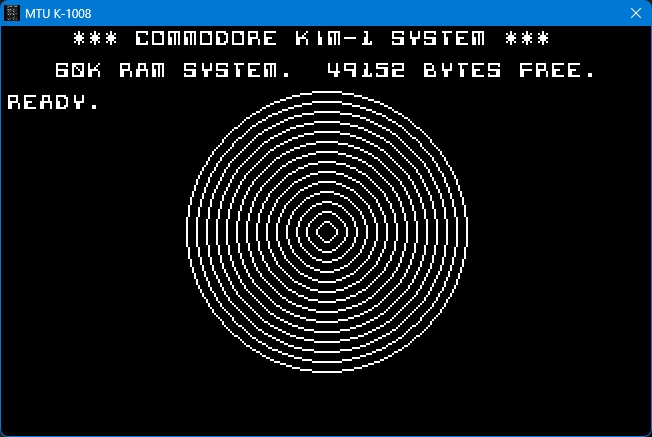

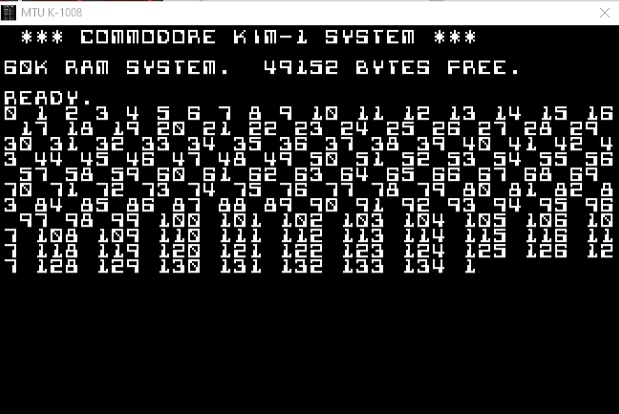

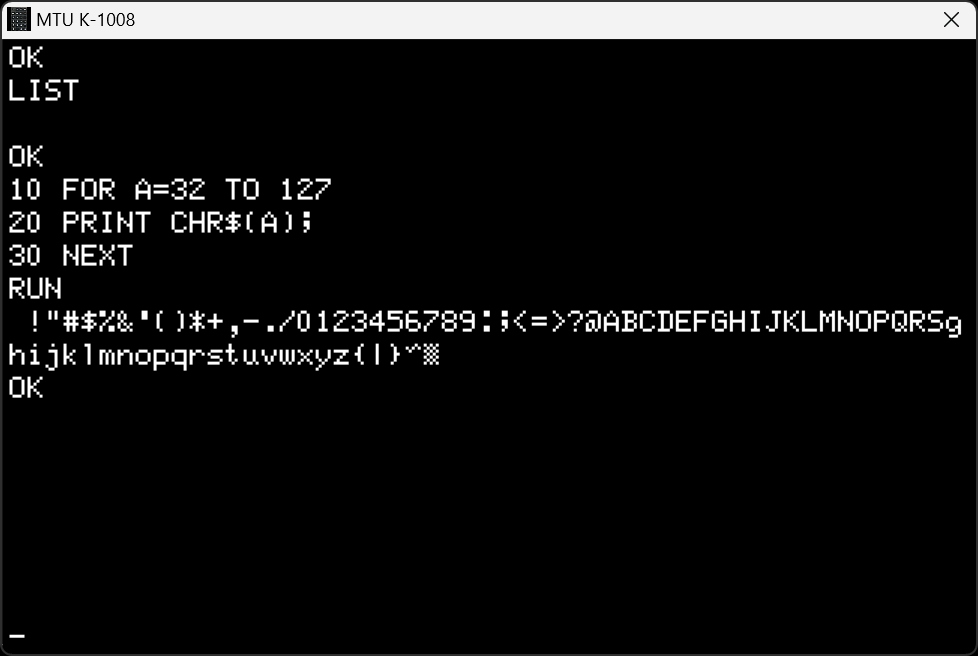

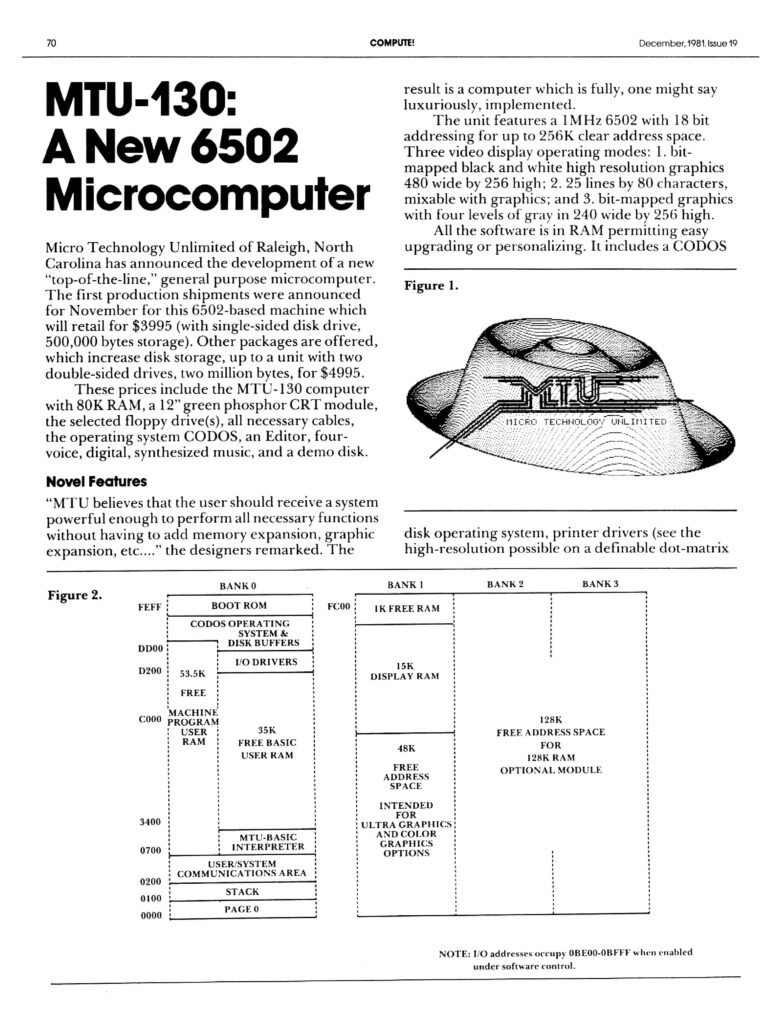

The unit features a 1 MHz 6502 with 18 bit addressing for up to 256K clear address space. Three video display operating modes: 1. bit-mapped black and white high resolution graphics 480 wide by 256 high; 2. 25 lines by 80 characters, mixable with graphics; and 3. bit-mapped graphics with four levels of gray in 240 wide by 256 high.

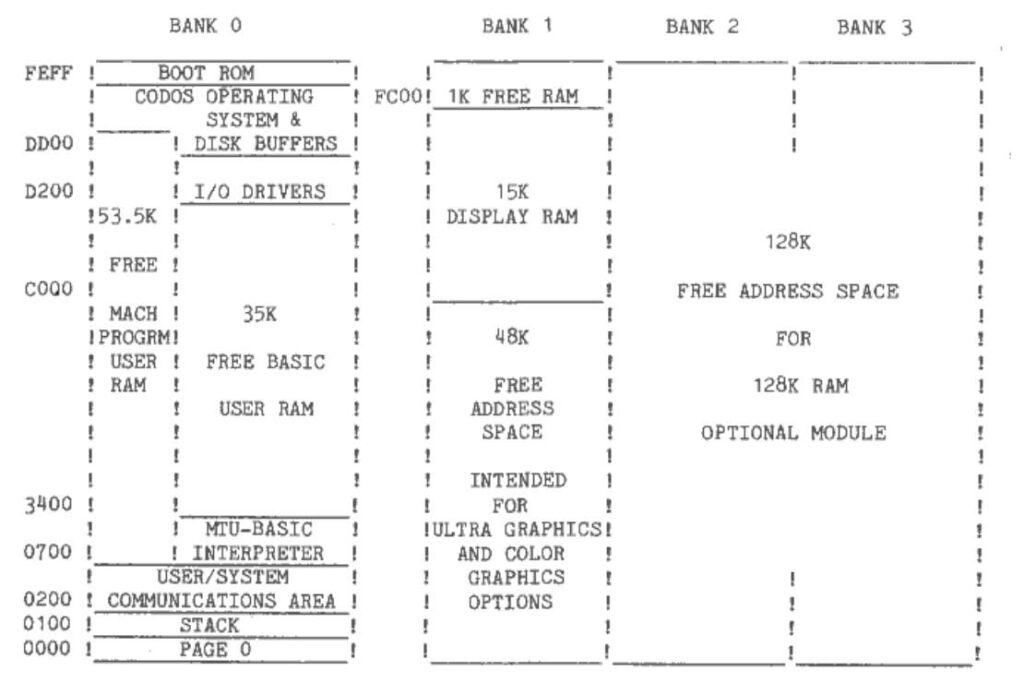

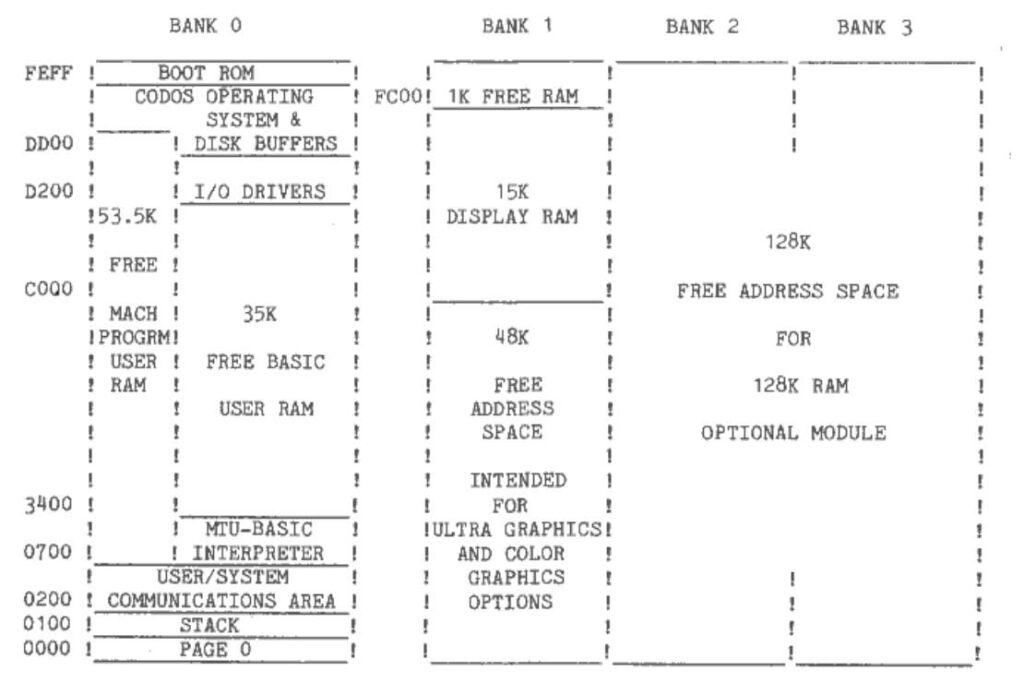

NOTE: I/O addresses occupy 0BE00-0BFFF when enabled under software control.

All the software is in RAM permitting easy upgrading or personalizing. It includes a CODOS disk operating system, printer drivers (see the high-resolution possible on a definable dot-matrix printer in the photo), two eight-bit parallel ports and one RS-232 serial port with software select of baud rate, an eight-bit D/A port with filter and amp (for speech, sound, and music), and an interface for a 50K Baud, interrupt driven, network option.

Additionally, the MTU-130 contains four EPROM sockets which are software controlled, a high resolution light pen, separate cursor keys, and a bank of eight user-defined function keys.

A unique approach to bank switching—using indirect addressing on the 6502—allows one 64K section of memory to contain a program while the data resides above in its own 64K zone.

Digitized Sound

The optional MTU-BASIC 1.0 with graphics and disk library extensions is an enhanced Microsoft BASIC. Currently, bank switching is not available to BASIC directly, but the system permits relatively easy user enhancements. Also, when the computer is turned on, it says, “MTU model 130. Please enter today’s date.” The “voice” is entirely digital and sounds remarably human (except that high frequency is muted—the cutoff is around 4 KHz). This provision for digital storage of sound is exciting, but, like high resolution graphics, it is a byte-eater. A two second message uses 16K on the disk. This space can be reduced, though, and plans are in the works to make the storage more efficient. The manufacturer also expects to provide an optional A/D microphone peripheral which will permit owners to digitize their own messages.

The eight inch floppy drive spins all the time, but the head remains out of contact with the disk until necessary. And it is fast. A 14K high-resolution picture can load to screen in about two seconds. Transfer rate is over 19 thousand bytes per second, sustained.

Future Options

MTU is currently working on additional software for the 130. Expected in early 1982 are FORTH, PASCAL, cassette I/O, PET/Apple BASIC translator utilities, and a word processor. Planned hardware includes a 128K memory expansion board, the A/D microphone system, a high fidelity sound synthesis and analysis package, a network operating system, and a rigid disk controller.

A prototype board for construction of custom circuits and a banker board are available now as options.

Micro Technology was around 1980 a manufacturer of products aimed at the KIM-1 and AIM 65 and SYM-1 user. Later on they made the MTU-130 computer around the 6502 and a compact version the MT-140. After the founder and technical genius Hal Chamberlin left in 1986, it became focussed on software like Karaoke.

Micro Technology was around 1980 a manufacturer of products aimed at the KIM-1 and AIM 65 and SYM-1 user. Later on they made the MTU-130 computer around the 6502 and a compact version the MT-140. After the founder and technical genius Hal Chamberlin left in 1986, it became focussed on software like Karaoke. In 1968, Hal wrote a second synthesis program that computed audio sample voltages, giving control over the harmonic content and duration of notes and chords, based on the Nyquist Theorem of digital sampling. This ran on the Biomathematics Dept. Ambilog computer with two D/A converters used to drive an HP analog X-Y plotter to generate the analog audio output recorded to a Revox tape deck. Music synthesis pioneers had to be resourceful to get their analog outputs from early digital computers!

In 1968, Hal wrote a second synthesis program that computed audio sample voltages, giving control over the harmonic content and duration of notes and chords, based on the Nyquist Theorem of digital sampling. This ran on the Biomathematics Dept. Ambilog computer with two D/A converters used to drive an HP analog X-Y plotter to generate the analog audio output recorded to a Revox tape deck. Music synthesis pioneers had to be resourceful to get their analog outputs from early digital computers! On March 1, 1977, while still employed by Hendrix, David and Hal started Micro Technology Unlimited. Our goal then and still today is to Bring microcomputer digital audio down to everyone. Our designs are visionary and improve the creativity, productivity and quality of audio communications. It has been a real trip through the 1968-2004 period in digital audio!

On March 1, 1977, while still employed by Hendrix, David and Hal started Micro Technology Unlimited. Our goal then and still today is to Bring microcomputer digital audio down to everyone. Our designs are visionary and improve the creativity, productivity and quality of audio communications. It has been a real trip through the 1968-2004 period in digital audio!