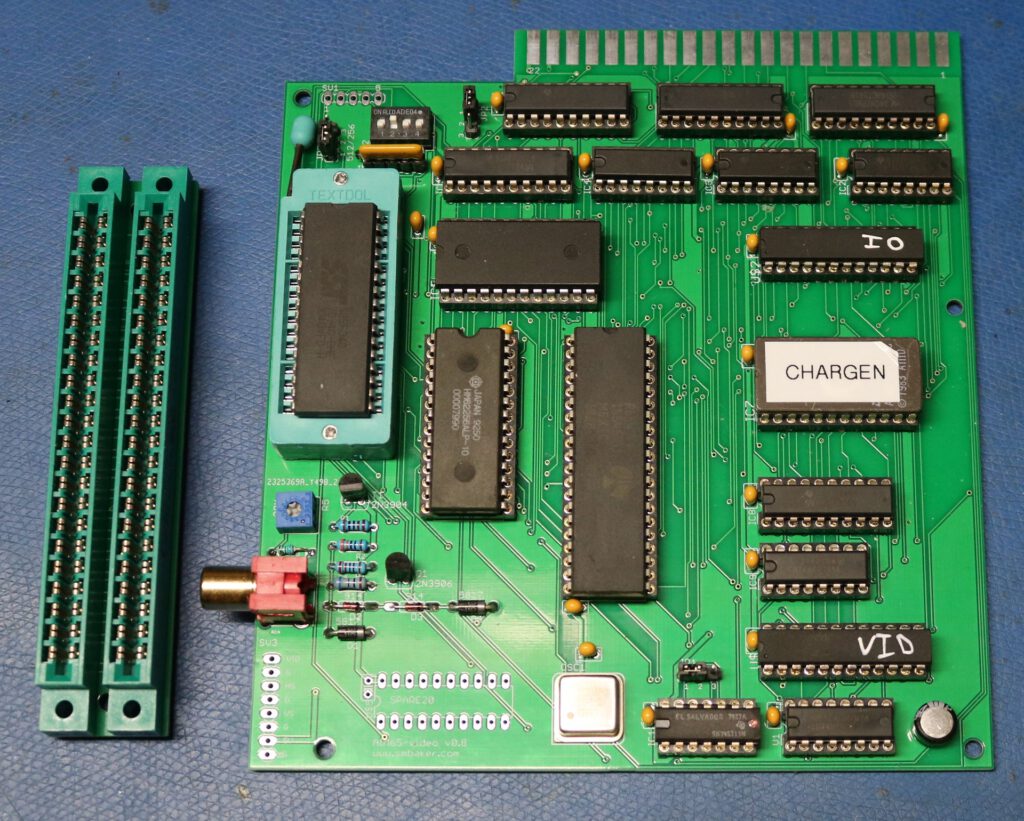

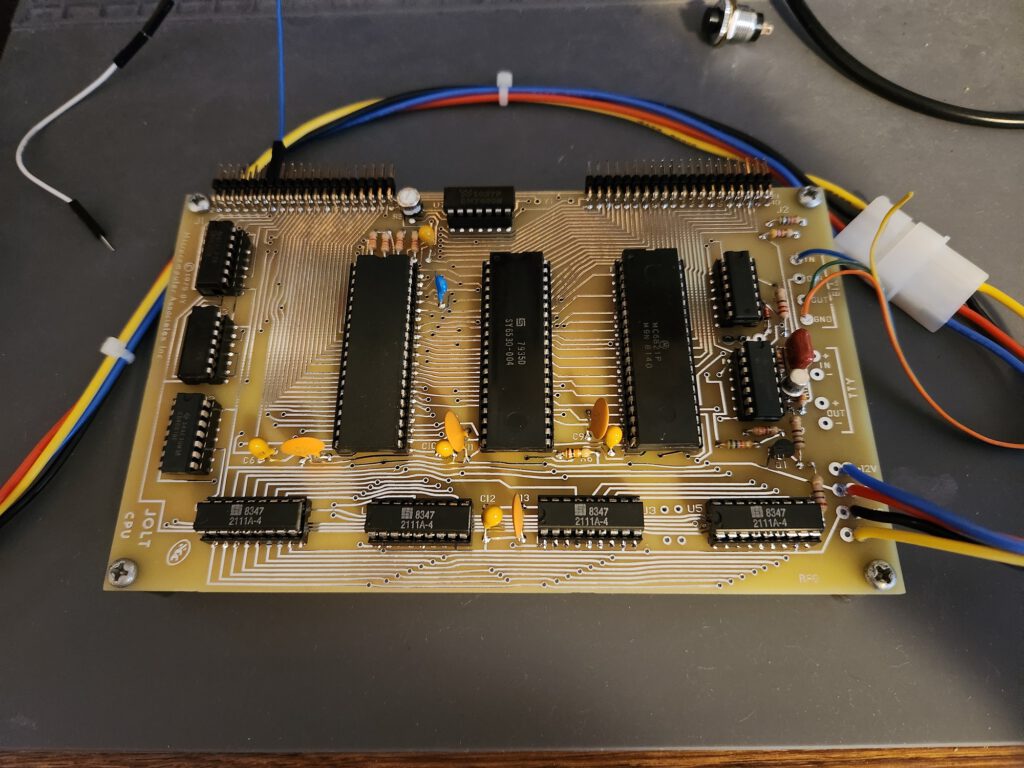

Scott LaBombard started many years ago on a replica of the Jolt. Quite a challenge, since only photos are known.

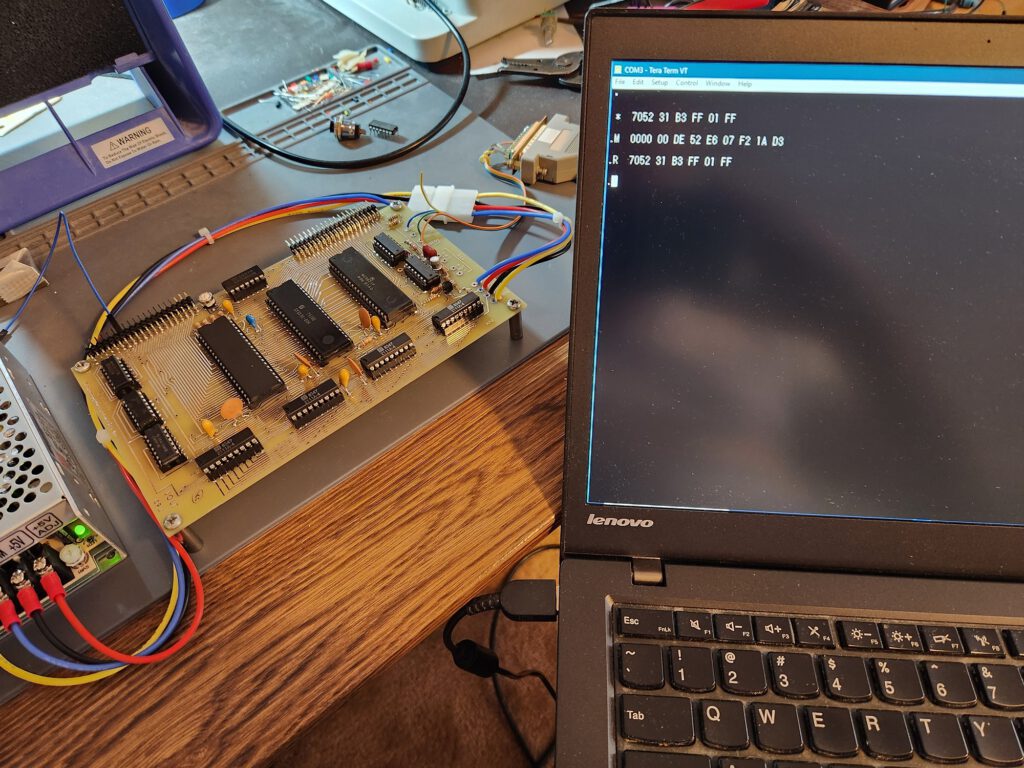

He succeeded in finishing a working replica as shown in the next photos sent by Scott.

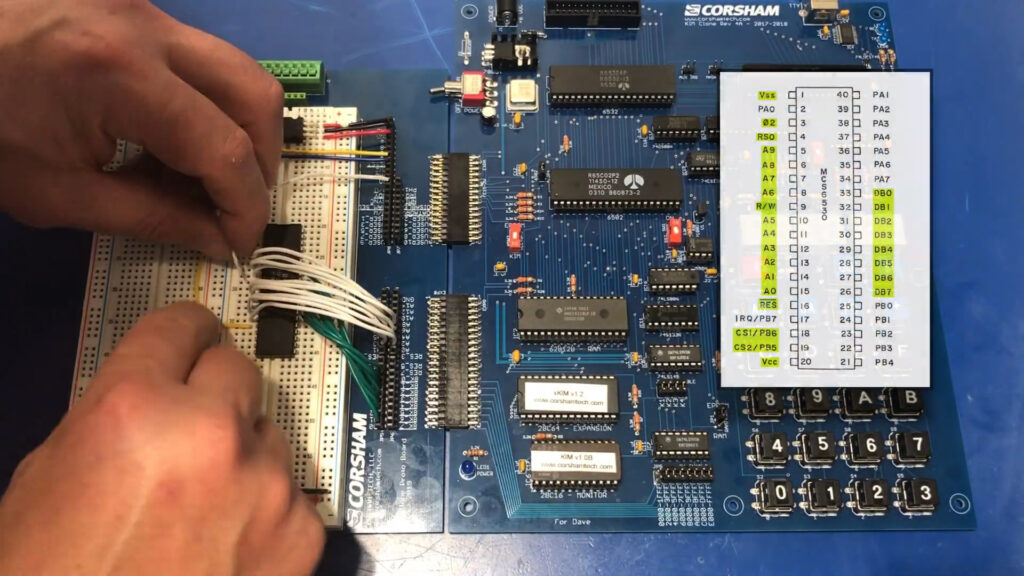

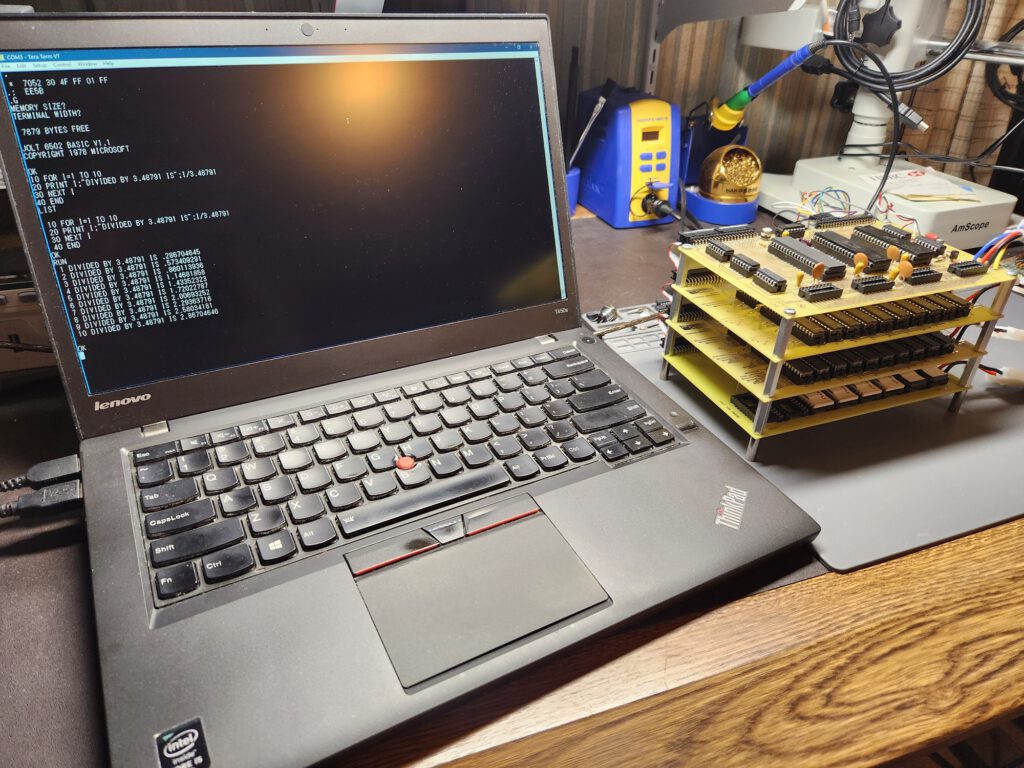

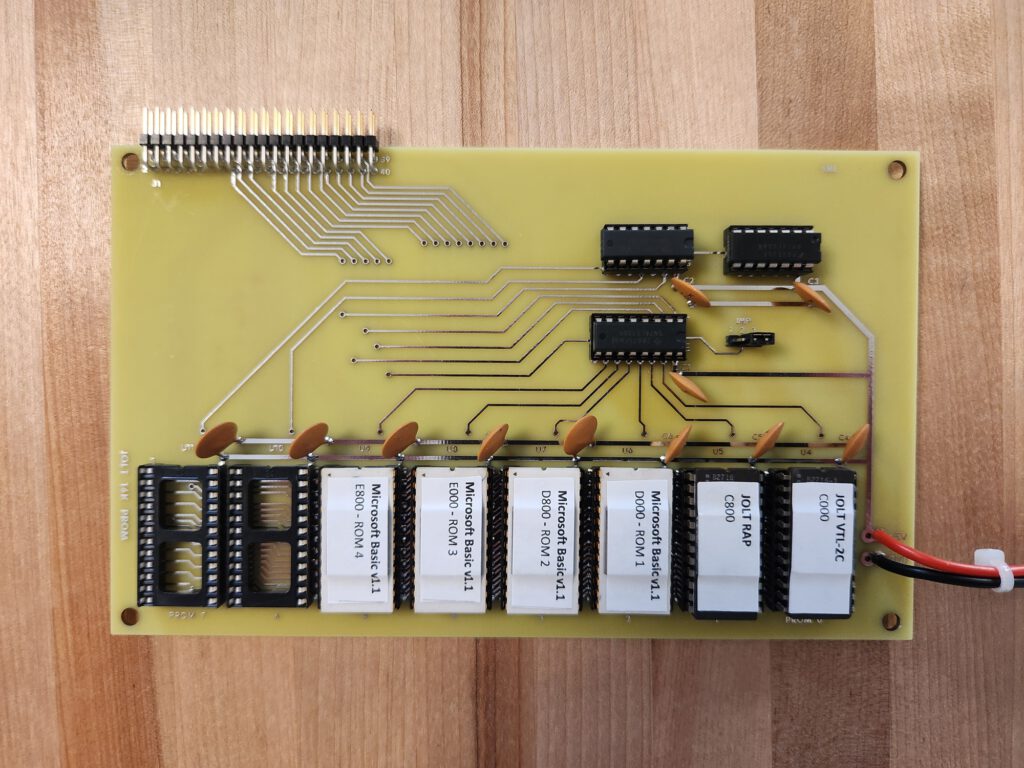

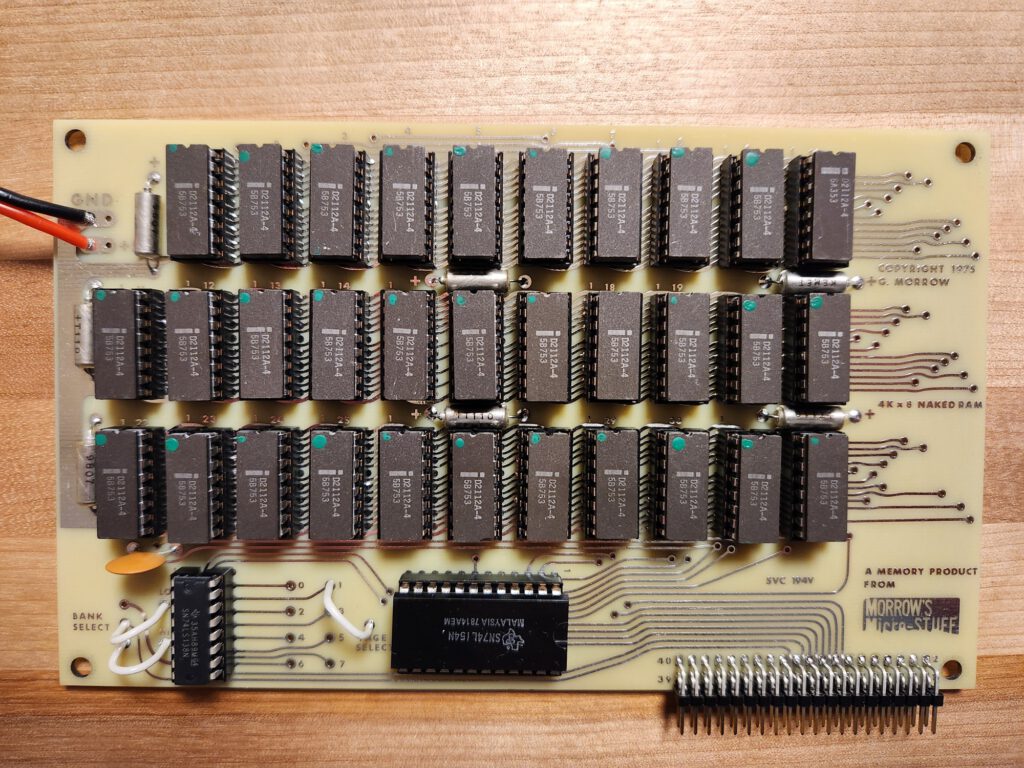

Attached is a picture showing the Jolt ‘stack’ running a late iteration of Microsoft’s 6502 Basic that Scott ‘ported’ to the Jolt. He even have it configured to support integer arrays and extended precision. Also included a picture of a replica of the George Morrow ‘naked’ 4k RAM board that was specifically marketed for Jolt owners back in the day (two are installed in the stack for 8k total). Last, there’s a picture of Scott’s own design of a 16K eprom board based on the mostly period correct 2716 eprom. It is jumper selectable for a base address of $8000 or $C000 (when configured for $C000, it only decodes $C000 – $EFFF because the Jolt decodes $Fxxx). One could install 28K of eprom with two of these boards!

In addition to Microsoft Basic, the eprom board has VTL-2 (Very Tiny Language) that is also ported to the Jolt. And last but not least, the eprom board has MAI’s RAP installed as well.

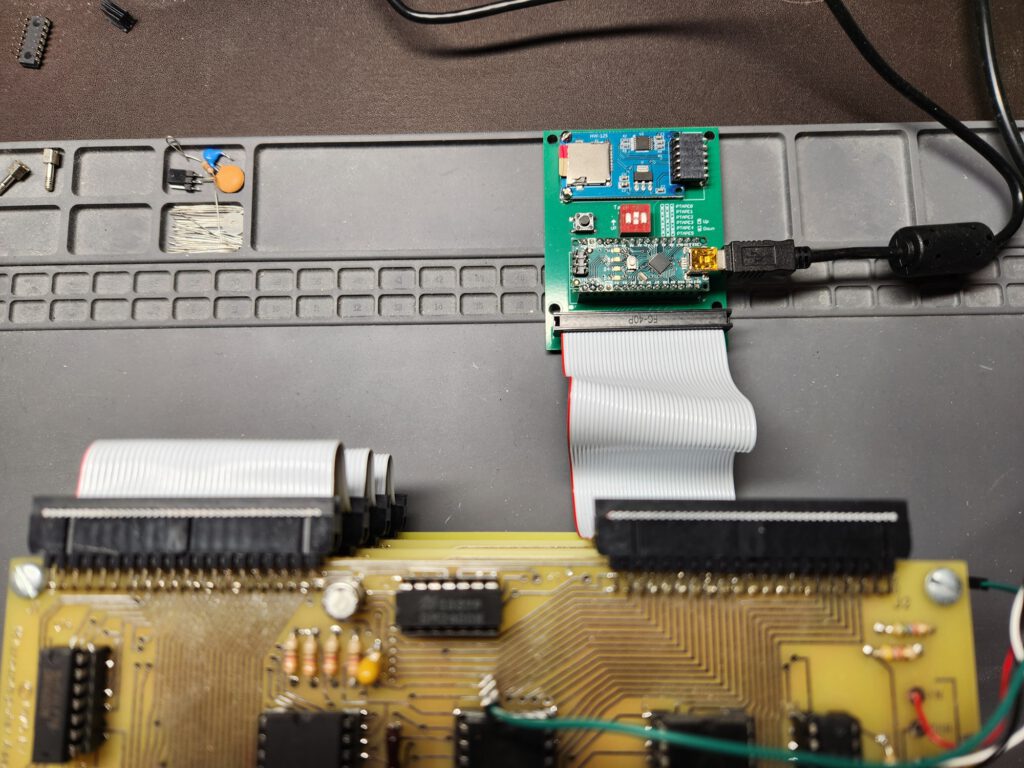

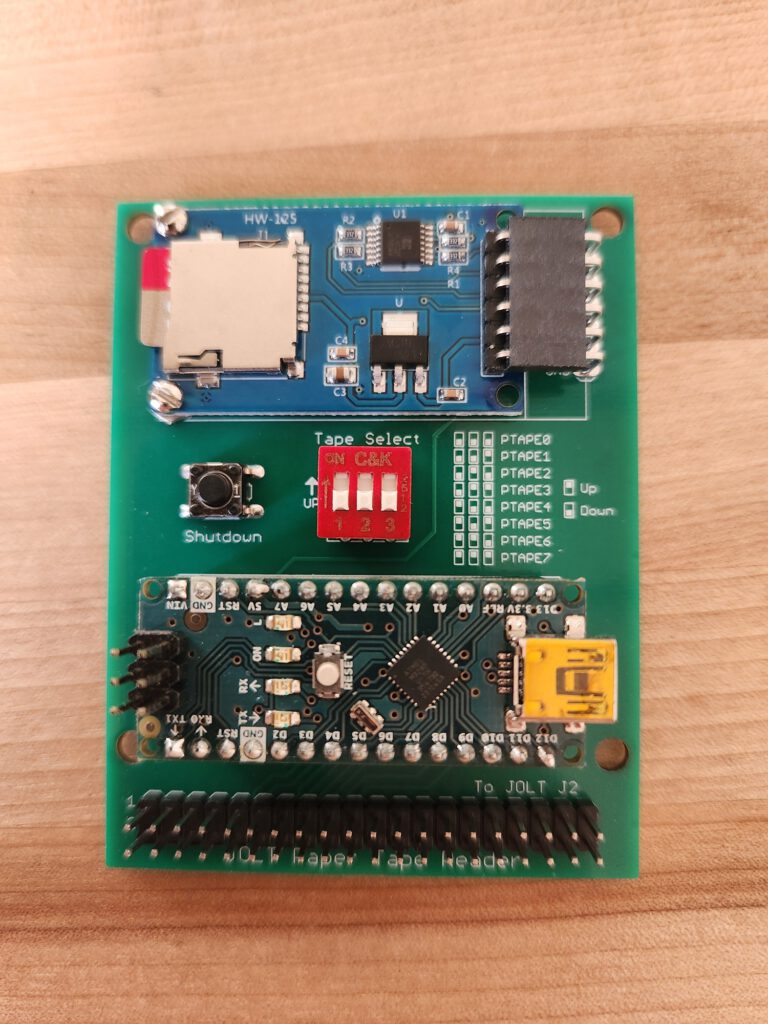

You may notice some wires hanging off from the J2 connector, that is connected to a ‘high speed tape reader’ that Scott designed specifically for the Jolt. It works directly with the TIM monitor just as documented (using the ‘H’ command to switch to the high speed tape reader, and then ‘LH’ to load ‘tapes’ in MOS Technology hex format). It’s super fast compared to loading via the console.

Scott has also created replicas of the original 2K eprom board that uses the venerable 1702 eproms, as well as the original power supply board.

He also did a replica of a George Morrow Micro-Stuff “Naked” 4K RAM board that was primarily marketed for the Jolt as an alternative to the original Jolt 4K RAM board.

Here an archive with a Tiny Basic Enhancement ROM Scott did. See below for what has been enhanced.

It also runs on the TIM Superjolt Emulator!

The JOLT replica

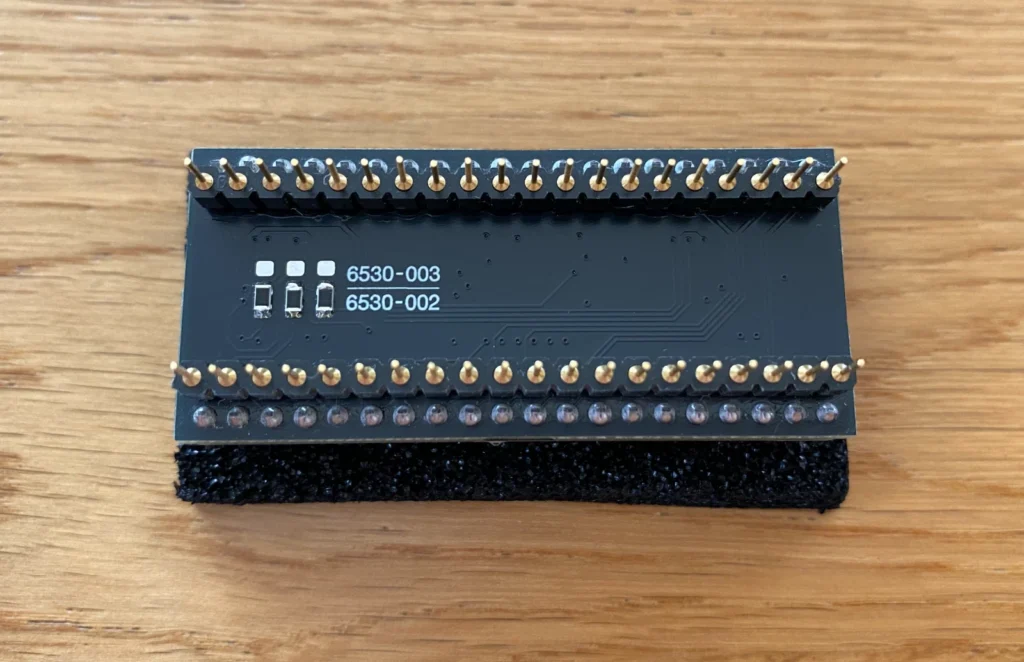

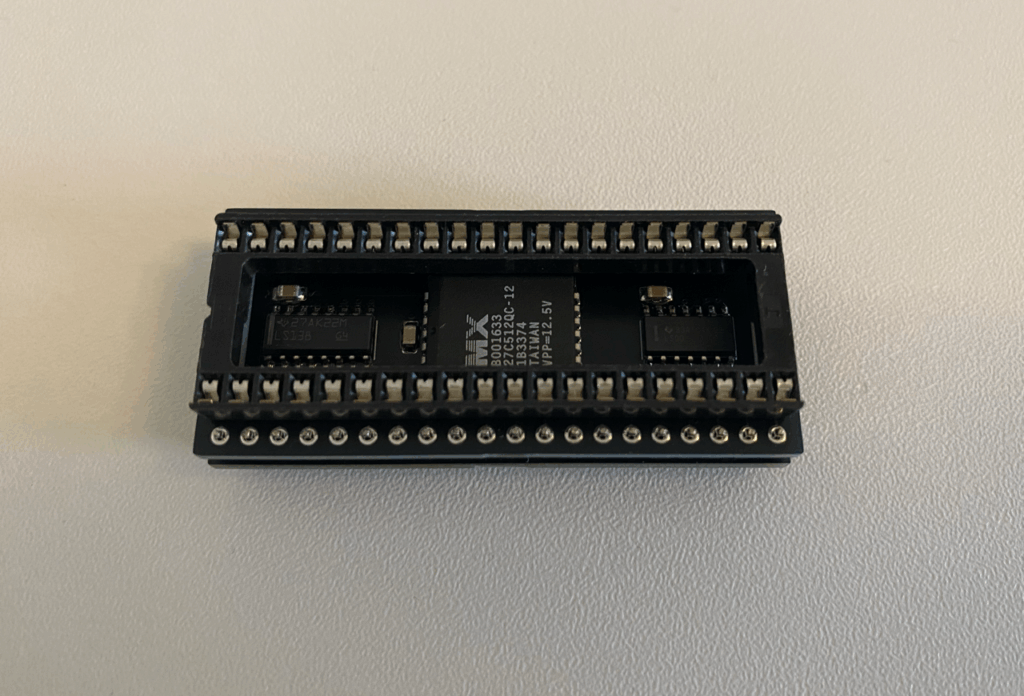

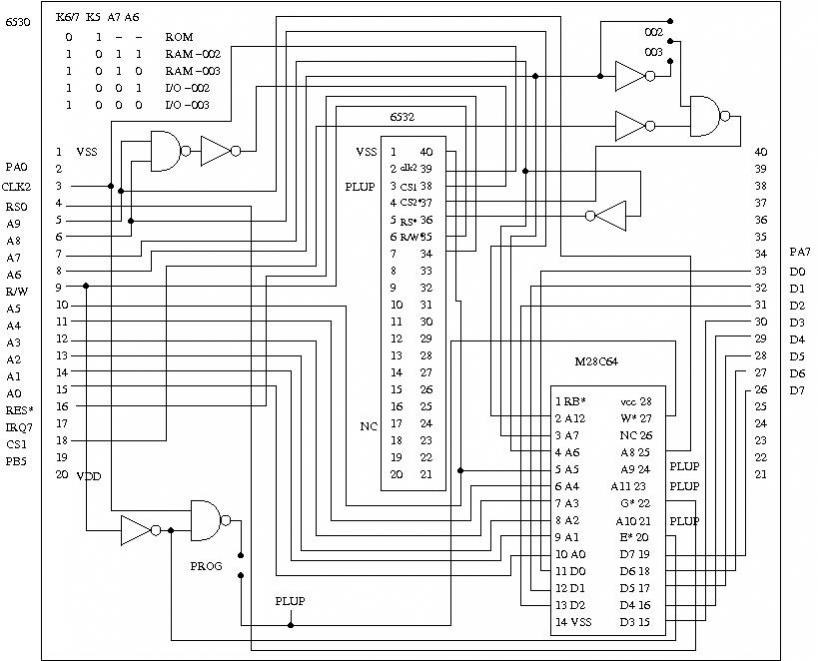

EPROM card

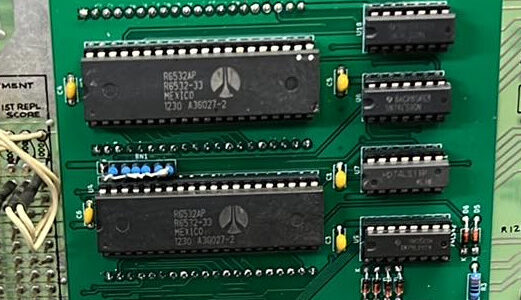

RAM card

PTP Highspeed reader

The text of the Tiny Basic enhancement:

The text of the Tiny Basic enhancement:

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

JOLT TinyBasic Enhancement ROM Notes

Scott LaBombard

August 2025

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Just add the ROM at $D000. No SW/HW modifications are

required.

Commands added: MON, HSPTR, NEW, AND, OR, NOT, PEEK, POKE

ABS, FRE, FOR, NEXT, LOAD, and SAVE

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

AND

example: PRINT AND(125,589)

output: 77

OR

example: PRINT OR(125,589)

output: 637

NOT

example: PRINT NOT(43)

output: -44

ABS

example: PRINT ABS(-43)

output: 43

FRE

Prints free memory.

Usage: PRINT FRE(0)

HSPTR

Toggles between using the high speed paper-tape reader

or the console for input.

NEW

Clears the current program.

PEEK

Print the contents of the specified decimal memory address.

example: PRINT PEEK(8192)

POKE

Store the specified value at the specified memory address.

example: POKE 8192,44

result: value 44 will be stored at address 8192

PEEK

example: PRINT PEEK(8192)

output: 44

FOR/NEXT

Standard FOR/NEXT loop support. STEP is not supported,

however reverse order loops are:

FOR I=1 TO 10 FOR I=10 TO 1

PRINT I PRINT I

NEXT I NEXT I

END END

SAVE

Will save the current Basic program in MOS Tech Hex format

to the console. After entering the SAVE command, you will

be at the TIM monitor prompt.

After the SAVE command has finished, you will be at the

TIM monitor prompt. Just enter the TIM 'G' command to

return to TinyBasic (via the TinyBasic warm start entry

point, so the Basic program remains intact).

LOAD

Will load a Basic program in MOS Tech Hex format from the

console or the high speed paper-tape reader (depending on

which is selected for program input by the HSPTR command

or via the TIM monitor's H command).

After the LOAD command has finished, you will be at the

TIM monitor prompt. Just enter the TIM 'G' command to

return to TinyBasic (via the TinyBasic warm start entry

point, so the Basic program remains intact).