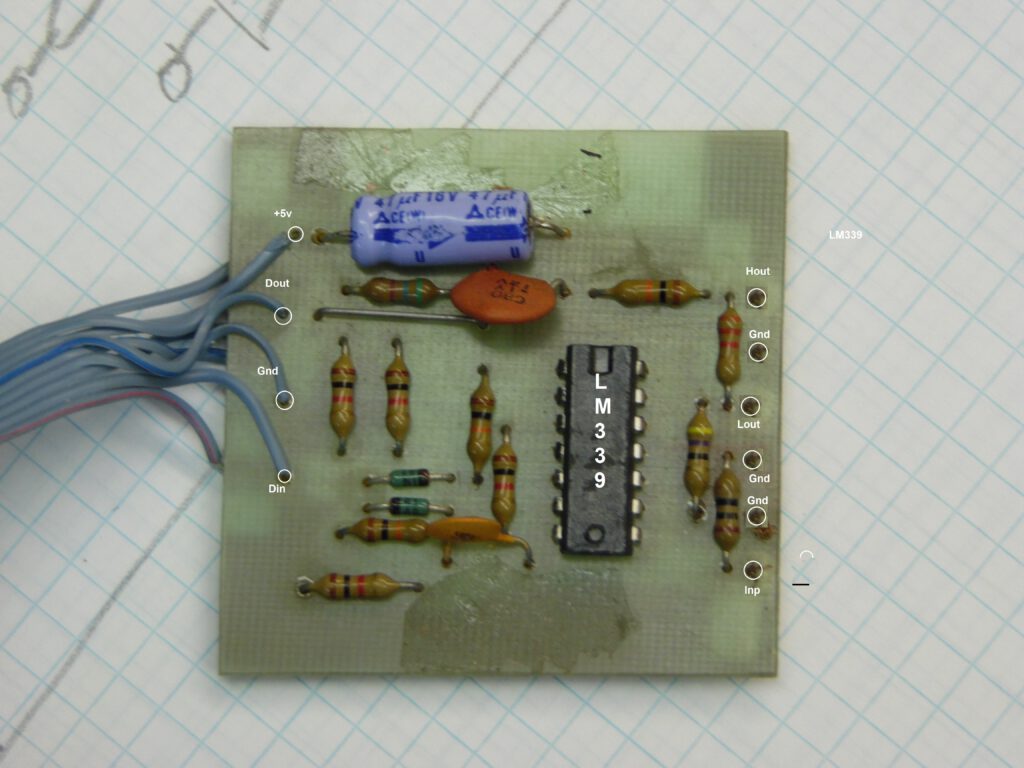

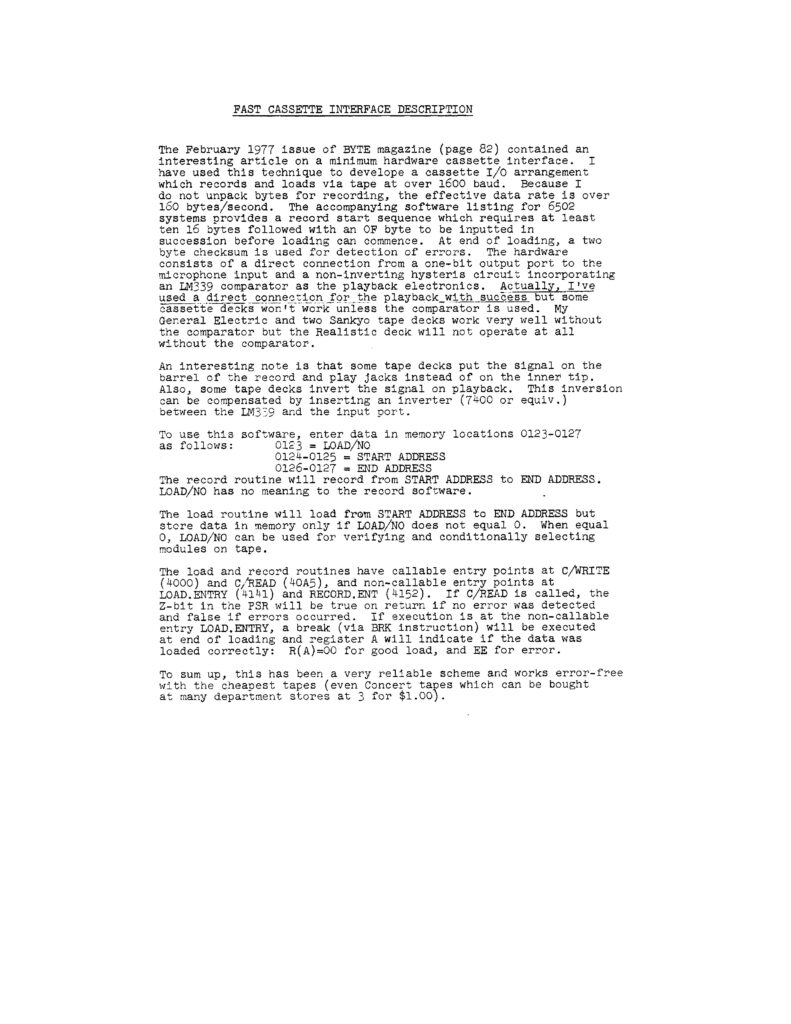

Glen Deas sent me an article about the Ziptape cassette interface, 1978, by the late Lew Edwards. Glen made a PCB for it.

The article about the Fast Cassette Interface is part of my CW Moser Assembler/editor package. Scanned by me in 2010 to the file kimfastcassette.pdf and on my website with the CW Moser package for years now .

Glen Deas knew it was designed by Lew Edwards and entered the source in modern assembler format.

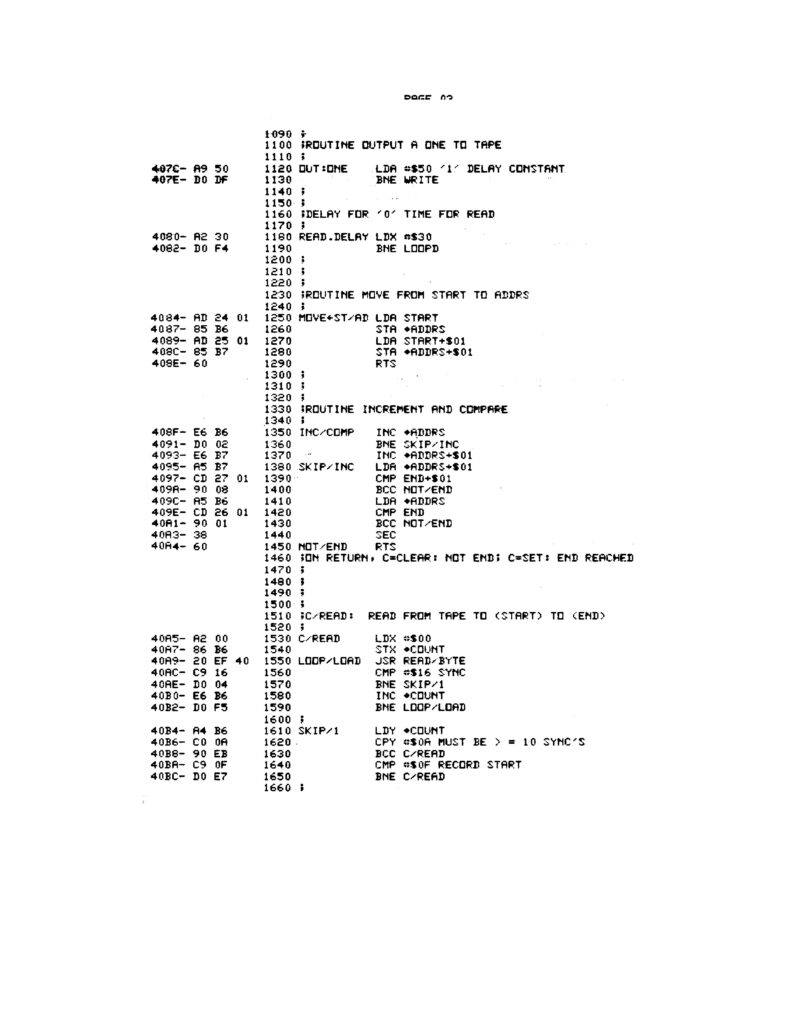

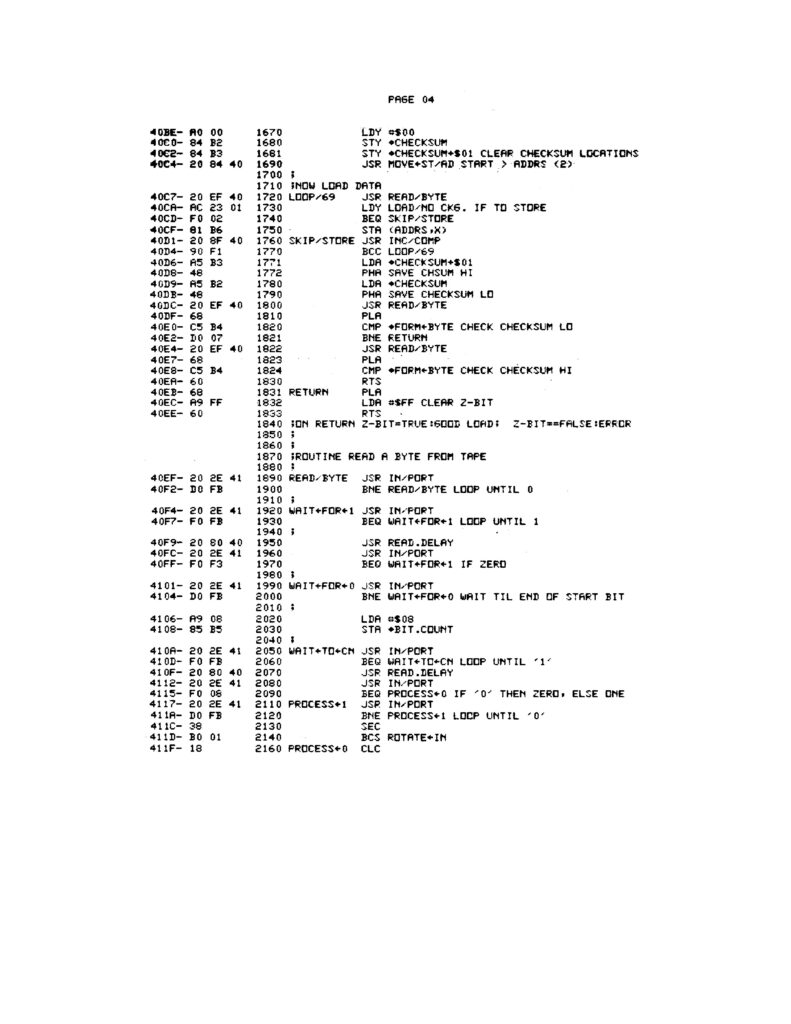

Page 1 A65 65C02 Assembler 1.16

Line# Loc Code Line

1

2 ;-----------------------------------------------------------------------------------------------------------

3 ; E:\ZIPTAPE>CSC ZIPTAPE1.ASM

4 ;

5 ; E:\ZIPTAPE>CSC6502 ZIPTAPE1.ASM

6 ; Page 1 File ZIPTAPE1.ASM

7 ;

8 ;

9 ; ORG $4000

10 4000 * = $4000

11 ; ***Irk FAST CASSETTE INTERFACE

12 ; (CONFIGURED FOR KIM)

13 ;================================================================

14 ;modified for CSC 6502 Cross Assembler Glen Deas K5GED 1/11/2023

15 ;================================================================

16 ;To use this software, enter data in memory locations 0123

17 ;as follows: 0123 = LOAD/NO

18 ; 0124-0125 = START ADDRESS

19 ; 0126-0127 = END ADDRESS

20 ;The record routine will record from START ADDRESS to END ADDRESS

21 ;LOAD/NO has no meaning to the record software.;

22 ;

23 ;The load routine will load from START ADDRESS to END ADDRESS

24 ;store data in memory onl if LOAD/NO does not =al 0. Where

25 ;LOAD/NO can be used for verifying and unconditionally selecting

26 ;modules on tape.

27 ;

28 ;The load and record routines have callable entry points at

29 ;(4000) and CREAD (40A5), and non-ccallable entry points at

30 ;LDENTRY (4141) and RCENTRY (4152). If CREAD is called, the

31 ;Z bit in the PSR will be treu on return if no error was detected

32 ;and false if errors occurred. If execution is at the non callable

33 ;entry LDENTRY, a break (via BRK instruction) will be execcuted

34 ;at end of loading and register A will indicate if the data was

35 ;loaded correctly: R(A)=00 for good load, and EE for errors.

36 ;

37 ;

38 1702 CPORT = $1702 ;CASSETTE I/O

39 1703 CPORTD = $1703 ;PORT DIRECTION REGISTER

40 ;BIT 3 = WRITE TO CASSETTE; BIT 2 - READ FROM CASSETTE

41 ;

42 ;

43 ; :== VARIABLES ==

44 00B2 CHECKSUM = $00B2

45 00B6 ADDRS = $00B6

46 00B6 COUNT = ADDRS

47 00B4 FORMBYTE = $00B4

48 00B4 SYNCCOUNT = FORMBYTE

49 00B5 BITCOUNT = $00B5

50 ;

51 ;INPUT PARMS

52 0123 LOADNO = $0123

53 0124 TSTART = $0124

54 0126 TEND = $0126

55 ;

56 ;CWRITE: WRITE TO TAPE FROM (START) TO (END)

57 ;

58 4000 AD 03 17 CWRITE LDA CPORTD

59 4003 09 08 ORA #%00001000 ;BIT 3 FOR OUTPUT ON PIA

60 4005 8D 03 17 STA CPORTD

Page 2 A65 65C02 Assembler 1.16

Line# Loc Code Line

61 ;THE ABOVE INITIALIZES BIT 3 FOR OUTPUT ON PIA

62 4008 A9 20 LDA #$20 ;32 TIMES

63 400A 85 B6 STA COUNT

64 400C A9 16 LPRECST LDA #$16 ;SYNC CHAR.

65 400E 20 41 40 JSR WRITEBYTE

66 4011 A9 10 LDA #$10

67 4013 85 B4 STA SYNCCOUNT

68 4015 20 5D 40 LPDELA JSR OUTZERO

69 4018 C6 B4 DEC SYNCCOUNT

70 401A D0 F9 BNE LPDELA

71 ;DELAY TIME FOR SYNC

72 401C C6 B6 DEC COUNT

73 401E D0 EC BNE LPRECST

74 4020 20 84 40 JSR MOVESTAD

75 4023 A9 0F LDA #$0F ;RECORD START CHAR.

76 4025 20 41 40 JSR WRITEBYTE

77 4028 A2 00 LDX #$00

78 402A 86 B2 STX CHECKSUM ;CLEAR CHECKSUM LOW BYTE

79 402C 86 B3 STX CHECKSUM+1 ;AND HIGH BYTE

80 ;

81 402E A1 B6 LOOPDATA LDA (ADDRS,X) ;LOAD DATA INDEXED BY X REG

82 4030 20 41 40 JSR WRITEBYTE

83 4033 20 8F 40 JSR INCCOMP

84 4036 90 F6 BCC LOOPDATA

85 4038 A5 B3 LDA CHECKSUM+1

86 403A 48 PHA SAVE HI CKSUM

87 403B A5 B2 LDA CHECKSUM

88 403D 20 41 40 JSR WRITEBYTE WRITE LO CKSUM FIRST

89 4040 68 PLA HI CKSUM NEXT

90 ;THE ABOVE WRITES BOTH CHECKSUM BYTES

91 ;

92 ;ROUTINE TO WRITE A BYTE TO TAPE

93 ;

94 4041 85 B4 WRITEBYTE STA FORMBYTE

95 4043 20 34 41 JSR CKSUMADD UPDATE CHECKSUM COUNTER

96 4046 20 7C 40 JSR OUTONE START BIT

97 4049 A9 08 LDA #$08 8 BITS

98 404B 85 B5 STA BITCOUNT

99 404D 06 B4 DATALOOP ASL FORMBYTE SHIFT LEFT INTO CARRY

100 404F 90 05 BCC ZEROBIT

101 4051 20 7C 40 ONEBIT JSR OUTONE

102 4054 F0 03 BEQ CKENDBY

103 4056 20 5D 40 ZEROBIT JSR OUTZERO

104 4059 C6 B5 CKENDBY DEC BITCOUNT

105 405B D0 F0 BNE DATALOOP

106 ;NOT OUTPUT 1 STOP BIT

107 ;

108 ;ROUTINE OUTPUT A ZERO TO TAPE

109 ;

110 405D A9 20 OUTZERO LDA #$20 '0' DELAY CONSTANT

111

112 ;:ROUTINE WRITE TO TAPE

113 ;

114 405F 48 WRITE PHA SAVE DELAY CONSTANT

115 4060 AD 02 17 LDA CPORT

116 4063 09 08 ORA #%00001000 ;OUT A" ON BIT 3

117 4065 8D 02 17 STA CPORT

118 4068 68 PLA

119 4069 48 PHA

120 406A AA TAX DELAY CONSTANT

Page 3 A65 65C02 Assembler 1.16

Line# Loc Code Line

121 406B 20 78 40 JSR LOOPD

122 406E AD 02 17 LDA CPORT

123 4071 29 F7 AND #%11110111 ;OUT A '01 ON BIT 3

124 4073 8D 02 17 STA CPORT

125 4076 68 PLA

126 4077 AA TAX DELAY CONSTANT

127 4078 CA LOOPD DEX

128 4079 D0 FD BNE LOOPD

129 407B 60 RTS

130 ;

131 ;ROUTINE OUTPUT A ONE TO TAPE

132 ;

133 407C A9 50 OUTONE LDA #$50 '1' DELAY CONSTANT

134 407E D0 DF BNE WRITE

135 ;DELAY FOR '0' TIME FOR READ

136

137 4080 A2 30 READDELAY LDX #$30

138 4082 D0 F4 BNE LOOPD

139 ;

140 ;ROUTINE MOVE FROM START TO ADDRS

141 ;

142 4084 AD 24 01 MOVESTAD LDA TSTART

143 4087 85 B6 STA ADDRS

144 4089 AD 25 01 LDA TSTART+1

145 408C 85 B7 STA ADDRS+1

146 408E 60 RTS

147 ;:ROUTINE INCREMENT AND COMPARE

148

149 408F E6 B6 INCCOMP INC ADDRS

150 4091 D0 02 BNE SKIPINC

151 4093 E6 B7 INC ADDRS+1

152 4095 A5 B7 SKIPINC LDA ADDRS+1

153 4097 CD 27 01 CMP TEND+1

154 409A 90 08 BCC NOTEND

155 409C A5 B6 LDA ADDRS

156 409E CD 26 01 CMP TEND

157 40A1 90 01 BCC NOTEND

158 40A3 38 SEC

159 40A4 60 NOTEND RTS

160 ;ON RETURN, C=CLEAR: NOTEND: C=SET: END REACHED

161 ;

162 40A5 A2 00 CREAD LDX #$00

163 40A7 86 B6 STX COUNT

164 40A9 20 EF 40 LOOPLOAD JSR READBYTE

165 40AC C9 16 CMP #$16 SYNC

166 40AE D0 04 BNE SKIP1

167 40B0 E6 B6 INC COUNT

168 40B2 D0 F5 BNE LOOPLOAD

169 40B4 A4 B6 SKIP1 LDY COUNT

170 40B6 C0 0A CPY #$0A ;MUST B >= 10 SYNC'S

171 40B8 90 EB BCC CREAD

172 40BA C9 0F CMP #$0F RECORD START

173 40BC D0 E7 BNE CREAD

174 40BE A0 00 LDY #$00

175 40C0 84 B2 STY CHECKSUM

176 40C2 84 B3 STY CHECKSUM+1 LAR CHECKSUM LOCATIONS

177 40C4 20 84 40 JSR MOVESTAD START > ADDRS (2)

178 ;

179 ;NOW LOAD DATA

180

Page 4 A65 65C02 Assembler 1.16

Line# Loc Code Line

181 40C7 20 EF 40 LOOP69 JSR READBYTE

182 40CA AC 23 01 LDY LOADNO ;CKG IF TO STORE

183 40CD F0 02 BEQ SKIPSTOR

184 40CF 81 B6 STA (ADDRS,X)

185 40D1 20 8F 40 SKIPSTOR JSR INCCOMP

186 40D4 90 F1 BCC LOOP69

187 40D6 A5 B3 LDA CHECKSUM+1

188 40D8 48 PHA SAVE CHKSUM HI

189 40D9 A5 B2 LDA CHECKSUM

190 40DB 48 PHA SAVE CHKSUM LO

191 40DC 20 EF 40 JSR READBYTE

192 40DF 68 PLA

193 40E0 C5 B4 CMP FORMBYTE CHECK CHECKSUM LO

194 40E2 D0 07 BNE RETURN

195 40E4 20 EF 40 JSR READBYTE

196 40E7 68 PLA

197 40E8 C5 B4 CMP FORMBYTE CHECK CHECKSUM HI

198 40EA 60 RTS

199 40EB 68 RETURN PLA

200 40EC A9 FF LDA #$FF CLEAR Z-BIT

201 40EE 60 RTS

202 ;ON RETURN Z-BIT = TRUE:GOOD LOAD: Z-BIT ==FALSE: ERROR

203 ;

204 ;ROUTINE READ A BYTE FROM TAPE

205 ;

206 40EF 20 2E 41 READBYTE JSR INPORT

207 40F2 D0 FB BNE READBYTE LOOP UNTIL 0

208 40F4 20 2E 41 WAITFORI JSR INPORT

209 40F7 F0 FB BEQ WAITFORI LOOP UNTIL 1

210 40F9 20 80 40 JSR READDELAY

211 40FC 20 2E 41 JSR INPORT

212 40FF F0 F3 BEQ WAITFORI IF ZERO

213 4101 20 2E 41 WAITFORO JSR INPORT

214 4104 D0 FB BNE WAITFORO WAIT TIL END OF START BIT

215 4106 A9 08 LDA #$08

216 4108 85 B5 STA BITCOUNT

217 410A 20 2E 41 WAITTOCN JSR INPORT

218 410D F0 FB BEQ WAITTOCN ;LOOP UNTIL '1'

219 410F 20 80 40 JSR READDELAY

220 4112 20 2E 41 JSR INPORT

221 4115 F0 08 BEQ PROCESSO IF '0' THENZERO, ELSE ONE

222 ;

223 4117 20 2E 41 PROCESS1 JSR INPORT

224 411A D0 FB BNE PROCESS1 ;LOOP UNTIL '0

225 411C 38 SEC

226 411D B0 01 BCS ROTATEIN

227 411F 18 PROCESSO CLC

228 ;

229 4120 26 B4 ROTATEIN ROL FORMBYTE ;ROTATE CARRY

230 4122 C6 B5 DEC BITCOUNT

231 4124 D0 E4 BNE WAITTOCN

232 4126 A5 B4 LDA FORMBYTE

233 4128 20 34 41 JSR CKSUMADD UPDATE CHECKSUM

234 412B A5 B4 LDA FORMBYTE

235 412D 60 RTS

236 ;

237 ;

238 ;INPUT FROM TAPE

239 ;

240 412E AD 02 17 INPORT LDA CPORT

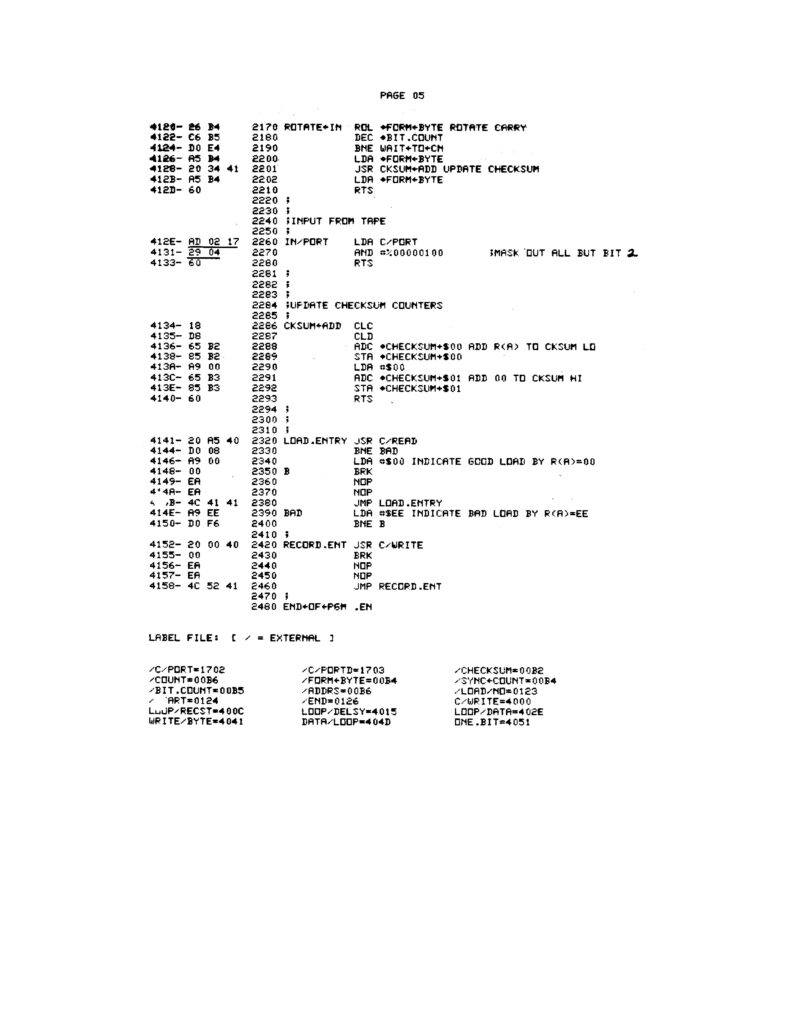

Page 5 A65 65C02 Assembler 1.16

Line# Loc Code Line

241 4131 29 04 AND #%00000100 ;MASK OUT ALL BUT BIT 2

242 4133 60 RTS

243 ;

244 ;

245 ;UPDATE CHEKSUM COUNTERS

246 ;

247 4134 18 CKSUMADD CLC

248 4135 D8 CLD

249 4136 65 B2 ADC CHECKSUM+$00 AD R(A) TO CKSUM LO

250 4138 85 B2 STA CHECKSUM+$00

251 413A A9 00 LDA #$00

252 413C 65 B3 ADC CHECKSUM+1 ADD 00 TO CKSUM HI

253 413E 85 B3 STA CHECKSUM+1

254 4140 60 RTS

255 ;

256 ;

257 4141 20 A5 40 LOADENTRY JSR CREAD

258 4144 D0 08 BNE BAD

259 4146 A9 00 LDA #$00 INDICATE GOOD LOAD BY R(A) =

260 4148 00 B BRK

261 4149 EA NOP

262 414A EA NOP

263 414B 4C 41 41 JMP LOADENTRY

264 414E A9 EE BAD LDA #$EE ;INICATE BAD LOAD BY RA)=EE

265 4150 D0 F6 BNE B

266 ;

267 4152 20 00 40 RECORDENT JSR CWRITE

268 4155 00 BRK

269 4156 EA NOP

270 4157 EA NOP

271 4158 4C 52 41 JMP RECORDENT

272

273 ;END OF PROGRAM

274

275 415B .END

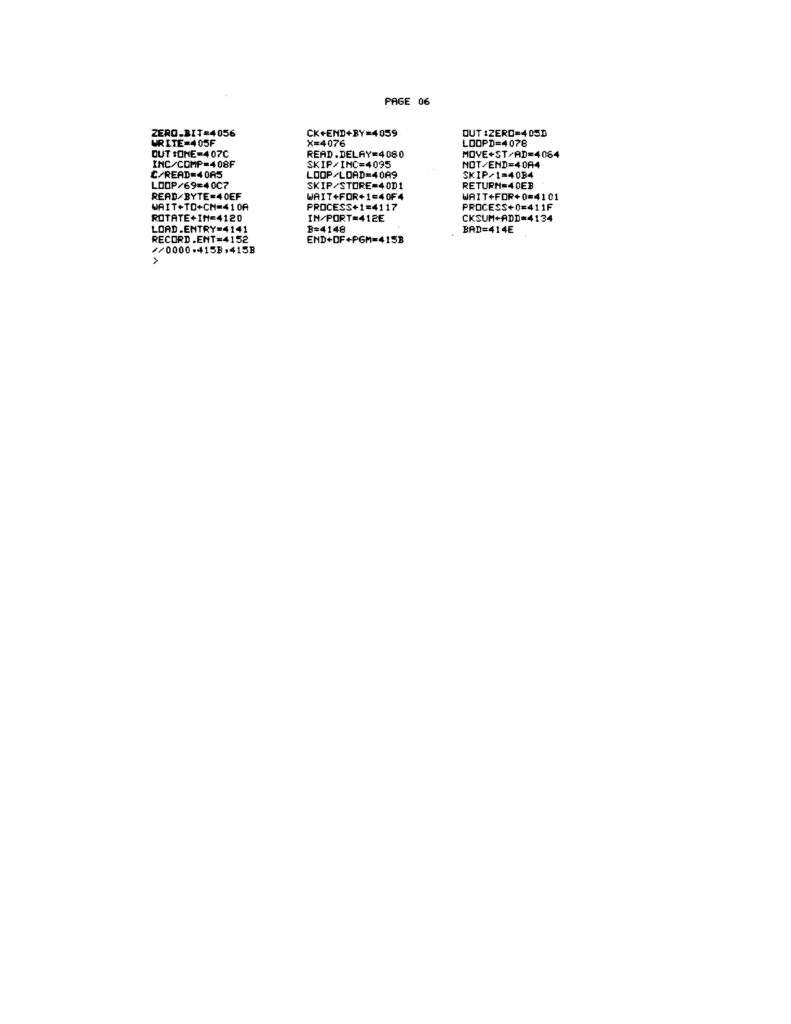

Page 6 A65 65C02 Assembler 1.16

Symbol Value Line References

ADDRS 00B6 45 (9) 46 81 143 145 149 151 152 155 184

BAD 414E 264 (1) 258

BITCOUNT 00B5 49 (4) 98 104 216 230

B 4148 260 (1) 265

CHECKSUM 00B2 44 (12) 78 79 85 87 175 176 187 189 249 250 252 253

CKENDBY 4059 104 (1) 102

CKSUMADD 4134 247 (2) 95 233

COUNT 00B6 46 (5) 63 72 163 167 169

CPORT 1702 38 (5) 115 117 122 124 240

CPORTD 1703 39 (2) 58 60

CREAD 40A5 162 (3) 257 171 173

CWRITE 4000 58 (1) 267

DATALOOP 404D 99 (1) 105

FORMBYTE 00B4 47 (8) 48 94 99 193 197 229 232 234

INCCOMP 408F 149 (2) 83 185

INPORT 412E 240 (7) 206 208 211 213 217 220 223

LOADENTRY 4141 257 (1) 263

LOADNO 0123 52 (1) 182

LOOP69 40C7 181 (1) 186

LOOPDATA 402E 81 (1) 84

LOOPD 4078 127 (3) 121 128 138

LOOPLOAD 40A9 164 (1) 168

LPDELA 4015 68 (1) 70

LPRECST 400C 64 (1) 73

MOVESTAD 4084 142 (2) 74 177

NOTEND 40A4 159 (2) 154 157

ONEBIT 4051 101 (0)

OUTONE 407C 133 (2) 96 101

OUTZERO 405D 110 (2) 68 103

PROCESS1 4117 223 (1) 224

PROCESSO 411F 227 (1) 221

READBYTE 40EF 206 (5) 164 181 191 195 207

READDELAY 4080 137 (2) 210 219

RECORDENT 4152 267 (1) 271

RETURN 40EB 199 (1) 194

ROTATEIN 4120 229 (1) 226

SKIP1 40B4 169 (1) 166

SKIPINC 4095 152 (1) 150

SKIPSTOR 40D1 185 (1) 183

SYNCCOUNT 00B4 48 (2) 67 69

TEND 0126 54 (2) 153 156

TSTART 0124 53 (2) 142 144

WAITFORI 40F4 208 (2) 209 212

WAITFORO 4101 213 (1) 214

WAITTOCN 410A 217 (2) 218 231

WRITEBYTE 4041 94 (4) 65 76 82 88

WRITE 405F 114 (1) 134

ZEROBIT 4056 103 (1) 100

Errors = 0

Warnings = 0

;184000AD031709088D0317A92085B6A916204140A91085B4205D4007EA

;184018C6B4D0F9C6B6D0EC208440A90F204140A20086B286B3A1B60D92

;184030204140208F4090F6A5B348A5B22041406885B4203441207C0A08

;18404840A90885B506B49005207C40F003205D40C6B5D0F0A920480AF2

;184060AD021709088D02176848AA207840AD021729F78D021768AA0805

;184078CAD0FD60A950D0DFA230D0F4AD240185B6AD250185B760E60E67

;184090B6D002E6B7A5B7CD27019008A5B6CD260190013860A200860B96

;1840A8B620EF40C916D004E6B6D0F5A4B6C00A90EBC90FD0E7A0000EE7

;1840C084B284B320844020EF40AC2301F00281B6208F4090F1A5B30C79

;1840D848A5B24820EF4068C5B4D00720EF4068C5B46068A9FF60200D3E

;1840F02E41D0FB202E41F0FB208040202E41F0F3202E41D0FBA9080C59

;18410885B5202E41F0FB208040202E41F008202E41D0FB38B0011809D7

;18412026B4C6B5D0E4A5B4203441A5B460AD021729046018D865B20B83

;18413885B2A90065B385B36020A540D008A90000EAEA4C4141A9EE0BE0

;0B4150D0F620004000EAEA4C52410575

;00000F000F

See also:

MTU K-1008 Visible Memory

The MTU Visible Memory is a memory mapped video display made by MTU. Supported by the KIM-1 Simulator.

See the MTU ...

TTY Serial

TTY Serial

The KIM-1 Simulator comes with a 'console', a glass teletype 24x80 screen. It has a subset of ANSI/VT100 sup...

TTY Console

TTY console mode

Press the TTY console switch to let the KIM simulator use a glass teletype in a console window. The st...

SD/RTC Card System, xKIM and CP/M-65

The SD-Shield is a mass storage device designed by Bob Applegate for Corsham Technologies. He named it SD/RTC Card. Ba...