This is the coolest thing we’ve done… so far!

Our original 6800 board continues to be a fun project to work with. I grew up doing 6502 and Z80 assembly language and have always been able to do a lot with either, but the 6809 is just amazing! The instruction set and addressing modes make it easy to write much more complicated code. There are numerous operating systems for this processor, include multi-tasking and multi-user options.

Features

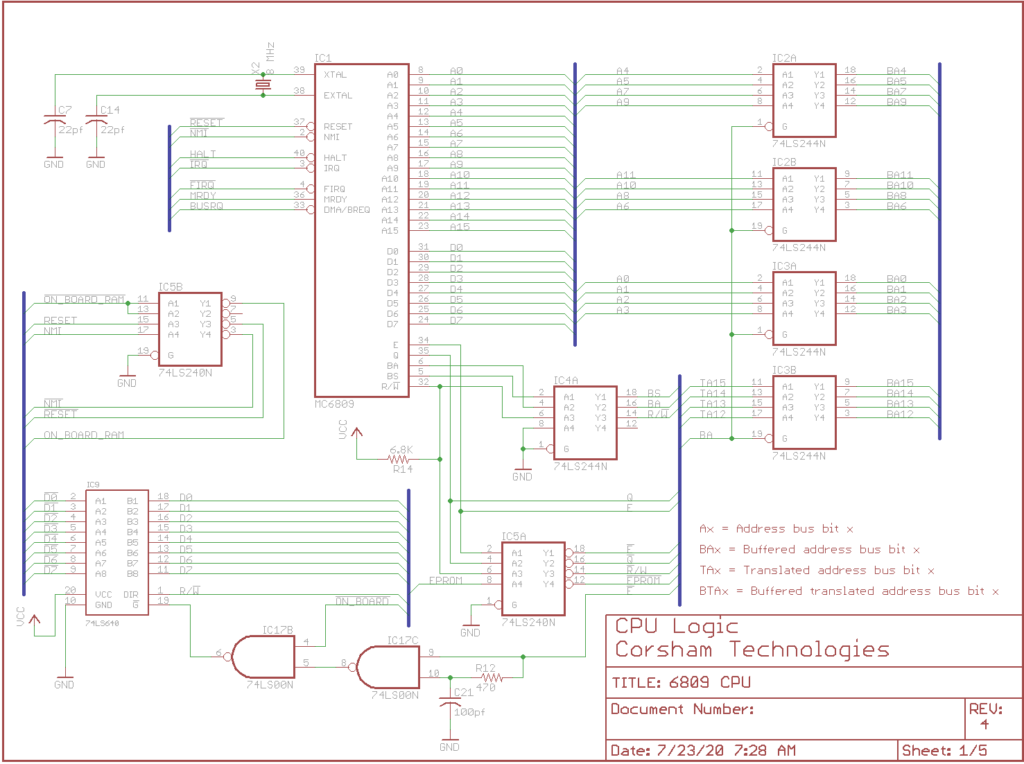

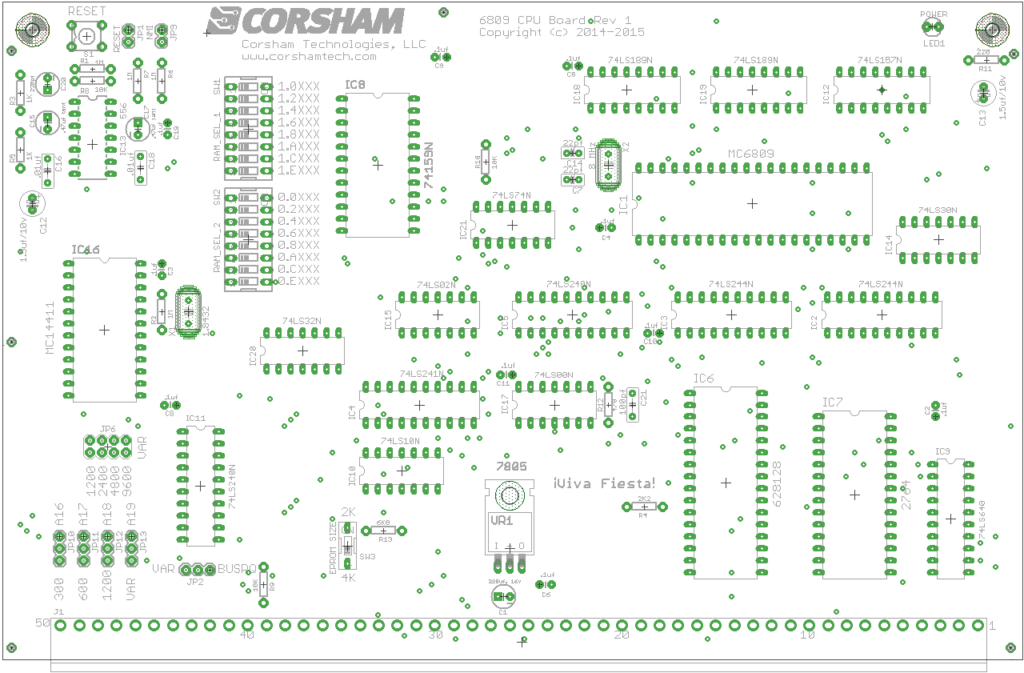

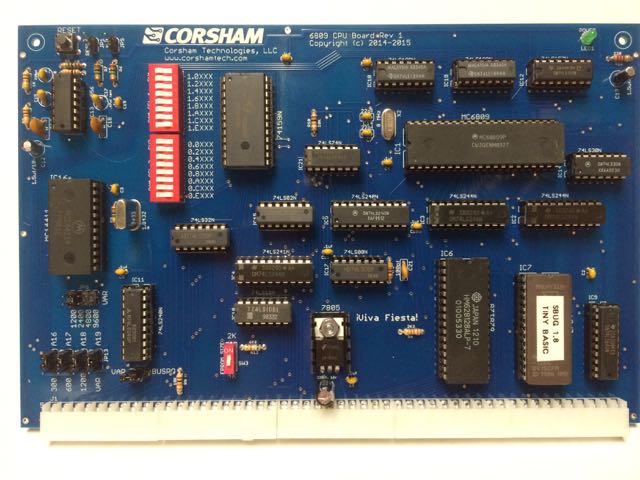

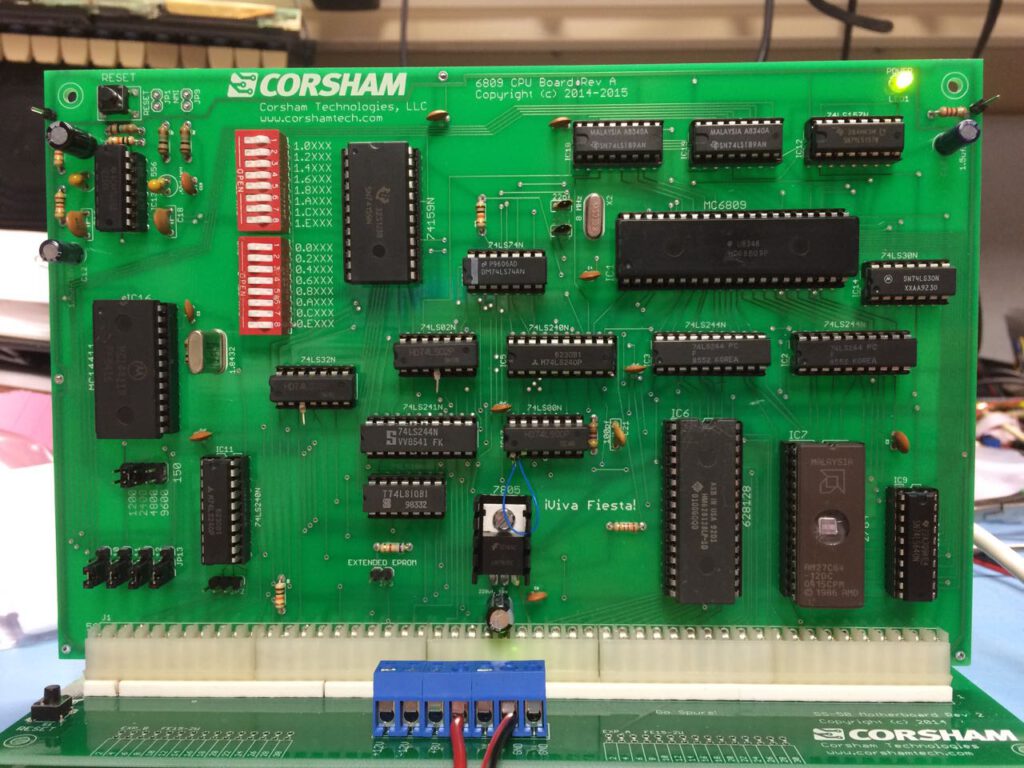

– 68B09 processor running at 2 MHz.

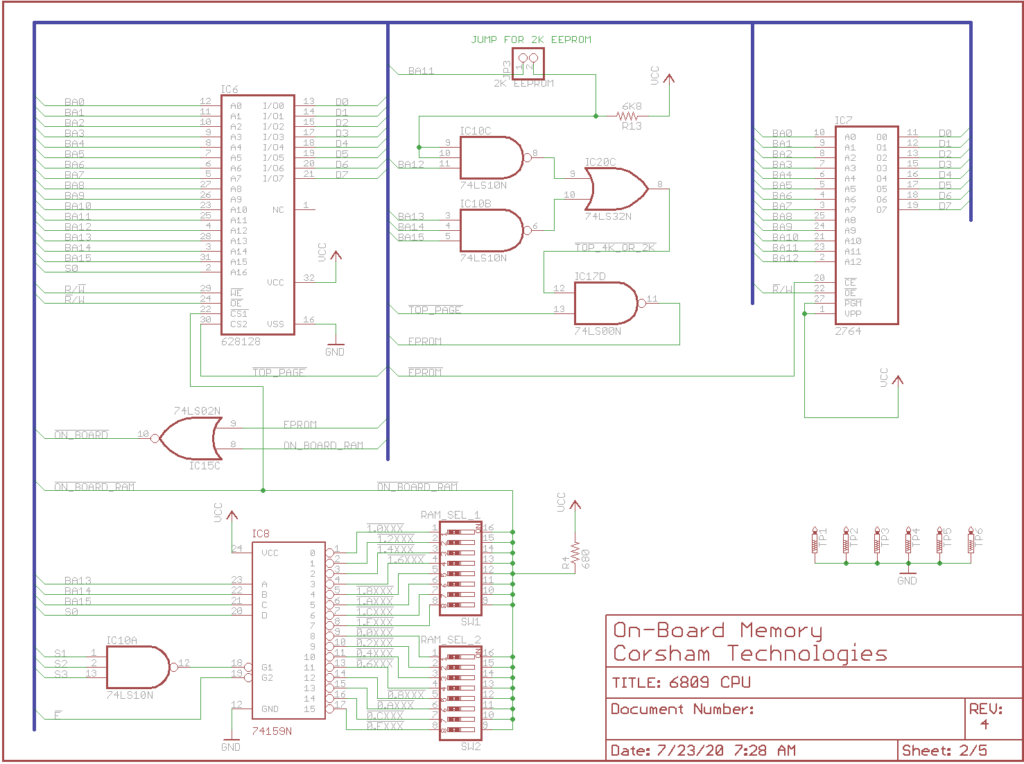

4- K EPROM – SBUG occupies upper 2K, and the lower 2K is available. We usually put either a Tiny BASIC or SD card subroutines there, but it can be replaced with user code.

– Switch allows disabling the lower 2K of the EPROM.

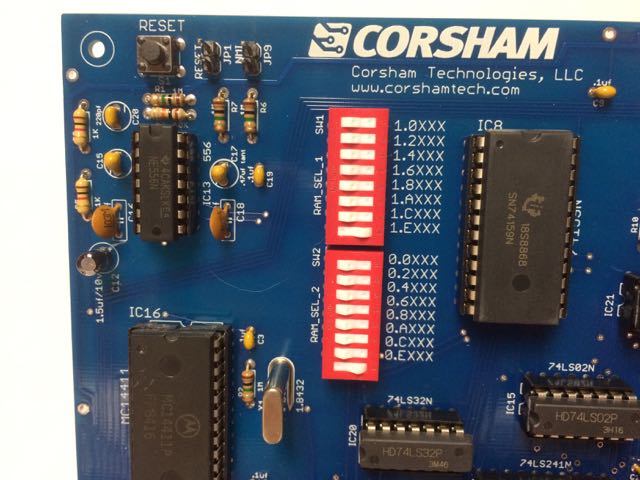

– 128K RAM – Extended memory banks 0 and 1. Each 8K block can be enabled/disabled via easy to use DIP switches.

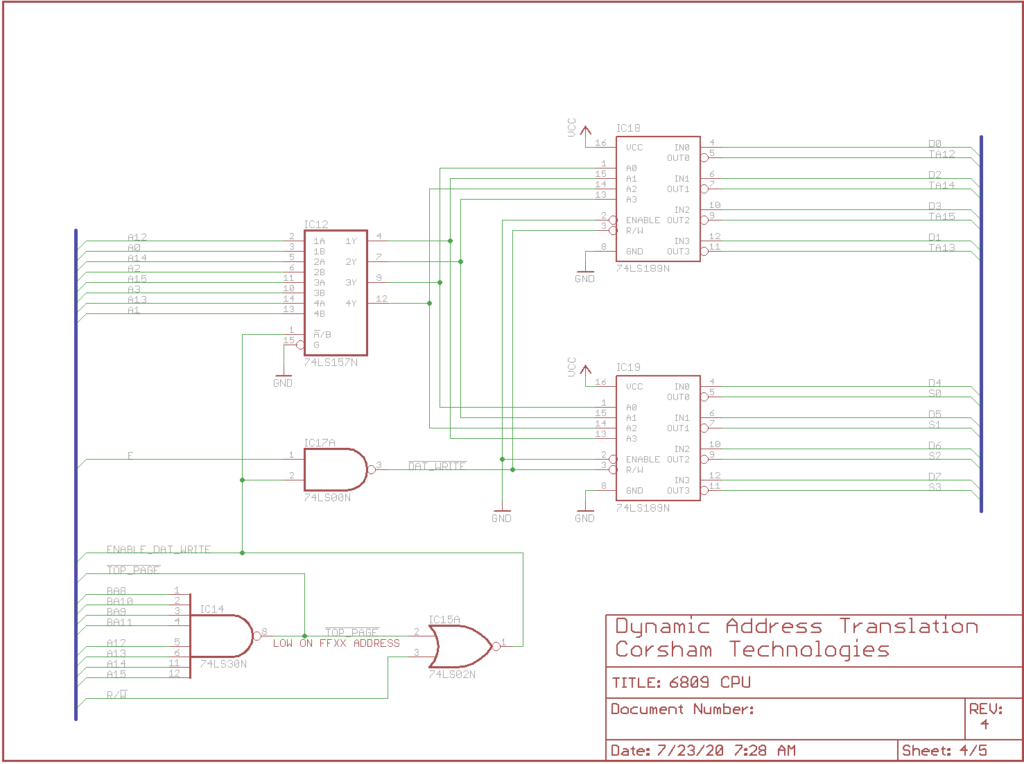

– Support for the extended 20 bit address bus using the same Dynamic Address Translation (DAT) as the original SWTPC board.

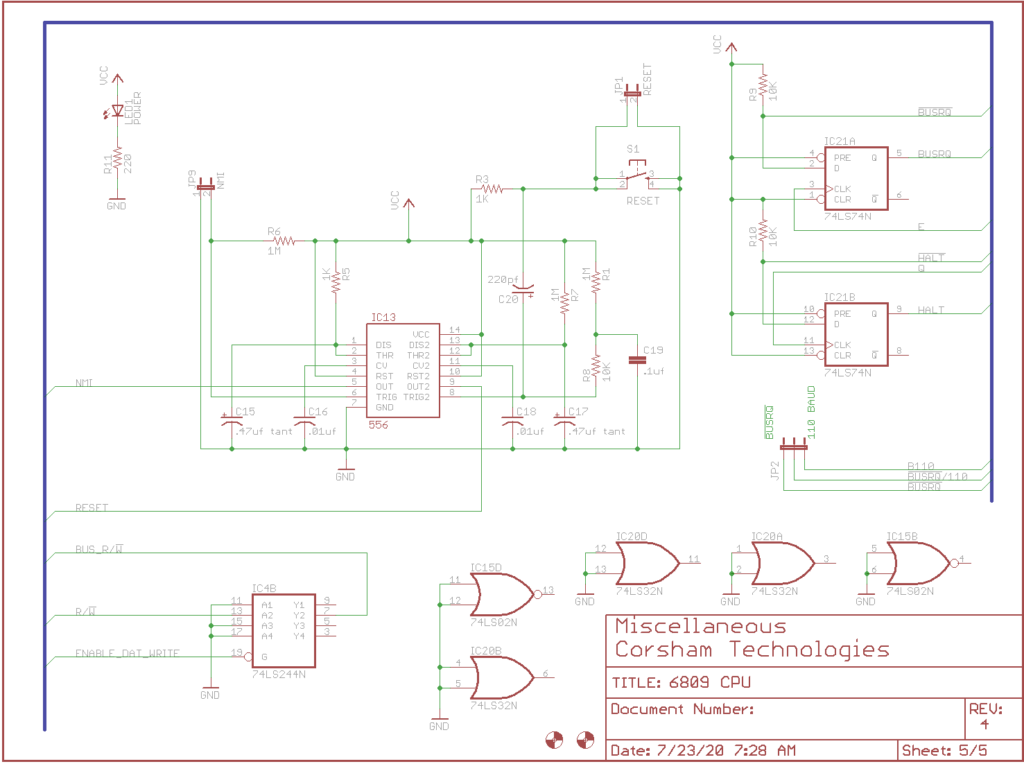

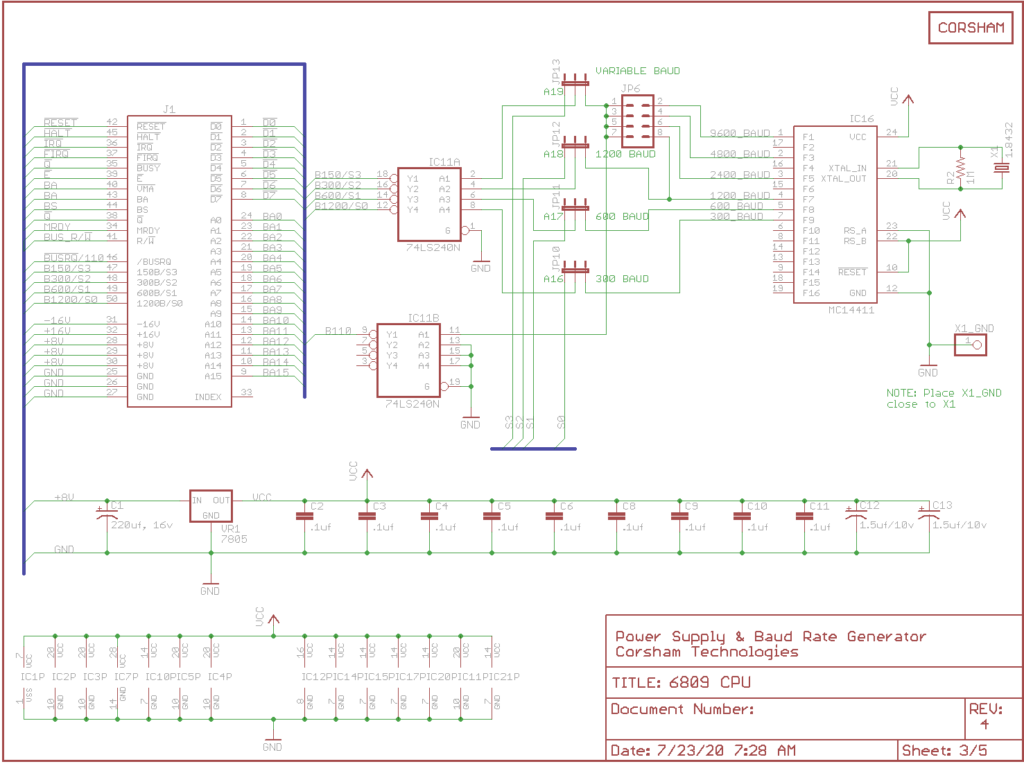

– Jumper selection of either baud rate clocks or address bits for A16 to A19.

– Jumper selection of either baud rate clock or /BUSRQ line.

– On-board RESET button along with headers for external reset and interrupt buttons.

– High quality dual-layer board.

– Off the shelf components: easy to understand, easy to repair, easy to modify.

This shows the jumpers used to select the extended address lines or baud clocks, and clock selection. The jumper block labeled VAR sets the “VAR” clock rate to 1200, 2400, 4800 or 9600 baud (actually x16). The VAR/BUSRQ jumper selects which of those two signals are placed onto bus pin 46, usually the 110 baud clock line.

The other four jumpers select whether A16 to A19 or additional baud rate clocks are placed onto pins 47 to 50. The usual practice is to use all four lines for the extended address bus, then use pin 46 (110 baud/BUSRQ) as the clock for the serial board:

|

SS-50 6809 CPU Manual |

Archive with older revisions (2-5) schematics