As many of you know, I started my journey in microcomputers with a KIM-1 in 1978 which was a 6502 based system. My next machine was an OSI SuperBoard, then an Atari 800, and Apple ][, and my first full-time job was at Franklin Computer Corp where I spent most every day doing 6502 programming., etc.

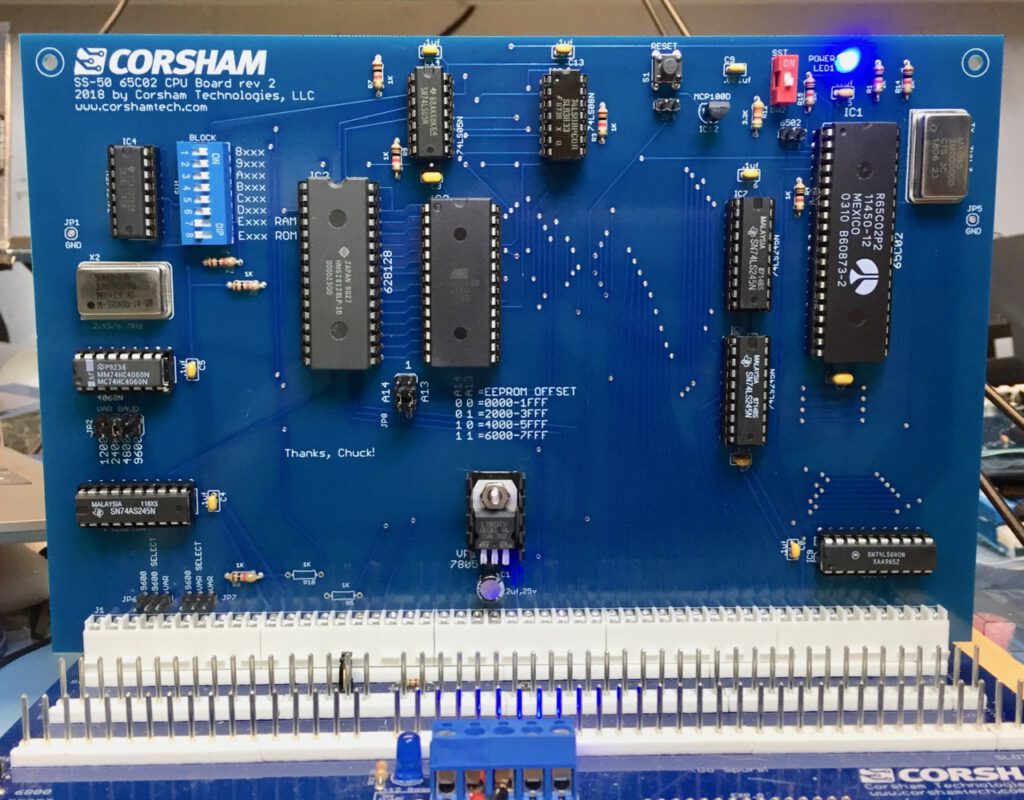

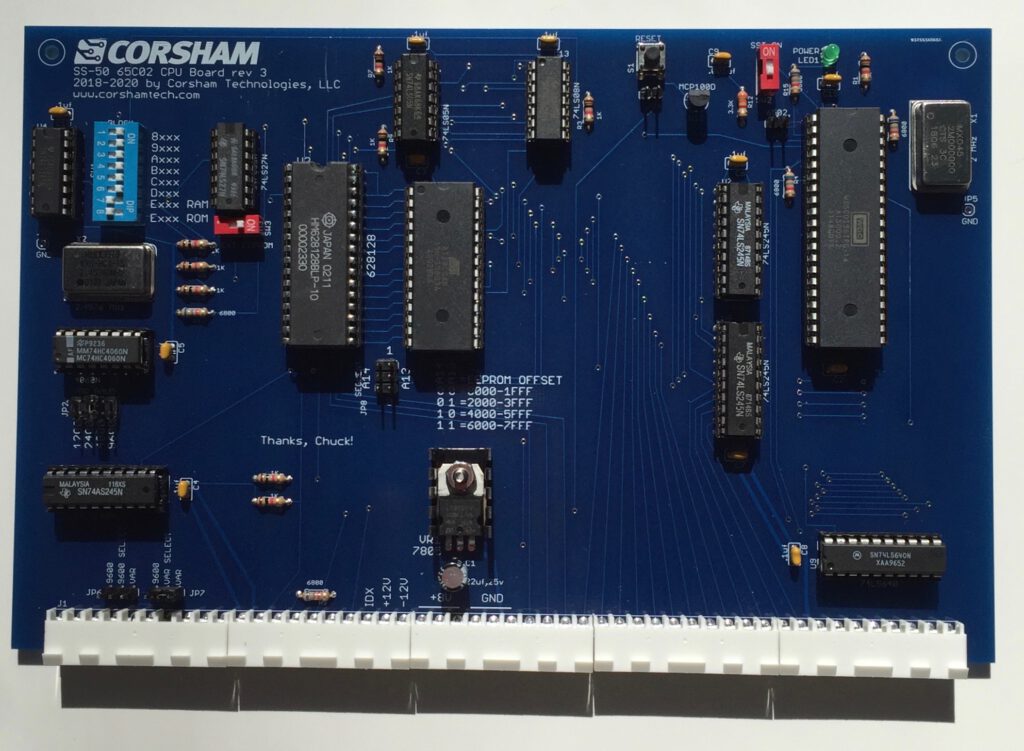

There was at least one commercial board for the SS-50 bus with a 6502, but it was never very popular. Given my interest in this processor I decided to create my own CPU board:

Basic specifications:

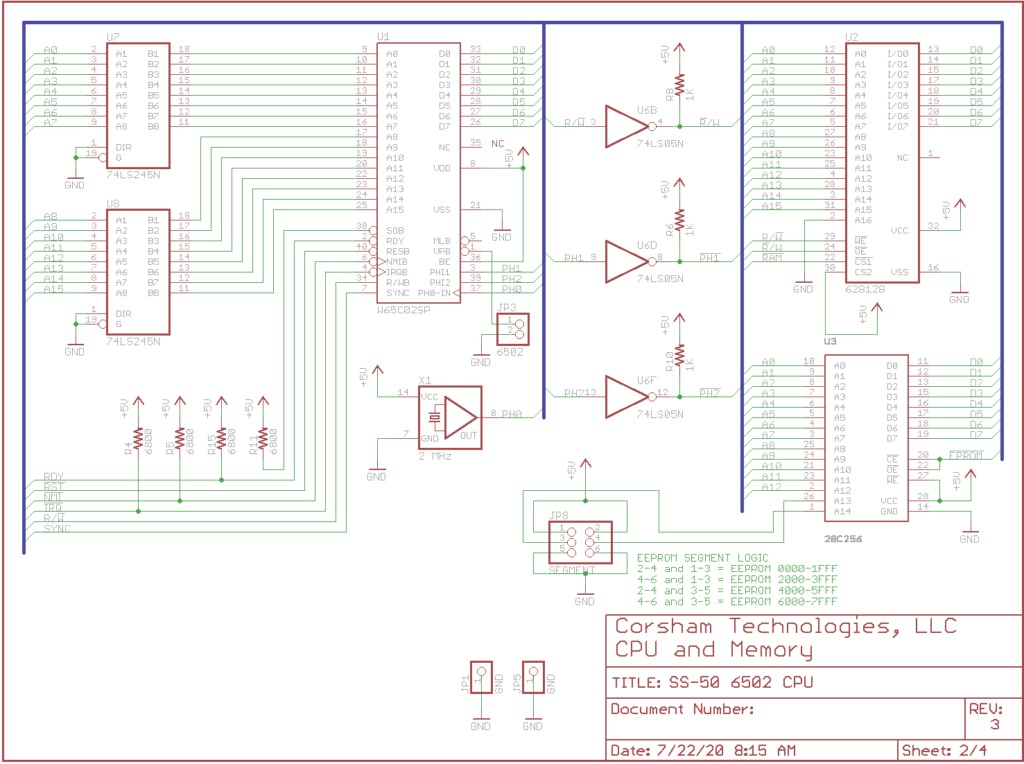

- WDC65C02 processor running at 2 MHz. This is a genuine WDC chip, nothing with an unknown history that came from who knows where.

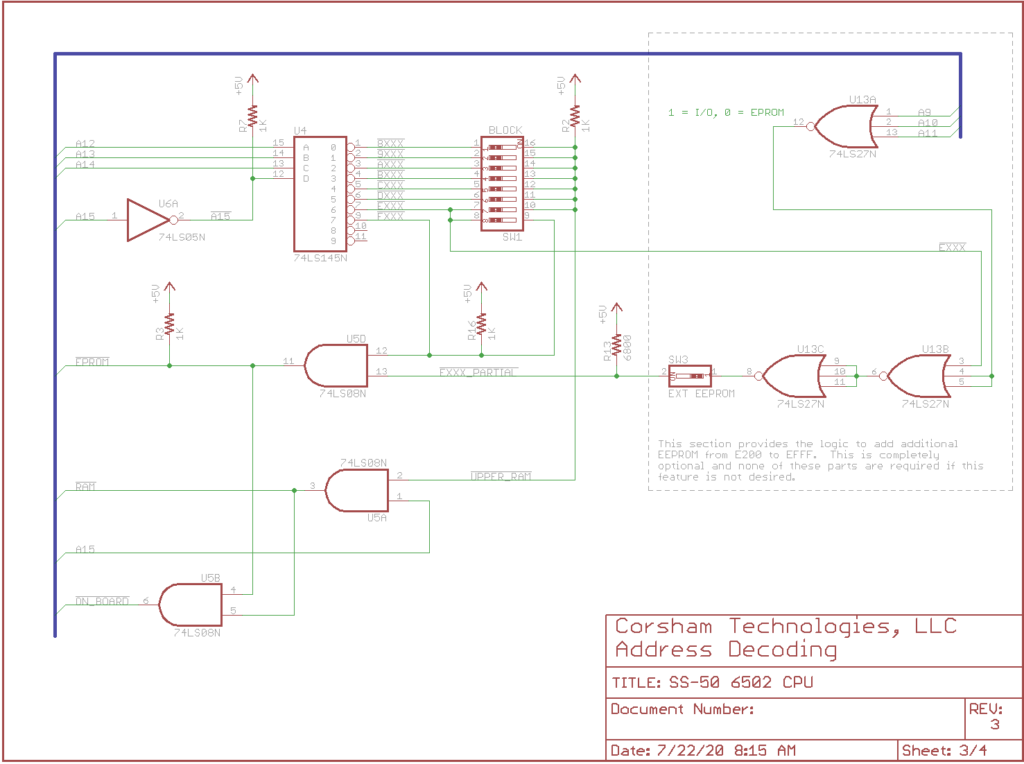

- Full memory map of RAM. 0000-7FFF is always RAM while each 4K block in the upper 32K can be turned on or off.

- EEPROM from F000 to FFFF.

- Optionally, EEPROM can be enabled from E200-EFFF via a DIP switch.

- We include a 28C64 (8K) EEPROM with CTMON65, but the socket can support 32K EEPROMs and two jumpers select which 8K region is visible.

- A single-step switch is on top of the board. When an opcode fetch occurs outside of the EEPROM, an NMI is generated. Great for writing a single-step monitor.

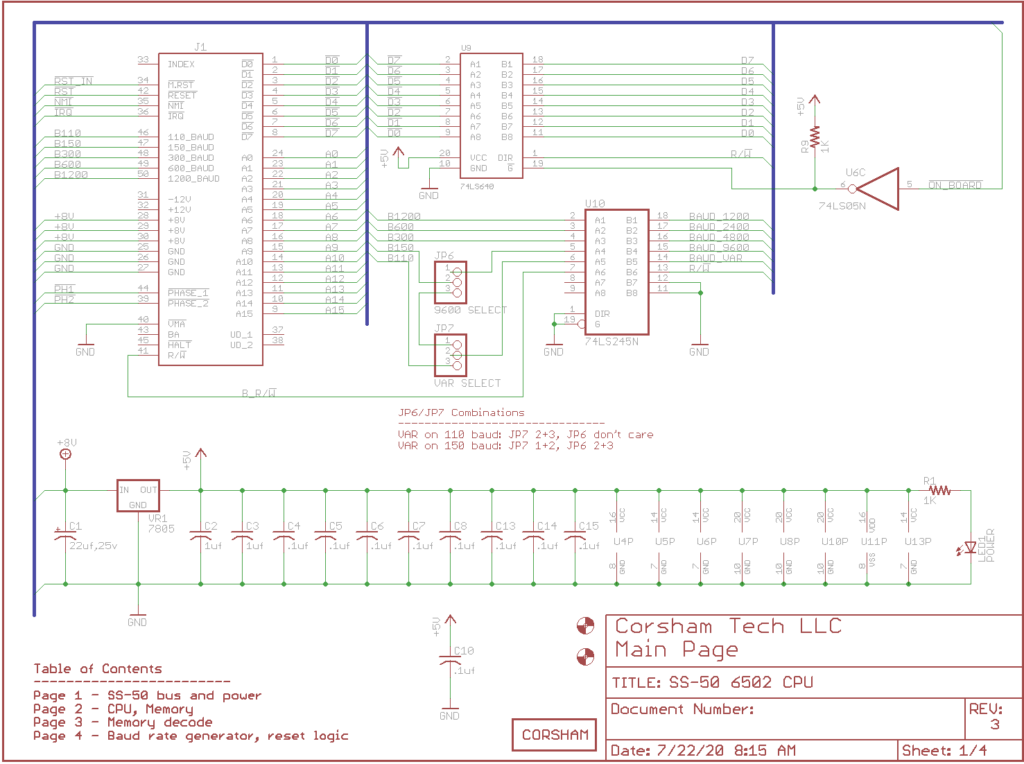

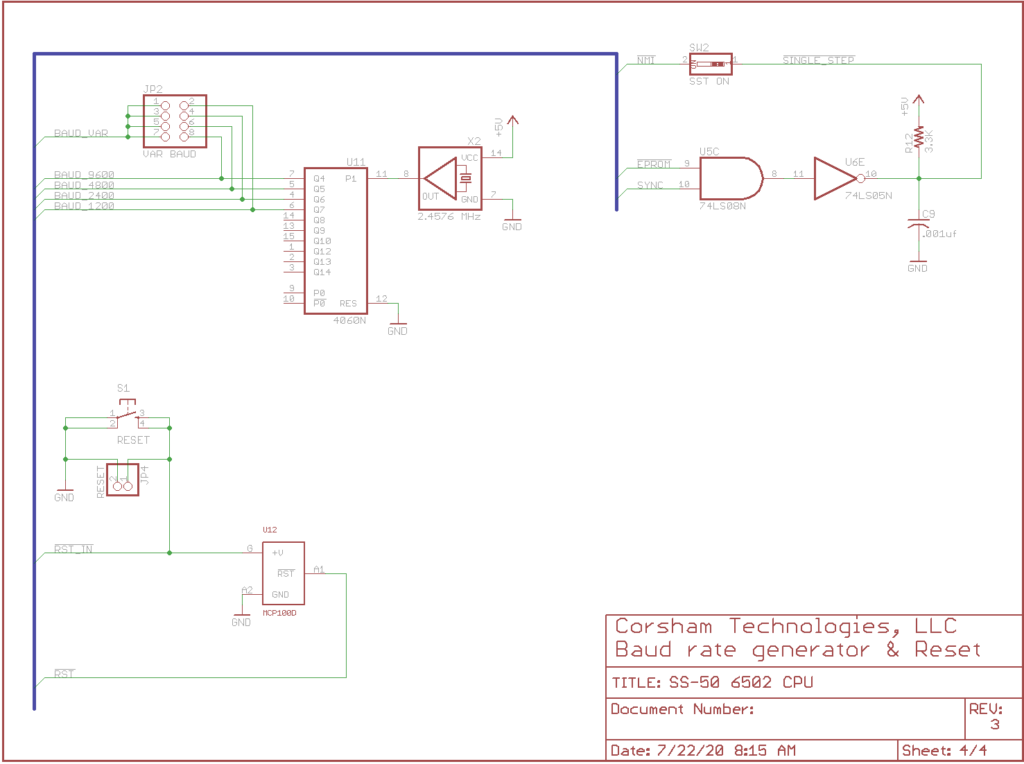

- The baud rate generator products x16 clock for 1200, 2400, 4800 and 9600 baud.

- Power-on reset.

- The monitor source code CTMON65 is available on our Github repository

This is an experimenter’s board as there was no code that I am aware of for a 6502 on the SS-50 bus. It uses the standard SS-30 I/O bus and most of those devices have plenty of example code for the 6800 and/or 6809 to use as templates for writing 65C02 code.