# MEMORY PLUS

AIM - SYM - KIM

# AIM/SYM/KIM USERS

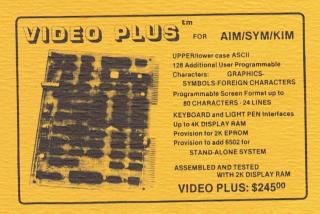

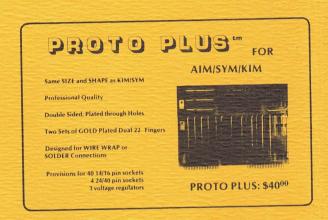

# Meet some other members of our 'ASK' family.

The COMPUTERIST specializes in expansion needs for your AIM/SYM/KIM. We offer a wide variety of support in expansion boards, power supplies, and software. Since we are continuously developing new 6502 based products, please contact us for the latest product and pricing information.

Prices subject to change without notice.

The COMPUTERIST, Inc. P. O. Box 3 So. Chelmsford, MA 01824 617/256-3649

[October 1979]

### Table of Contents

# Warranty and Service

Should you experience difficulty with your MEMORY PLUS board and be unable to diagnose or correct the problem, you may return the board to The COMPUTERIST for repair. MEMORY PLUS is warranted by The COMPUTERIST against defects in workmanship and materials for a period of ninety (90) days from date of delivery. During the warranty period, The COMPUTERIST will repair or, at its option, replace at no charge components that prove to be defective provided that the board is returned, shipping prepaid, to:

The COMPUTERIST, Inc.

Service Department

34 Chelmsford Street

Chelmsford, MA 01824

This warranty does not apply if the board has been damaged by accident or misuse, or as a result of repairs or modification made by other than authorized personnel at the above service facility. No other warranty is expressed or implied. The COMPUTERIST is not liable for consequential damages.

Beyond the ninety (90) day warranty period, MEMORY PLUS boards will be repaired for a reasonable service fee. All service work performed by The COMPUTERIST beyond the warranty period is warranted for an additional ninety (90) day period after shipment of the repaired board.

It is the customer's responsibility to return the board with shipping charges prepaid to the above service facility. For in-warranty service, the board will be returned to the customer, shipping prepaid, by the fastest economical carrier. For out-of-warranty service, the customer will pay for shipping charges both ways. The repaired board will be returned to the customer C.O.D. unless the repairs and shipping charges are prepaid by the customer.

All material in the MEMORY PLUS Manual is Copyright © 1979 by The COMPUTERIST Inc.

#### INTRODUCTION

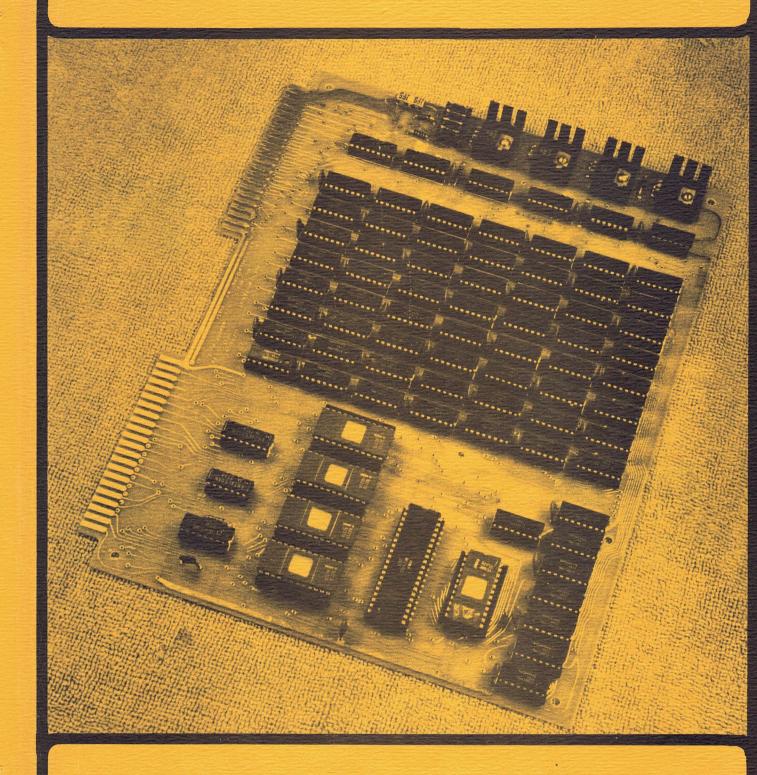

MEMORY PLUS<sup>tm</sup> has been designed specifically to work with the KIM-1, SYM-1, AIM 65 microcomputers. It greatly extends the power of the basic MICRO by providing four major facilities:

RAM Memory: 8K bytes of low power 2102 type static RAM.

ROM Memory: Sockets and decoding for up to 8K bytes of 2716 type erasable programmable read-only memory - EPROM

Versatile Interface Adapter: Two 8-bit programmable I/O ports with additional handshaking lines. Two sophisticated timers.

A serial-to-parallel and parallel-to-serial shift register.

EPROM Programmer: All components required to programming the INTEL type 2716 EPROM. This includes a programming socket, all hardware, a +25 volt regulator circuit, and an EPROM Programming program on cassette tape.

Other features of MEMORY PLUS include:

On board +5 volt regulators: User need only supply +8 to +10 unregulated power for running everything on MEMORY PLUS except the EPROM Programmer.

Provision for Battery Backup: External batteries may be connected to MEMORY PLUS to maintain power to the RAMs during any power outage, thereby automatically preserving the contents of the RAM.

All ICs are socketted: This means that in the event of a chip failure in the field the user may often be able to correct the problem immediately and locally, and not be required to ship the board back to the factory for service.

May be mounted directly underneath the KIM-1 or SYM-1. Mounting holes are provided so that the board may be attached to the existing holes on the KIM-1 or SYM-1.

Compatible with the KIM-4 Bus: The basic connections between the MICRO and MEMORY PLUS are identical to those between the KIM-1 and KIM-2/KIM-3. Therefore, users who have already designed and/or built systems based on these KIM boards may easily adapt to the MEMORY PLUS board.

Provision for Off-the-board EPROM Programming Socket: All of the lines necessary to add an external EPROM Programming Socket are available at the MEMORY PLUS application connector.

Fully Assembled, Burned-in, and Tested: Ready to go.

Switch Selectable Addressing: Starting address for RAM and ROM are set by rotary switches on the board. They may each start at any 8K boundary (2K hex).

The quickest way to get your new MEMORY PLUS board "up and running" with your MICRO is to take your time and follow all of the steps outlined below.

- 1. Carefully unpack your MEMORY PLUS board from its individual box, padding, and protective anti-static wrapping. While none of the components on this board are unusually susceptible to static, any chip can be damaged (destroyed) by a large static shock. So, take some care about avoiding static buildup.

- 2. Examine the board for any visible damage which may have occurred in shipping. Push all IC's firmly into their sockets. Unbend any capacitors which have been bent.

- 3. Read briefly the entire MEMORY PLUS manual. Pay particular attention to the main sections on "POWER", "RAM Memory", "EPROM Memory", and "VERSATILE INTERFACE ADAPTER", but do not try to memorize everything.

- 4. Build the required connector cables following the wiring list labelled "MEMORY PLUS to MICRO Connections".

- 4A <u>KIM-1 ONLY</u>; If you are only planning to use the RAM memory to start, then only the expansion connector cable is required. A wire running from pin E-16 of MP to A-K of KIM for the DECODE. Remember to remove the wire you currently have between pin A-K of KIM and pin A-1 of KIM which grounds the DECODE signal for an unexpanded system.

- 5. Carefully check the cable you built for any errors or bad connections.

- 6. Set up your power for MEMORY PLUS in one of the following ways:

- a. If you have a single +5V supply which is going to run both the MICRO and MEMORY PLUS (it must be capable of about 3.5 amps), then the following connections should be made:

MP E-21 to MICRO E-21

MP E-Y to MICRO E-21

MP A-A to MICRO A-A

The Header should be positioned with no wire near the edge of the board.

- b. If you have a separate +5 regulated supply for MEMORY PLUS, the above connections must <u>not</u> be made. The header should be positioned with no wire near the edge of the board. Attach supply to MP E-21/E-Y.

- c. If you have a +8 to +10 unregulated supply, then the above connections must  $\underline{not}$  be made. The header should be positioned with a wire near the edge of the board. Attach supply to MP E-19/E-20.

- 7. Connect the MICRO and MEMORY PLUS together via the cables you have made.

- 8. Set the RAM Select Switch to the 2000 position.

- 9. Turn on the power supply. Using the MICRO monitor, examine and modify a few RAM locations to verify that they basically work. With the RAM switch set to 2000, locations 2000 through 3FFF are accessible. If you are unable to examine and modify these locations, then check steps 2 to 8 for any errors. If you can not find anything you did wrong, then go to the section on "MEMORY PLUS Testing and Field Repair" on page 16.

- 10. If the above preliminary examination of RAM memory is successful, then you are ready to run a more rigorous memory test. Follow the instructions in the section on "RAM Memory Test". If these tests work, and all you plan to use on MEMORY PLUS is the RAM, then you are done with the initial set up and check out.

- 11. If you plan to use the EPROM Programmer, you must build the cable that goes between the MICRO and MEMORY PLUS application connectors if you have not already done so. Follow the wiring list labelled "MEMORY PLUS to MICRO Connections". Carefully check the cable you built and review the power connections as discussed in step 6 above.

- 12. Connect the MICRO and MEMORY PLUS together with the application cable.

- 13. No specific tests are provided for testing the VIA. If you wish to test this chip, read the section on "VERSATILE INTERFACE ADAPTER" and the "MCS6522 VERSATILE INTERFACE ADAPTER Data Sheet" contained in your MICRO Manual. You may then devise your own tests dependent on how you intend to use the VIA chip.

- 14. The only simple way to test the EPROM Programmer is to program an EPROM. The EPROM Programmer requires a +25 volts at 30 milliamps. The best way to provide this is by using the on board regulator circuit. A +27 to +30V unregulated supply can be connected to pin E-3 of the MEMORY PLUS expansion connector. See the section on "EPROM Programming" for details. This will provide about +24.7V for EPROM programming and will prevent over voltages which can destroy an EPROM. Follow the instructions in the "EPROM Programming" section and program an EPROM.

- 15. Once you have a programmed EPROM, you can place it into the correct EPROM socket and try to use it. The "standard" addresses for the MEMORY PLUS board are COOO C7FF, C800 CFFF, D000 D7FF, and D800 DFFF. Set the ROM Select Switch to the desired 8K starting address. Since the EPROM Programmer Program verified as it programmed, the contents should be correct. If not, then there is probably a problem in where you have placed the EPROM (wrong socket) or which direction you have inserted the EPROM (pin 1 goes upper right corner). If the contents of the EPROM look okay, then execute the code to determine if it runs correctly. If the code looks correct, then it should run properly.

- 16. Congratulations. You now have an expanded MICRO system with a lot of new capabilities. You should now make yourself more familiar with the MEMORY PLUS facilities by re-reading the documentation, particularly the VIA Data Sheet.

# MEMORY PLUS to MICRO Connections

|   |                         | MEMORY<br>PLUS | MICRO        | Expansion   | Connector     | MEMORY<br>PLUS | MICRO    |

|---|-------------------------|----------------|--------------|-------------|---------------|----------------|----------|

|   | Function                | Pin#           | Pin#         |             | Function      | Pin#           | Pin#     |

|   | Ground                  | E-1            | E-22         |             | Ground        | E-A            | E-22     |

| * | +5V Battery             | E-2            |              | 1 -         | ABO           | E-B            | E-A      |

| * | +27 Unreg.              | E-3            |              | green/wit   | AB1           | E-C            | E-B      |

|   | IRQ                     | E-4            | E-4          |             | AB2           | E-D            | E-C      |

|   | 1114                    | E-5            |              |             | AB3           | E-E            | E-D      |

|   |                         | E-6            |              |             | AB4           | E-F            | E-E      |

|   | RST                     | E-7            | E-7          |             | AB5           | E-H            | E-F      |

|   | DB7                     | E-8            | E-8          |             | AB6           | E-J            | E-H      |

|   | DB6                     | E-9            | E-9          |             | AB7           | E-K            | E-J      |

|   | DB5                     | E-10           | E-10         |             | AB8           | E-L            | E-K      |

|   | DB4                     | E-11           | E-11         |             | AB9           | E-M            | E-L      |

|   | DB3                     | E-12           | E-12         |             | AB10          | E-N            | E-M      |

|   | DB2                     | E-13           | E-13         |             | AB11          | E-P            | E-N      |

|   | DB1                     | E-14           | E-14         |             | AB12          | E-R            | E-P      |

|   | DBO                     | E-15           | E-15         |             | AB13          | E-S            | E-R      |

|   | DECODE                  | E-16           | A-K          |             | AB14          | E-T            | E-S      |

|   |                         | E-17           | A-K          |             | AB15          | E-U-           | E-T      |

|   |                         | E-18           |              |             | Phase 2       | E-V            | E-U      |

|   | +8V Unreg.              | E-19           |              | Blaun       | Read/Write    | E-W            | E-V      |

|   | +8V Unreg.              | E-20           |              |             | Phase 2       | E-X            | E-Y      |

|   | +5V Regulated           |                | E-21         | roon .      | +5V Regulated |                | E-21     |

|   | Ground                  | E-22           | E-22         | ZWART       | Ground        | E-Z            | E-22     |

|   |                         | MEMORY<br>PLUS | MICRO        | Application | on Connector  | MEMORY<br>PLUS | MICRO    |

|   | Function                | Pin#           | Pin#         |             | Function      | Pin#           | Pin#     |

|   | Ground                  | A-1            | A-1          |             | +5V Regulated | A-A            | A-A      |

|   | MPA1                    | A-2            |              |             | MPB6          | A-B            |          |

|   | MPA2                    | A-3            |              |             |               | A-C            |          |

|   | MPA3                    | A-4            |              |             |               | A-D            |          |

|   | MPA4                    | A-5            |              |             | MCA 2         | A-E            |          |

|   | MPA5                    | A-6            |              |             | MCA.          | A-F            |          |

|   | MPA6                    | A-7            |              |             | MCB1          | A-H            |          |

|   | MPA7                    | A-8            |              |             | MCB2          | A-J            | te bonce |

|   | MPB0                    | A-9            |              |             | DECODE        | A-K            | A-K      |

|   | MPB1                    | A-10           | Lat. State 1 |             |               | A-L            |          |

|   | MPB2                    | A-11           | -X SEE       | IMPERTHAT   | WAZNING       | A-M            |          |

|   | MPB3                    | A-12           | NOTE         | ON PACE 12  | ABOUT .       | A-N            |          |

|   | MPB4                    | A-13           | F-2          | /E-3 CONN   | IGO TOUR      | A-P            |          |

|   | MPAO                    | A-14           | TO LUEN      | 12-3 001111 |               | A-R            |          |

|   | MPB7                    | A-15           |              |             |               | A-S            |          |

|   | MPB5                    | A-16           |              |             |               | A-T            |          |

|   | MCB2                    | A-17           |              |             |               | A-U            |          |

|   | 1) () A ()              | A-18           |              |             |               | A-V            |          |

|   | PRA8                    | A-19           | A-9          |             |               | A-W            |          |

|   | PRA9                    | A-20           | A-10         |             |               | A-X            |          |

|   | PRA10<br>+25V Regulated | A-21           | A-11         |             |               | A-Y            |          |

|   | +COV REBUIATE           | 1 H-CC         |              |             |               | A-Z            |          |

<sup>\*</sup> One of the two DECODE lines must be connected to the KIM-1. This is not required on the SYM-1 or AIM 65.

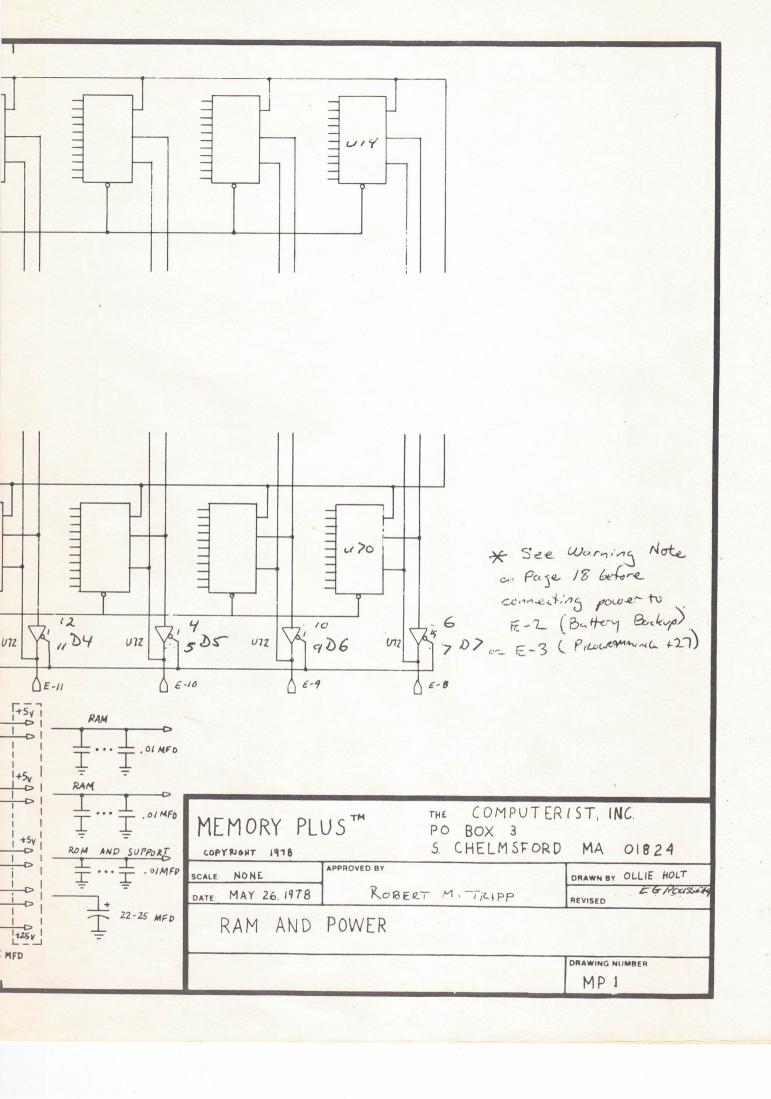

The power requirements for MEMORY PLUS are simple and on-board regulators are provided to make powering the board even easier. Essentially the board requires only +5 volts at about 2.0 amps. While the actual current requirements will vary slightly with the particular components on any board, the table below shows the individual and collective power requirements.

| Component         | #   | T | ypical | Ma  | ximum | Measured | Max Total | Meas. | Total |

|-------------------|-----|---|--------|-----|-------|----------|-----------|-------|-------|

| 74LS00<br>74LS04  | 1   |   |        |     | 8     | 3        | 8         | 3 4   |       |

| 74LS32<br>74LS138 | 1 3 |   | 5      |     | 10    | 6        | 10<br>30  | 18    |       |

| 74LS367           | 3   |   | 14     |     | 24    | 17       | 72        | 51    |       |

| 2716              | 4   |   | 57     | 1   | 05    | 45       | 420       | 180   |       |

| 6522<br>M-1       | 1   |   | 50     | [A] | 60    | 52       | 60        | 52    |       |

| 2102L [B]         | 32  |   | 14     |     | 22    | 14       | 704       | 448   |       |

| 2102L 4-8         | 32  |   | 14     |     | 22    | 14       | 704       | 448   |       |

| Total System      |     |   |        |     |       |          | 2016      | 1206  | [C]   |

Notes: All current values in milliamps.

- [A] Value as estimated by an engineer at MOS Technology.

- [B] 2102Ls are split into two sections of 4K RAM each in the table for purposes of discussion below.

- [C] Measurements were taken with an inexpensive meter and should be only used as a guide to the system current requirements.

- [D] The above values were obtained with Fairchild 21L02s. The values may vary with other 21L02s produced by other manufacturers and supplied with your MEMORY PLUS board.

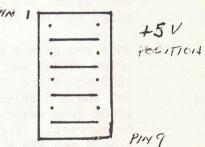

Regulated +5 Volt Supply. If the MEMORY PLUS is to be powered by regulated +5 volts, then the supply should be connected to pins E-21 and E-Y on the MEMORY PLUS expansion connector. The supply should be capable of supplying at least 2.0 amps in addition to any other board it is driving such as the KIM-1. The Header at the top of the board should be positioned so that the bus wires are away from the top of the board and the Header notched corner is positioned at pin 9.

Unregulated +8 to +10 Volt Supply. If the MEMORY PLUS is to be powered by unregulated +8 to +10 volts, then the supply should be connected to pins E-19 and E-20 on the MEMORY PLUS expansion connector. The supply should be capable of supplying at least 2.5 amps. This supply is distributed to three +5 volt regulators which each handle a separate section of the board.

Regulator Q4 supplies the high 4K of 2102L RAM with 448 to 704 milliamps.

Regulator Q5 supplies all support chips, the 2716s and the 6522 with 310 to 608 milliamps.

Regulator Q6 supplies the low 4K of 2102L RAM with 448 to 704 milliamps.

The Header at the top of the board should be positioned so that the bus wires are near the top of the board and the Header notched corner is positioned at pin 1.

The only other power requirement for the MEMORY PLUS board is +25 volts at 30 milliamps during programming of an EPROM. This voltage may be provided as either regulated +25 volt or unregulated +28 to +30 volts.

Regulated +25 Volt Supply. Programming of the INTEL 2716 EPROM requires +25V. This may be attached to pin A-22 of the MEMORY PLUS application connector. Care must be taken to assure that the voltage is within the limits of +24 to +26 volts. A higher voltage will destroy the EPROM as both the INTEL documentation and my own personal experience can attest.

- Unregulated +27 to +30 Volt Supply. MEMORY PLUS provides a circuit with a +24 volt regulator and a diode to produce a regulated +24.7 volts from an unregulated +27 to +30 volt supply. The unregulated supply, which may be three +9 volt transistor radio type batteries, is attached to pin E-3 of the MEMORY PLUS expansion connector. Since the programming voltage is so critical and since an over voltage can destroy an EPROM, use of this on board regulator is recommended. The three battery clips provided in the Accessory Bag are for the purpose of hooking up three +9 volt batteries.

- \* Battery Backup. Since it is often desirable to be able to protect the contents of the RAM memory during a transient power interruption, or for longer periods of time, a provision has been made for battery backup to be connected to the MEMORY PLUS board. The batteries must be capable of providing between about 3.5 and 4.5 volts. They are connected to pin E-2 of the MEMORY PLUS expansion connector. There are diodes in the circuit which prevent current from being drawn from the batteries during normal system functioning. When the power drops, however, the batteries will automatically start supplying the required current. The amount of current will depend on the basic system configuration. If the MEMORY PLUS board is being run from +5 volts, then the batteries must supply the entire board. If the board is being run from the +8 to +10 volt regulators, then the battery backup will only run the RAM memory chips. This will result in a lower current drain on the batteries. The length of time that the system will retain its RAM contents on battery power will be a function of the configuration and the capacity of the batteries.

\* SER IMPORTANT WARRING NOTE ON PAGE 18.

# Cassette Loading Instructions

The cassette tape is recorded in standard KIM format at the normal rate. The programs have been written so that they will run on a KIM-1, SYM-1 or AIM 65 with no modification.

The MEMORY TEST is the first program on the tape. It has program ID = 10. It loads into locations 0000 through 00D8. It is set up to test memory from 2000 to 3FFF. The starting address of the program is 0002. See pages 21 to 23 of this manual for the MEMORY TEST Source Listing and page 20 for instructions on using the program.

The PROM PROGRAMMER is the second program on the tape. It has Program ID = 20. It loads into locations 0000 through 00E7. The programming parameters must be set up in locations 0000 through 0005 as outlined in the section on EPROM Programming, pages 11 to 13. The starting address of the program is 0011. Complete Source Listings are located on pages 14 through 16 of this manual.

# RAM Memory

The Random Access Memory (RAM) used with MEMORY PLUS is 2102-type static RAM. Each 2102 chip contains 1024 bits of memory. Any single bit is directly addressable. By addressing eight chips in parallel, an eight bit word is accessed. It takes eight 2102 chips to provide 1024 8-bit bytes. The MEMORY PLUS provides 8K bytes of 8-bit RAM (actually 8192 bytes). This requires 64 2102 chips: eight chips per 1K times eight K.

The 2102 chips used with MEMORY PLUS are Synertek 21L02B or equivalent. This version of 2102 has the following basic parameters:

SPEED: 450 nanosecond access time

POWER: 30 milliamp worst case (these are "low power" chips)

single +5 voltage required

The MEMORY PLUS RAM is organized into a single contiguous 8K block of memory. The location of the RAM in the MICRO addressing space is defined by a switch which may be set to start at any 8K boundary (2K hex boundary). Looking at the board with the regulators at the top, the RAM select switch is the left switch of the pair of rotary switches. Using the flat side of the switch as the position indicator, the addresses are set as follows:

|                                                     |   | 4   |     |          | 4   |   |

|-----------------------------------------------------|---|-----|-----|----------|-----|---|

|                                                     | 6 |     | 2   | E        |     | 6 |

| On-board Address Select<br>Switches for RAM and ROM | 8 | RAM | Not | Selected | ROM | 8 |

|                                                     | A | С   | E   | 2        | С   | A |

The address associated with each position is:

| 2K<br>4K | 2000 |    |      | Assumed as the RAM address in this manual.                                                          |

|----------|------|----|------|-----------------------------------------------------------------------------------------------------|

| 6K       | 6000 | to | 7FFF |                                                                                                     |

| 8K       | 8000 | to | 9FFF |                                                                                                     |

| AK       | A000 | to | BFFF |                                                                                                     |

| CK       | C000 | to | DFFF | Assumed as the ROM address in this manual.                                                          |

| EK       | E000 |    |      | Not normally used for RAM since interrupt vectors must be defined in FFFA to FFFF if this memory is |

|          |      |    |      | addressed. See note in EPROM Memory about using this space for EPROM.                               |

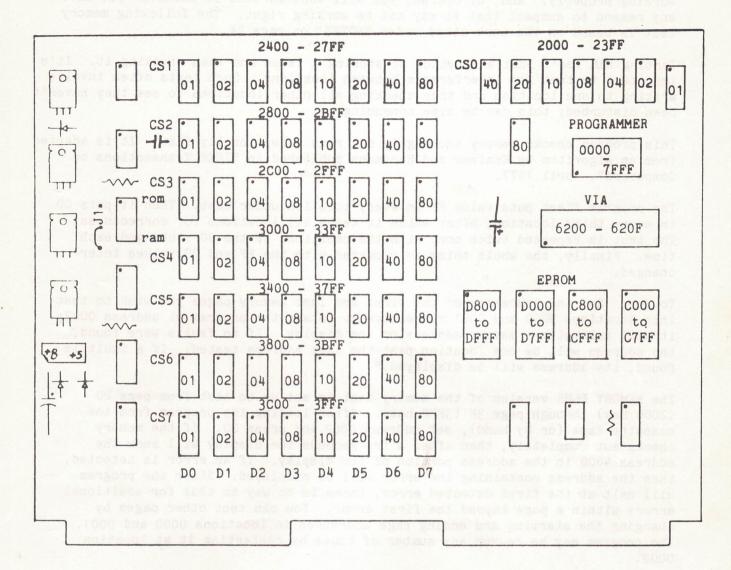

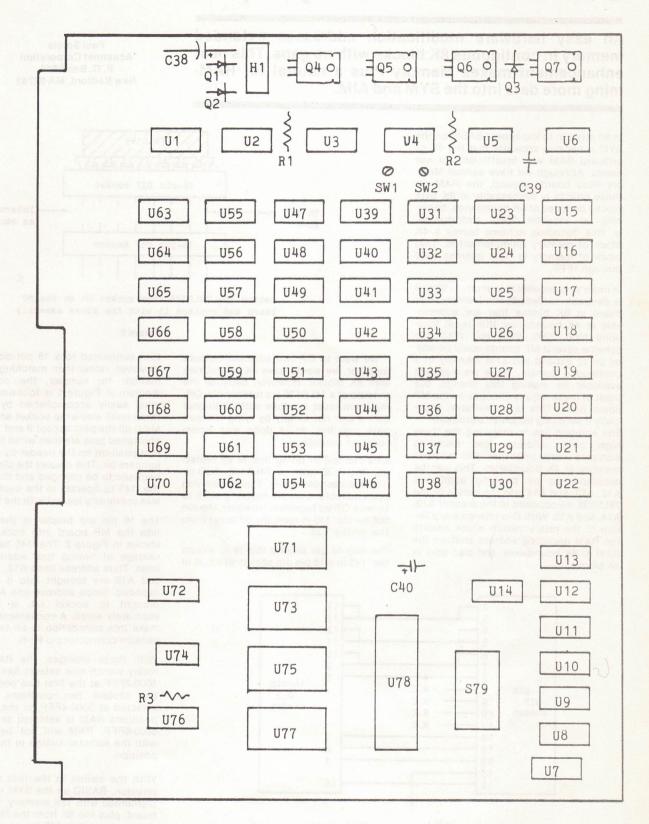

The exact layout of the individual RAM chips may be found in a diagram in the section on "MEMORY PLUS Testing and Field Repair".

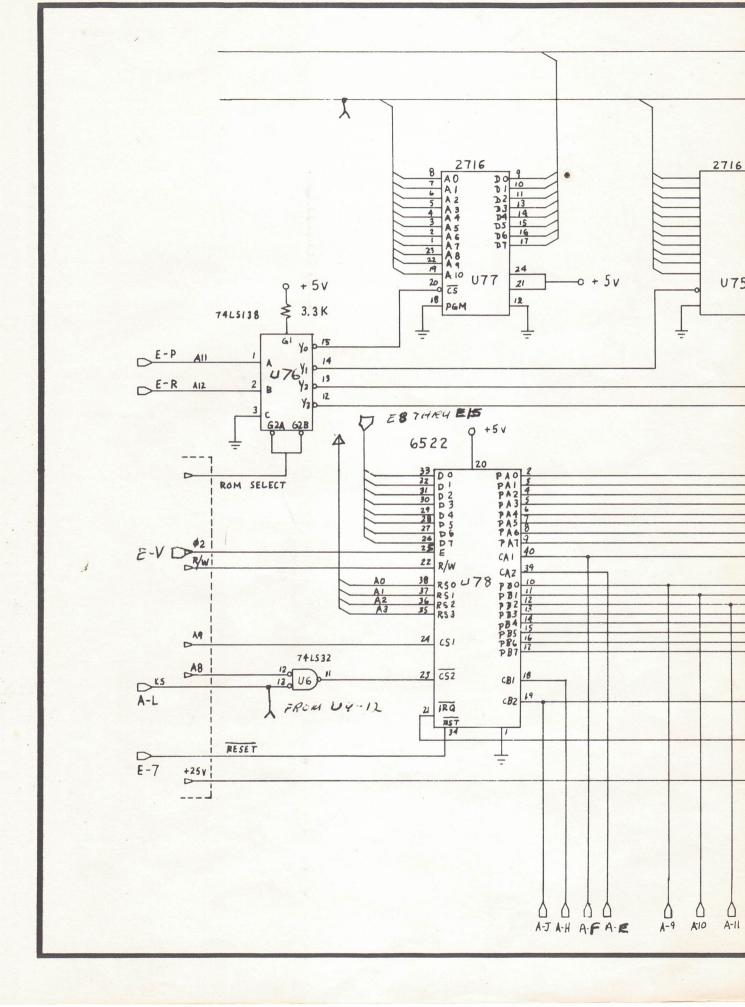

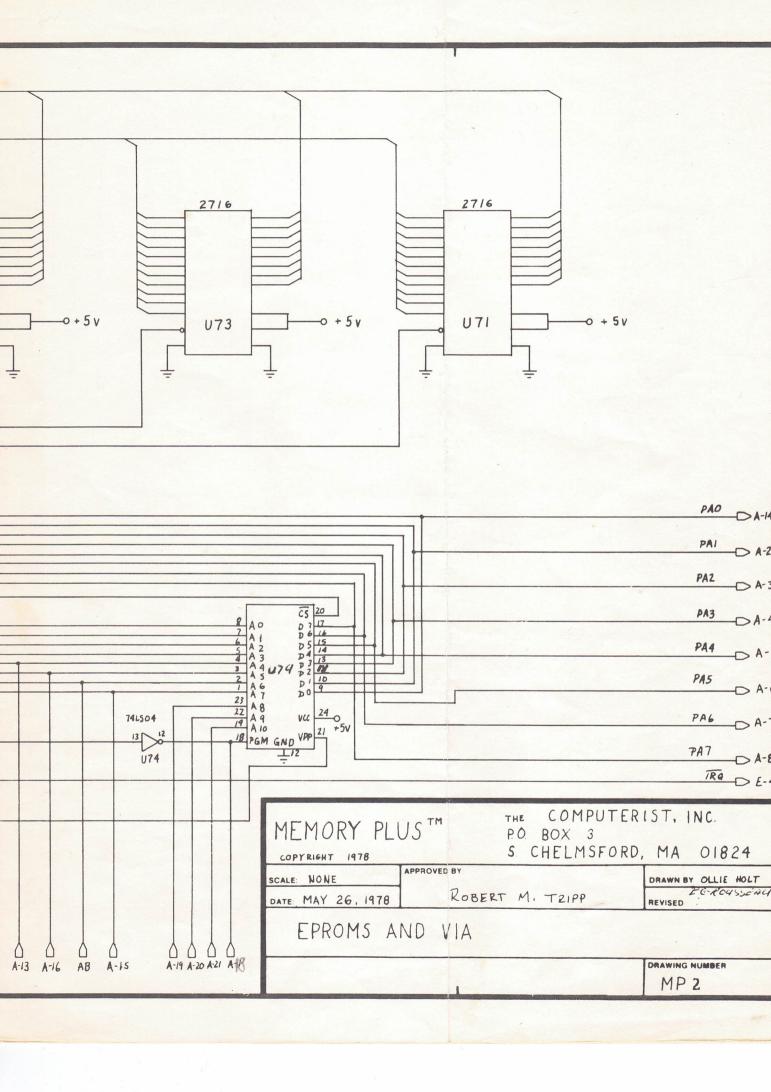

# EPROM Memory

The Erasable Programmable Read-Only Memory (EPROM) used with MEMORY PLUS is an ultraviolet erasable and electrically programmable 2716 type ROM. This is a fairly new memory chip. The version used in MEMORY PLUS is made by INTEL. It is not compatible with the 2716 made by some other manufacturers such as Texas Instruments. It may be second sourced by other manufacturers, but be certain that any EPROM you purchase is at least INTEL 2716 compatible. Each 2716 chip contains 16,384 bits of memory. The addressing of the chip is such that data is accessed eight bits at a time. The organization is 2048 bytes of eight bits each. A single 2716 provides 2K bytes of memory. The MEMORY PLUS board has provision for up to four 2716 chips providing for a maximum of 8K bytes of EPROM.

The 2716 chips required for MEMORY PLUS are INTEL 2716 or equivalent (Texas Instrument 2516 but NOT T. I. 2716). This chip has the following basic parameters:

SPEED: 450 nanosecond access time

POWER: 105 milliamp worst case current, and

single +5 volt required

The MEMORY PLUS EPROM is organized into a single contiguous 8K block of memory. The location of the EPROM in the MICRO addressing space is defined by a switch which may be set to start at any 8K boundary (2K hex boundary). See the chart of switch positions on the preceding page. The position is determined by the flat section of the switch.

(KIM 1 ONLY): If, and only if, the "EK" address is used, then the jumper "J1" (located on the top side of component U4) must be changed. The existing jumper etched on the board must be cut and a wire run from the hole nearest the "J" to the hole nearest the "1". This will cause interrupts to be serviced by the FFFx vectors instead of the lFFx KIM-1 vectors.

The EPROM sockets are addressed such that the socket nearest the edge of the board has the lowest address. The exact layout of the individual EPROM chips may be found in a diagram in the section on "MEMORY PLUS Testing and Field Repair".

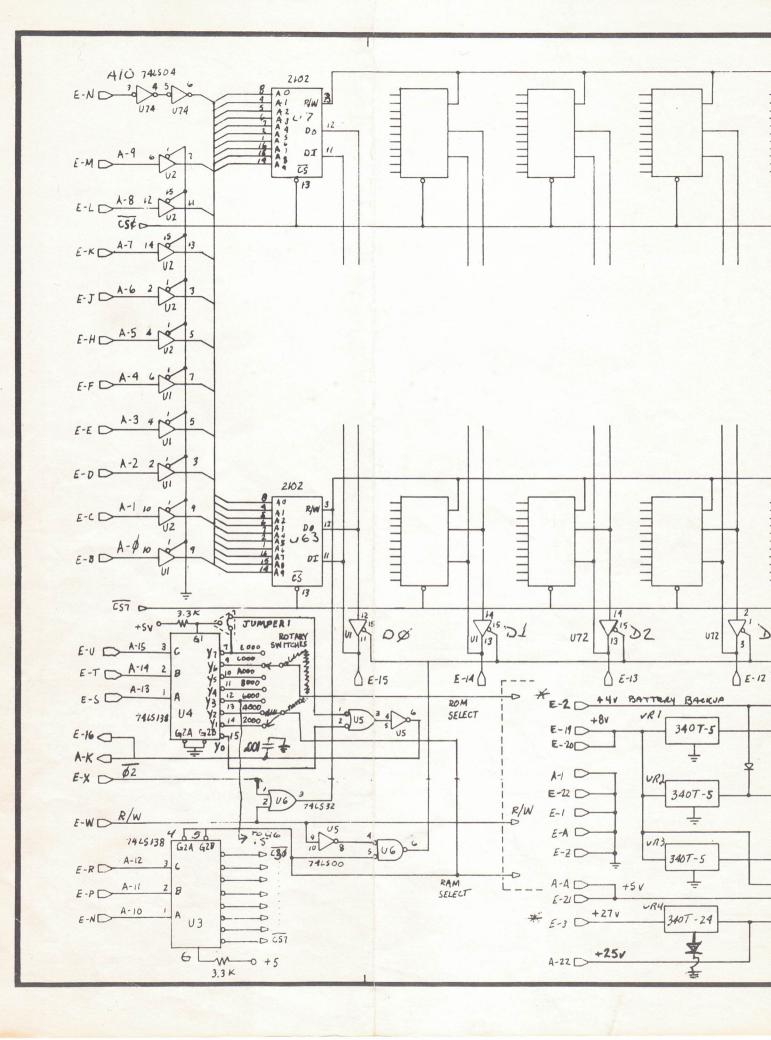

## VIA Address Selection

There are several ways to address the MEMORY PLUS VIA chip. There is circuitry on the board which will normally address the VIA starting at 6200. This is accomplished by combining the 6000 signal generated by the 74LS138 at U4, pin 12, with address lines A8 and A9 in the 74LS32 at U6. If this address is in conflict with something in your system, it may be changed in several ways. The easiest change is to use any other available (unused) decode signal from the 74LS138 at U4. Simply unsolder the existing wire from pin 12 and attach it to the new pin. In this way you can have the VIA addressed as 2200, 4200, 6200 (which is the way the MEMORY PLUS board is shipped), 8200, A200, or C200. If these other addresses do not solve your problem, then you can provide from an external source a signal at pin L of the Application Connector in place of the signal from U4 discussed above. The U4 wire must be disconnected. The VIA address will be the value of the external signal to pin L, plus 0200. example, using the K5 signal (1400) from the KIM-1 or SYM-1 will cause the VIA addresses to start at 1600 (1400 + 0200 = 1600). IMPORTANT NOTE: If you do change the VIA address, then locations 0006 and 0007 in the EPROM Programming Program must be changed before using it.

# VERSATILE INTERFACE ADAPTER

The 6522 Versatile Interface Adapter is one of the important pluses of MEMORY PLUS. This sophisticated chip has the following basic features:

I/O: Two 8-bit parallel I/O ports with additional handshaking control lines. This more than doubles the basic KIM-1 I/O capabilities.

TIMERS: Two powerful interval timers which have a number of operating modes permitting them to be used as counters, "free-running" timers, "one-shot" timers, and more.

SHIFT REGISTER: Perform serial I/O under control of a timer, the system clock or an external signal. Serial-to-parallel and parallel-to-serial conversions take place within the 6522 without involving the MICRO on a bit-by-bit basis.

INTERRUPTS: The many different devices on the 6522 can cause interrupts to signal the completion of activity. These interrupts can be individually enabled, disabled and tested.

The 6255 chip has two functions on MEMORY PLUS. The first is to provide all of the 6522 capabilities to the user as an extension of the MICRO. The second is to control the EPROM Programmer. The 6522 is the heart of the EPROM Programmer. When the system is being used to program EPROMs, then the 6522, as well as several I/O lines from the basic MICRO, is dedicated to this task. See the section on "EPROM Programming" for details.

The addressing of the 6522 is determined by a +5 signal generated by the MEMORY PLUS board and the AB8 and AB9 address signals. The sixteen internal registers of the 6522 normally have the following addresses and functions:

| 6200 | ORB Outp  | ut Register B/Input Register B                       |

|------|-----------|------------------------------------------------------|

| 6201 | ORA Outp  | ut Register A/Input Register A With Handshake        |

| 6202 | DDRB Data | Direction Register B                                 |

| 6203 | DDRA Data | Direction Register A                                 |

| 6204 | T1C-L     | Timer/Counter 1 Low                                  |

| 6205 | T1C-H     | Timer/Counter 1 High                                 |

| 6206 | T1L-L     | Timer/Counter 1 Low                                  |

| 6207 | T1L-H     | Timer/Counter 1 High                                 |

| 6208 | T2C-L     | Timer/Counter 2 Low                                  |

| 6209 | T2C-H     | Timer/Counter 2 High                                 |

| 620A | SR        | Shift Register                                       |

| 620B | ACR       | Auxiliary Control Register                           |

| 620C | PCR       | Peripheral Control Register                          |

| 620D | IFR       | Interrupt Flag Register                              |

| 620E | IER       | Interrupt Enable Register                            |

| 620F | ORA2      | Output Register A/Input Register A Without Handshake |

|      |           |                                                      |

# EPROM Programming

The usefulness of the EPROMs on the MEMORY PLUS board is enhanced by the inclusion of on board EPROM programming facilities. The INTEL 2716 EPROM is electrically programmable and ultraviolet light erasable. The user can buy or build an ultraviolet light eraser. MEMORY PLUS provides the parts required for the programming of the EPROMs. These parts consist of the following items:

- EPROM Programming Socket: Socket 79 is a 24 pin socket located toward the lower right hand corner of the board. The EPROM to be programmed is placed in this socket.

- +25 Volt Regulator: +25 volts is required for programming the 2716.

This may be provided directly by the user at pin A-22 of the MEMORY PLUS application connector. Since this voltage is so critical, and since an over voltage can destroy an EPROM, an on board regulator circuit is provided. This will provide about 24.7 volts when supplied with +27 to +30 volts at pin E-3 of the MEMORY PLUS expansion connector. \*\*SEE NOTE OF PAGE 18.

- Control Lines: The EPROM requires eleven (11) address lines, eight (8) data lines, and two (2) control lines. All but three of these lines are provided by the MEMORY PLUS VIA 6522. The remaining three lines come from the MICRO port B: PBO, PB1, and PB2.

- Timing: EPROM programming requires a 50 millisecond pulse be applied to the EPROM. The VIA 6522 includes a timer which is used for timing this interval.

- EPROM Programming Program: The control of the programming is handled by a program run on the MICRO. This program is provided in the form of a source listing in this manual and as a cassette tape included in the MEMORY PLUS package.

The 2716 EPROM may be programmed one location (byte) at a time, or the entire EPROM may be programmed. The steps required to program the EPROM are:

- 1. With the power off, insert the EPROM to be programmed into the Programming Socket.

- 2. Turn on the power and load the data to be copied into the EPROM into any portion of memory. This may be RAM memory loaded from cassette (or by hand) or may be another EPROM which is going to be copied.

- 3. Load the EPROM Programming Program from cassette (or by hand) into memory (locations 0000 to 00D8)

- 4. Make sure the following application connector connections are in place: MICRO A-9 TO MP A-19; MICRO A-10 TO MP A-20; MICRO A-11 TO MP A-21

5. Set up the following parameters for the EPROM Programming Program:

0000 and 0001 Starting address of memory to be copied from.

0002 and 0003 First address in EPROM to be copied to.

0004 and 0005 Last address +1 of memory to be copied from.

For example, to copy from RAM locations 2000 through 217A into the EPROM starting at location 0300, the following values would be set:

0000 00 Low byte of Starting address 2000

0001 20 High byte of Starting address 2000

0002 00 Low byte of First address in EPROM 0300

0003 03 High byte of First address in EPROM 0300

0004 7B Low byte of Last address +1 217A = 7B

0005 21 High byte of Last address +1 217A

- 6. Turn on +25 volt supply connected to MP A-22 or unregulated +27 to +30 volt supply connected to MP E-3. See Note of Phone 18.

- 7. After double checking that all prior steps have been done correctly, start the program at 0011.

- 8. It will take about 50 milliseconds per location for programming. This means about 100 seconds to program an entire 2K EPROM. When the program is done it will return to the MICRO Monitor with an address which will indicate successful completion of the requested programming. The address value is given in the table in 10. below.

- 9. Turn off the +25 volt (or +27 to +30 volt) supply and the rest of the power to the system. Then remove the EPROM from the programming socket. The EPROM may now be placed in its operational socket and used.

- 10. The EPROM Programming Program performs several tests and may exit to the Monitor to indicate an error or successful completion. The address which will be displayed depends on which Monitor/MICRO you are using.

AIM 00B8 Program ran successfully to completion.

SYM OOBA

AIM 009E A Verify error. The correct data has not been programmed KIM 009F into the EPROM. This may be caused by: SYM 00A0

An EPROM which was not "clean" (all 1's) to start.

A defective EPROM.

One or more address lines from the MICRO not properly hooked up or not properly functioning.

AIM 00A9 A Starting address error. The memory address pointer has KIM 00AA tried to go beyond location FFFF. This may be caused by: SYM 00AB

Providing an incorrect Starting address in locations 0000 and 0001.

Providing an incorrect Last address in locations 0004 and 0005.

AIM 00C3 An EPROM address error. The EPROM address pointer has tried to go beyond location FFFF. This may be caused by:

SYM 00C5

Providing an incorrect First address in locations 0002 and 0003.

Providing an incorrect Last address in locations 0004 and 0005.

The following connections must be made between the MICRO and the MEMORY PLUS board before any EPROM Programming can take place:

| MTCRO | A-9 to MP A-19  | Port                       | В | Bit | 0 | (PBO) | Address | Bit | 8  | for | EPROM . |

|-------|-----------------|----------------------------|---|-----|---|-------|---------|-----|----|-----|---------|

|       | A-10 to MP A-20 | The Village Control of the |   |     |   |       | Address |     |    |     |         |

|       | A-11 to MP A-21 | Port                       | B | Bit | 2 | (PB2) | Address | Bit | 10 | for | EPROM   |

If the MEMORY PLUS board is mounted in its normal position, directly below the MICRO, it may be difficult or impossible to get access to the EPROM socket for programming. There are two ways around this problem.

- 1. Use a 24 pin header to bring wires directly from the EPROM Programming Socket out to a more accessible location.

- 2. Attach wires for an additional EPROM Programming Socket directly to the MP application connector. All of the lines necessary for attaching an external EPROM Programming Socket are available:

| EPROM |               | plication<br>nnector | Function                                 |

|-------|---------------|----------------------|------------------------------------------|

| 1     |               | A-15                 | Address bit 7 from VIA PB7               |

| 2     |               | A-B                  | Address bit 6 from VIA PB6               |

| 3     |               | A-16                 | Address bit 5 from VIA PB5               |

| 3     |               | A-13                 | Address bit 4 from VIA PB4               |

|       |               |                      | Address bit 3 from VIA PB3               |

| 5     |               | A-12                 | Address bit 2 from VIA PB2               |

| 6     |               | A-11                 | Address bit 1 from VIA PB1               |

| 7     |               | A-10                 | Address bit 0 from VIA PB0               |

| 8     |               | A-9                  |                                          |

| 9     |               | A-14                 | Data bit 0 from VIA PAO                  |

| 10    |               | A-2                  | Data bit 1 from VIA PA1                  |

| 11    |               | A-3                  | Data bit 2 from VIA PA2                  |

| 12    |               | A-1                  | Ground                                   |

| 13    |               | A-4                  | Data bit 3 from VIA PA3                  |

| 14    | 100 March 201 | A-5                  | Data bit 4 from VIA PA4                  |

| 15    |               | A-6                  | Data bit 5 from VIA PA5                  |

| . 16  |               | A-7                  | Data bit 6 from VIA PA6                  |

| 17    |               | A-8                  | Data bit 7 from VIA PA7                  |

| 18    |               | A-18                 | Program Pulse Inverted from VIA CB2      |

| 19    | (MICRO A-11)  | A-21                 | Address bit 10 from MICRO PB2            |

| 20    |               | A-F                  | Chip Select from VIA CA2                 |

| 21    |               | A-22                 | +25V direct or from +27 to +30 regulator |

| 22    | (MICRO A-10)  | A-20                 | Address bit 9 from MICRO PB1             |

| 23    | (MICRO A-9)   |                      | Address bit 8 from MICRO PBO             |

| 24    | (MICRO A-A)   | A-A                  | +5V regulated                            |

|       |               |                      |                                          |

The addressing for the EPROM Socket only consists of eleven (11) bits. This means that addressing for programming purposes runs from 0000 to 07FF, regardless of the actual address that the EPROM will eventually reside at. The high order five (5) bits of EPROM address are totally defined by which socket the EPROM is placed in and where the set of EPROMs are switched to: 2000, 4000,..., E000.

PROM ORG \$0000

ACCESS \* \$8B86 SYM-1 ACCESS ENTRY

# VIA REGISTER OFFSETS

|                                                                                                                                                                                    | ORB ORA DDRB DDRA TTWOL TTWOH PCR IFR IER                         | * * * * * * * * * * * * * * * * * * *                        | \$0001<br>\$0002<br>\$0003<br>\$0008<br>\$0009<br>\$0000                                                             | OUTPUT REGISTER B OUTPUT REGISTER A DATA DIRECTION REGISTER B DATA DIRECTION REGISTER A TIMER TWO LOW TIMER TWO HIGH PERIPHERAL CONTROL REGISTER INTERRUPT FLAG REGISTER INTERRUPT ENABLE REGISTER                                                                          |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| G000 C0 0001 00 0002 00 0003 C0 0004 00 0005 00 0006 00 0007 62 0008 4C 00C9 00 000A C0 000B C0 000C OC 00CD OC 00CD OC                                                            | SAL SAH PRMLOW PRMHGH EAL EAH VIA  JMPMON MONTOR  INTVEC PBDD PBD |                                                              | \$00<br>\$00<br>\$00<br>\$00<br>\$00<br>\$00<br>\$00<br>\$62<br>\$4C<br>\$00<br>\$00<br>\$00<br>\$00<br>\$00<br>\$00 | STARTING ADDRESS LOW STARTING ADDRESS HIGH EPROM LOW ADDRESS EPROM HIGH ADDRESS END ADDRESS LOW END ADDRESS HIGH POINTER TO VIA NORMALLY AT 6200 JUMP TO MONITOR POINTER TO SYSTEM MONITOR FOR RETURN FROM PROGRAMMER POINTER TO INTERRUPT VECTOR  PORT B DATA  PORT B DATA |  |

| 0011 A9 00<br>0013 48<br>0014 28<br>0015 A2 E0<br>0017 AD FD FF<br>001A C9 8B<br>001C F0 0A<br>001E A2 D0<br>0020 C9 E0<br>0022 F0 07<br>0024 A2 D8<br>0026 D0 03<br>0028 20 86 8B | KIM                                                               | LDA<br>CMPIM<br>BEQ<br>LDXIM<br>CMPIM<br>BEQ<br>LDXIM<br>BNE | STABLE<br>\$FFFD<br>\$8B<br>SYM<br>ATABLE<br>\$EO<br>MOVE<br>KTABLE<br>MOVE                                          |                                                                                                                                                                                                                                                                             |  |

| 002B 86 30<br>002D A2 07<br>002F B5 00<br>0031 95 09<br>0033 CA<br>0034 10 F9                                                                                                      | MOVE                                                              | STXZ<br>LDXIM<br>LDAX<br>STAX<br>DEX                         | \$07<br>\$00<br>MONTOR                                                                                               | +O1 SETUP POINTER                                                                                                                                                                                                                                                           |  |

| 0036<br>0038<br>0039                                 | 48                               | 00                         | ENTER  | LDAIM<br>PHA<br>PLP                       | \$00                                         | CLEAR ALL STATUS FLAGS                                                      |

|------------------------------------------------------|----------------------------------|----------------------------|--------|-------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------|

| 003A<br>003C<br>003E<br>0040<br>0042                 | AO<br>A9<br>91<br>A9             | C5<br>OB                   |        | LDYIM<br>LDAIM<br>STAIY                   |                                              | GET INTERRUPT POINTER SETUP IN TABLE                                        |

| 0042<br>0043<br>0045<br>0047<br>0049                 | 91<br>A9<br>A0                   | EC<br>OC                   |        | STAIY<br>LDAIM<br>LDYIM                   | PCR                                          | SETUP VIA VALUES                                                            |

| CO4B<br>004D<br>CO4F                                 | AO<br>A9<br>91                   | 0E<br>7F<br>06             |        | LDAIM<br>STAIY                            | IER<br>\$7F<br>VIA                           | DISABLE ALL INTERRUPTS                                                      |

| 0051<br>0053<br>0055<br>0057                         | A 9<br>91<br>A D                 | FF<br>C6<br>OE             |        | LDYIM<br>LDAIM<br>STAIY<br>LDYIM          | \$FF<br>VIA<br>IER                           | CLEAR INTERRUPT PENDING                                                     |

| 0059<br>005B                                         |                                  |                            |        | LDAIM                                     |                                              | ENABLE TIMER TWO                                                            |

| 005D<br>005F<br>0061<br>0063<br>0065<br>0067         | A9<br>A0<br>91<br>AC<br>91       | FF<br>02<br>06<br>03<br>06 | NEXT   | LDAIM<br>LDYIM<br>STAIY<br>LDYIM<br>STAIY | DDRB<br>VIA<br>DDRA<br>VIA                   | INIT X RECISTER SET DATA DIRECTION                                          |

| 0069<br>006B<br>006D<br>006F<br>0071<br>0073<br>0075 | A5<br>81<br>A5<br>81<br>A1<br>A0 | 06<br>03<br>0F<br>00<br>01 |        | LDYIM                                     | PRMLOW<br>VIA<br>PRMHGH<br>PBD<br>SAL<br>CRA | CUTPUT NEXT ADDRESS LOW 8 BITS  BITS 8, 9, 10 GET DATA BYTE  CUTPUT VIA CRA |

| 0077                                                 |                                  | 50                         | TIMER  |                                           | VIA<br>\$50                                  | SETUP 50 MILLISECOND TIMER                                                  |

| 007B<br>007D<br>007F<br>0081                         | A D<br>91<br>A 9<br>A D          | 08<br>06<br>03<br>09       | TITLE  | LDYIM<br>STAIY<br>LDAIM<br>LDYIM          | TIWOL<br>VIA<br>\$C3<br>TIWOH                | OUTPUT TO TIMER TWO LOW<br>HIGH BYTE OF TIMER                               |

| 0083<br>0085<br>0087<br>0089                         | A9<br>AD                         | CE<br>OC                   |        |                                           |                                              | OUTPUT TO TIMER TWO HIGH<br>PROGRAM HIGH, PROGRAM MODE                      |

| 008B                                                 |                                  |                            | TIAW   | CPYIM<br>BEQ                              | PCR<br>WAIT                                  | TEST FOR INTERRUPT SERVICED ELSE, WAIT FOR IT                               |

| 008F<br>0091<br>0093<br>0095                         | A0<br>91<br>A0                   | 03<br>06<br>01             | VERIFY | LDYIM<br>STAIY                            | DDRA                                         | VERIFY PROGRAMMING SET ORA FOR INPUT SETUP POINTER                          |

| 0097                                                 | Bl                               | 06                         |        | LDAIY                                     | VIA                                          |                                                                             |

| 0099 C1 00<br>0098 F0 03<br>009D 20 08 00                                                         |        | BEQ                                           | DKAY                                                         | COMPARE ORIGINAL DATA GOOD IF MATCH EXIT ON ERROR                                            |

|---------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| ODAO E6 OO<br>OOA2 DO O7<br>OOA4 E6 O1<br>OOA6 DO O3<br>COA8 20 O8 OO                             | OKAY   | BNE<br>INC                                    | SAH<br>TEST                                                  | BUMP DATA POINTER BRANCH IF NOT ZERO BUMP HIGH DATA POINTER BRANCH IF NOT ZERO EXIT ON ERROR |

| 00AB A5 05<br>00AF C5 01<br>00AF D0 09<br>00B1 A5 04<br>00B3 C5 00<br>00B5 D0 03<br>00B7 20 08 00 | TEST   | LDA<br>CMP<br>BNE<br>LDA<br>CMP<br>BNE<br>JSR | SAH<br>MORE<br>EAL<br>SAL<br>MORE                            | TEST ALL DONE<br>BY COMPARING POINTERS                                                       |

| 00BA E 6 02<br>00BC DO 9F<br>00BE E 6 03<br>00CO DO 9B<br>00C2 20 08 00                           | MORE   | INC<br>BNE<br>INC<br>BNE<br>JSR               | NE XT<br>PRMHGH<br>NE XT                                     | BUMP PROM POINTERS READY IF NOT ZERO BUMP HIGH POINTER OKAY IF NOT ZERO EXIT ON ERROR        |

| COC5 A9 EC<br>OOC7 91 O6<br>COC9 AO OD<br>OOCB B1 O6<br>OOCD 91 O6<br>OOCF 40                     | INTRPT | STAIY<br>LDYIM<br>LDAIY                       | \$EC<br>VIA<br>IFR<br>VIA<br>VIA                             | SETUP TO CLEAR INTERRUPT<br>READ AND WRITE TO CLEAR                                          |

| 00D0 6D<br>00D1 E1<br>00D2 0C<br>00D3 A4<br>00D4 02<br>00D5 A0<br>00D6 00<br>00D7 AC              | ATABLE | = = = = = = = = = = = = = = = = = = = =       | \$6D<br>\$E1<br>\$00<br>\$A4<br>\$02<br>\$A0<br>\$A0<br>\$A0 | TO DISPLAY PC COUNTER                                                                        |

| 00D8 05<br>00D9 1C<br>00DA FE<br>00DB 17<br>00DC 03<br>00DD 17<br>00DE 02<br>00DF 17              | KTABLE |                                               | \$05<br>\$1C<br>\$FE<br>\$17<br>\$03<br>\$17<br>\$02<br>\$17 | KIM MONITOR ENTRY  IRQ INTERRUPT POINTER  PBDD  PBD                                          |

| 00E0 35<br>00E1 80<br>00E2 7E<br>00E3 A6<br>00E4 02<br>00E5 A0<br>00E6 00                         | STABLE | =======================================       | \$35<br>\$80<br>\$7E<br>\$A6<br>\$02<br>\$A0                 | SYM ENTRY POINT IRQ INTERRUPT POINTER PBDD PBD                                               |

| COE7 AO                                                                                           |        | Ξ                                             | \$A0                                                         | 16                                                                                           |

# MEMORY PLUS Testing and Field Repair

Your MEMORY PLUS board has been burned in and tested before shipment. If, after following the steps outlined in the "Setting Up MEMORY PLUS" section, the board does not seem to work properly, or if it ever seems to stop functioning correctly, then the following steps should be taken.

1. Check that the board is receiving adequate power.

Place the ground lead of a voltmeter or 'scope on any convenient ground on the board (the left lead of the large capacitor at the upper left hand corner of the board is handy) or on the connector (A-1, E-1, E-22, E-A, or E-Z).

Measure the +5 volts at each of the four jumpers on the Header located near the voltage regulators. If you are providing unregulated +8 to +10 volts, then the top jumper should have this value. If you are using regulated +5 volts, then the top jumper should show +5V. The bottom three jumpers should show +5V in any case. If not, check your supply. If one of the three shows a voltage other than +5, it indicates a problem with the associated voltage regulator which might require replacement. The bottom jumper comes from Q6, the next jumper from Q5, and the next to top jumper from Q4. (See diagram on page 25).

Measure the +25 volts at pin A-22 of the MEMORY PLUS application connector. If you are providing unregulated +27 to +30 volts, the output of the +25 volt regulator circuit should show about +24.7V. If you are providing regulated +25 volts at this pin, it will show the output of your power supply. If the value for the unregulated situation is not +24.7, then check your unregulated voltage at pin E-2 of the MEMORY PLUS expansion connector. It must be +27 to +30V.

- 2. Check that all IC chips are firmly in their sockets. It is possible for chips to come loose during handling and shipping. Push each chip firmly into its socket.

- 3. Check that the Header is in the proper position for the method of providing +5 volts. If you are providing +5 at pins E-21 and E-Y, then the Header should have its notched corner at pin 9 and the jumper wires should go from pins 2-15, 4-13, 6-11, and 8-9. If you are providing unregulated +8 to +10 volts at pins E-19 and E-20, then the Header should have its notched corner at pin 1 and the jumper wires should go from pins 1-16, 3-14, 5-12, and 7-10.

- 4. Check all of the connections between the MICRO, MEMORY PLUS, and the power supplies.

- 5. Follow the instructions in the "RAM Memory Test" section if the RAM Memory appears to be having problems.

- 6. Check the MICRO or try MEMORY PLUS with a different MICRO. For EPROM Programming it is absolutely essential that bits 0, 1, and 2 of the MICRO Port B are functioning properly (PBO, PBI, and PB2). A quick test of Port B may be made by putting FF in location PBDD and then trying to write 07 in location PBD. If this does not work, then you have a problem and should not attempt to program any EPROMs until you have the MICRO serviced.

Remember that you are exercising your MICRO in ways you may have never tried before. This will, in some cases, uncover faults that have existed undetected in a MICRO. For example, my own "reliable" Kim-1 which I had been using extensively for well over a year, turned out to have a defective Port B. Bits O and 1 which I had been using for cassette control worked fine, but bit 2 did not. I zapped a few EPROMs, not fatally thank goodness, before discovering this. Another KIM-1 I used had flakey memory in Page Zero such that the RAM Memory Test would not work. So, it really can happen.

7. Check all MEMORY PLUS switches and jumpers. In addition to the Header which was discussed in 1. and 3. above, there are two switches and a jumper to be concerned with:

The RAM Address Select Switch (see page 8) must be set to "2K" for the Memory Test to work as documented. Actually, the memory test will work with any addresses, as long as the correct parameters are set in page zero location 0000 - start page number = first page to test and location 0001 - end page number = last page to test. The RAM switch must be selecting the bank of memory you are attempting to test, and it may not be selecting the same chunk of memory as the ROM select switch.

The ROM Address Select Switch (see page 8) must not be set to the same starting address as the RAM switch. If the ROM switch is set to "EK", then there will be conflict with the MICRO Monitor interrupt vectors unless the jumper changes discussed on page 9 have been made, since the board comes with the jumper set so that interrupts will be decoded by the MICRO Monitor locations 1FFA through 1FFF. If you put ROM in E000 to FFFF, then this jumper must be changed. Otherwise any address in this range will be decoded twice: as E000 to FFFF and 0000 to 1FFF.

8. Check that all EPROMs are inserted in the proper direction. Pin 1 in the EPROM Programming Socket is in the upper left corner. Pin 1 in the EPROM normal sockets is in the upper right corner.

MEMORY PLUS was designed for easy field repair. It is, of course, hoped that no repair will ever be required on your unit. If some repair is required, then it is hoped that it can be done by the user or some local source. The unit should only have to be sent back for factory servicing in rare circumstances. This means that your MEMORY PLUS board should never be down very long.

#### WARNING:

Do NOT connect +5V Battery to E-2

or +27 Unreg. to E-3 if these lines

are connected to your microcomputer

via a cable of MOTHER board as these

voltages could damage your computer.

If these two voltages are to be used

(for battery backup and EPROM programming)

make sure they are isolated from the

rest of your system.

The dot in one corner of each IC chip and Header indicates the proper location of pin 1. The Header has two corners marked, one labelled +5 and one labelled +8. These indicate the proper orientation of the Header when the power supply is providing a regulated +5 volts or an unregulated +8 to +10 volts.

ROM and RAM show the location of the switches used to select the base address for the ROM and RAM memories.

J1 marks the location of the jumper which must be changed if ROM is placed to start at E000. The line shown is the etched jumper which causes interrupt addresses (FFFA to FFFF) to select the KIM-1 Monitor interrupt vectors (1FFA to 1FFF). This jumper must be removed and replaced by a jumper from the dot near the J to the dot near the 1 if interrupts are to be decoded by the high addresses.

# RAM Memory Test

You should test the MEMORY PLUS RAM when you initially set up your system. You may also want to test it from time-to-time to make sure it is all still working properly. And, of course, you will want to test it whenever you have any reason to suspect that it may not be working right. The following memory test is based on the work cited under "NOTES" on page 24.

"Testing RAM isn't just a question of storing a value and then checking it. It's important to test for interference between locations. Such tests often involve writing to one location and then checking all other locations to see they haven't been disturbed; this can be time consuming.

This program checks memory thoroughly and runs exceptionally fast. It is adapted from an algorithm by Knaizuk and Hartmann published in "IEEE Transactions on Computers", April 1977.

The program first puts value FF in every location under test. Then it puts 00 in every third location, after which it tests all locations for correctness. The test is repeated twice more with the positions of the 00's changed each time. Finally, the whole thing is repeated with the FF and 00 values interchanged.

To Run: Set the addresses of the first and last memory pages you wish to test into locations 0000 and 0001 respectively. Start the program at address 0002; it will halt with a memory address on the display. If no faults were found, the address will be one location past the last address tested. If a fault is found, its address will be displayed."

The MEMORY PLUS version of the memory test is set up to test from page 20 (2000 hex) through page 3F (3FFF hex). After loading the program from the cassette tape (or by hand), set address 0002 and press GO. If the memory checks out completely, then after a few seconds the display will show the address 4000 in the address portion of the display. If an error is detected, then the address containing the error will be displayed. Since the program will halt at the first detected error, there is no way to test for additional errors within a page beyond the first error. You can test other pages by changing the starting and ending page addresses in locations 0000 and 0001. The program may be re-run any number of times by restarting it at location 0002.

Once a bad location has been detected, you can examine the location via the MICRO Monitor and perhaps determine the problem. For example, if the location has a data value of 7F, it would indicate that the most significant bit was not working. Refering to the Memory Organization drawing you could determine which 2102 chip was responsible for this bit. Since the RAM chips are all socketted, it is a simple matter to remove the suspect chip and replace it with another chip. Even if you do not have any spare 2102 chips handy, you can swap the suspect chip with another chip and see if the problem moves with the chip or stays in the same location. <a href="IMPORTANT NOTE:">IMPORTANT NOTE:</a> Turn the power off when removing any chips, otherwise you may destroy the memory chips. If the problem moves with the chip, then the solution is to get a replacement chip. If the problem does not move with the chip, then you must look elsewhere for the solution.

The next test would be to swap the 74LS367 chips and see if the problem shifted. Then the 74LS138 chips could be swapped. Finally you could replace the 74LS00, 74LS32, or 74LS04 chips. Note that the replacements do not have to be "LS" type. One of the above chip replacements should solve 99% of the problems which occur in the field.

```

MEMORY TEST 9 FEBRUARY 1979

MEMORY ORG $0000

$8B86 SYM-1 ACCESS ENTRY

ACCESS *

OUTBYT * $82FA SYM-1 OUTPUT BYTE

SCANDS * $8906 SYM-1 SCAN DISPLAY

$1C4F KIM-1 ENTRY POINT

$00FA KIM DISPLAY POINTERS

GOKIM *

LPOINT *

HPOINT * $00FB

$EF7B AIM 65 OUTPUT ASCII

ASCOUT *

BEGIN =

STARTING TEST PAGE

0000 20

$20

$3F

0001 3F

END =

ENDING TEST PAGE

0002 A9 00 START LDAIM $00 ZERO POINTERS

0004 A8 TAY FOR LOW ORDER ADDRESSES

0005 48 PHA SET ALL STATUS BITS TO ZERO

0006 28 PLP

0007 85 D1

STAZ POINTL

BIGLP STAZ FLAG = 00 FIRST PASS, = FF SECOND PASS

0009 85 D3

000B A2 02

LDXIM $02

STXZ PASS SET 3 TESTS EACH PASS

000D 86 D5

NPASS LDAZ BEGIN SET POINTER TO

STAZ POINTH START OF TEST AREA

LDXZ END

000F A5 00

0011 85 D2

0013 A6 01

LDAZ FLAG

0015 A5 D3

0017 49 FF

EORIM $FF REVERSE FLAG

STAZ FLIP = FF FIRST PASS, = 00 SECOND PASS

0019 85 D4

001B 91 D1 CLEAR STAIY POINTL WRITE FLIP VALUE

001D C8 INY TAIL CONTROL

INY

INTO ALL LOCATIONS

BNE CLEAR

OO1E DO FB

INCZ POINTH

0020 E6 D2

0022 E4 D2

CPXZ POINTH

0024 BC F5

BCS CLEAR

FLIP VALUE IN ALL LOCATIONS. NOW CHANGE 1 IN 3

0026 A6 D5 LDXZ PASS

CO28 A5 CO LDAZ BEGIN SET POINTER

CO2A 85 D2 STAZ POINTH BACK TO START

002C A5 D3

LDAZ FLAG CHANGE VALUE

FILL

CO2E CA

TOP

DEX

BPL SKIP SKIP 2 OUT OF 3

002F 10 04

BPL SKIP SKIP 2 OUT OF 3

LDXIM $02 RESTORE 3 COUNTER

STAIY POINTL CHANGE 1 OUT OF 3

0031 A2 02

STAIY POINTL CHANGE 1 OUT OF 3

0033 91 D1

SKIP

0035 CE

INY

0036 DO F6

TOP

INCZ POINTH NEW PAGE

0038 E6 D2

```

| 003A<br>003C<br>003E                                         | C5                               | D2                               |    |        | CMPZ                                           | POINTH                                             | HAVE WE PASSED<br>END OF TEST AREA?<br>NO. KEEP GOING                                 |

|--------------------------------------------------------------|----------------------------------|----------------------------------|----|--------|------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------|

|                                                              |                                  |                                  |    | MEMORY | SET UF                                         | . NOW                                              | TEST IT                                                                               |

| 0040<br>0042<br>0044                                         | 85                               | D2                               |    |        | STAZ                                           | POINTH                                             | SET POINTER BACK TO START SET UP 3 COUNTER                                            |

| 0046<br>0048<br>0049<br>004B<br>004D                         | CA<br>10<br>A2                   | 04                               |    |        | DE X<br>BPL<br>LDXIM                           | SLIP<br>\$02                                       | TEST FOR FLIP VALUE 2 OUT OF 3 TIMES OR 1 OUT OF 3 TIMES TEST FOR FLAG VALUE          |

| 004F<br>0051<br>0053<br>0054<br>0056<br>0058<br>005A<br>005C | DO<br>C8<br>DO<br>E6<br>A5<br>C5 | 15<br>F 0<br>D 2<br>01<br>D 2    |    |        | BNE<br>INY<br>BNE<br>INCZ<br>LDAZ              | OUT POP POINTH                                     | TEST END                                                                              |

|                                                              |                                  |                                  |    | ABOVE  | TEST OF                                        | KAY. CH                                            | HANGE AND REPEAT                                                                      |

| 005E<br>0060<br>0062<br>0064<br>0066                         | 10<br>A5<br>49                   | AD<br>D3<br>FF                   |    |        | BPL<br>LDAZ                                    | NPASS<br>FLAG<br>\$FF                              | CHANGE 1 IN 3 POSITION AND DO NEXT PASS INVERT FLAG FOR PASS TWO AND REPEAT BIG LOOP  |

| 0068<br>006A<br>006D<br>006F<br>0071<br>0073                 | AD<br>C9<br>FO<br>C9             | FD<br>8B<br>46<br>E0             | FF |        | LDA<br>CMPIM<br>BEQ                            | POINTL<br>\$FFFD<br>\$8B<br>SYM<br>\$EO<br>AIM     | PUT LOW ORDER ADDRESS FOR DISPLAY TEST HIGH BYTE OF INTERRUPT VECTOR = SYM-1 = AIM 65 |

| 0075<br>0077<br>0079<br>007B<br>007D                         | 85<br>A5<br>85                   | FA<br>D2<br>FB                   | 1C | KIM    | LDAZ<br>STAZ<br>LDAZ<br>STAZ<br>JMP            | LPOINT<br>POINTH<br>HPOINT                         | MOVE POINTERS FOR KIM RETURN TO KIM MONITOR                                           |

| 0080<br>0082<br>0084<br>0086<br>0088<br>008A<br>008C         | 85<br>85<br>85<br>A2<br>A1<br>85 | D6<br>D1<br>D7<br>00<br>D1<br>D8 | ë  | AIM    | STAZ<br>LDAZ<br>STAZ<br>LDXIM<br>LDAIX<br>STAZ | AHIGH<br>POINTL<br>ALOW<br>\$00<br>POINTL<br>ADATA | MOVE DATA FOR AIM DISPLAY  GET DATA AT ADDRESS  START AT POSITION 19.                 |

| 0090                                                         | 8A                               |                                  |    | ALOOP  | TXA                                            |                                                    | SAVE X VALUE                                                                          |

|                                                              |                                  |                                  |    |        |                                                |                                                    |                                                                                       |

```

0091 48

PHA

ON STACK

CC92 AC C4

SHIFT 4 POSITIONS PER CHARACTER

LDYIM $04

0094 A5 D8

LDAZ ADATA

GET DATA

0096 29 OF

ANDIM $OF

MASK TO NIBBLE

CO98 C9 CA

CMPIM $0A

TEST DECIMAL

009A 30 03

BMI

AOKAY

DECIMAL

CLC

CO9C 18

A - F. MUST CONVERT TO

009D 69 07

ADCIM $07

ASCII

009F 18

ADKAY

CLC

FINISH CONVERSION

00AC 69 BC

ADCIM $BO

ASCII + AIM FLAG

00A2 20 7B EF

JSR

ASCCUT CUTPUT TO DISPLAY

00A5 46 D6

AMOVE

LSRZ

AHIGH MOVE TO NEXT NIBBLE

00A7 66 D7

RORZ

ALOW

00A9 66 D8

ROR7

ADATA

00AB 88

DEY

ODAC DO F7

BNE

AMOVE

RESTORE X

00AE 68

PLA

ODAF AA

TAX

OOBO CA

DEX

DONE?

COB1 EO CE

CPXIM $0E

COB3 BC DB

BCS

ALCCP

NO

OCB5 90 C9

BCC

AIM

YES. REPEAT

COB7 20 86 8B SYM

JSR

ACCESS ENABLE SYM MOEMORY

OOBA A5 D2

LDAZ

PCINTH

OUTBYT OUTPUT

OOBC 20 FA 82

JSR

OOBF A5 D1

LDAZ

POINTL

OOC1 20 FA 82

JSR

OUTBYT

00C4 AC CC

LDYIM $00

00C6 B1 D1

LDAIY POINTL GET DATA

OCC8 20 FA 82

JSR

CUTBYT

COCB 20 06 89 DISPLY JSR

SCANDS SCAN DISPLAY

OOCE 4C CB OO

JMP

DISPLY CONTINUE

00D1 00

POINTL =

$00

00D2 00

POINTH =

$00

00D3 00

FLAG

=

$00

COD4 CC

FLIP

=

$00

00D5 00

PASS

=

$00

00D6 00

=

AHIGH

$00

COD7 00

ALOW

=

$00

0008 00

ADATA

$00

```

# MEMORY PLUS Parts List

| ITEM | PART                                | Qty. | DESCRIPTION                                    |

|------|-------------------------------------|------|------------------------------------------------|

| 1.   | U1, U2, U72                         | 3    | IC 74LS367 Hex Bus Driver with 3-state outputs |

| 2.   | U3, U4, U76                         | 3    | IC 74LS138 3-to-8 Line Decoder                 |

| 3.   | U5                                  | 1    | IC 74LS00 Quad 2-Input Positive NAND Gates     |

| 4.   | U6                                  | 1    | IC 74LS32 Quad 2-Input Positive OR Gates       |

| 5.   | U74                                 | 1    | IC 74LS04 Hex Inverter                         |

| 6.   | U7 - U70                            | 64   | Memory Element 2102 450 nanosec, low power     |

| 7.   | SW1, SW2                            | 2    | 1-of-7 Rotary Switch                           |

| 8.   | R1 - R3                             | 3    | Resistor 3.3K, 1/4 watt                        |

| 9.   | C1 - C37                            | 37   | Capacitor .01 MFD, 50WV DC                     |

| 10.  | C38                                 | 1    | Electrolytic Capacitor 22 - 25 MFD, 25V        |

| 11.  | C39                                 | 1    | Capacitor .001 MFD                             |

| 12.  | C40                                 | 1    | Electrolytic Capacitor 3 - 5 MFD, 35V          |

| 13.  | Q1, Q2, Q3                          | 3    | Diodes 1N4001 Rectifier 50V                    |

| 14.  | Q4, Q5, Q6                          | 3    | Voltage Regulator LM340T-5, +5V, 1.0A          |

| 15.  | Q7                                  | 1    | Voltage Regulator LM340T-24, +24V, 1.0A        |

| 16.  | HS1 - HS3                           | 3    | T220 Heat Sink (Large)                         |

| 17.  | HS4                                 | 1    | T220 Heat Sink (Small) (may be omitted)        |

| 18.  | S1 - S4, S7 - S70,<br>S72, S76, S80 | 71   | IC Socket 16 pin                               |

| 19.  | S5, S6, S74                         | 3    | IC Socket 14 pin                               |

| 20.  | S71, S73, S75, S77,                 | 5    | IC Socket 24 pin                               |

|      | S79                                 |      |                                                |

| 21.  | S78                                 | 1    | IC Socket 40 pin                               |

| 22.  | H1                                  | 1    | IC Socket Header 16 pin                        |

| 23.  | U78                                 | 1    | VIA 6522 Versatile Interface Adapter           |

|      | Accessories Package                 |      |                                                |

3 Battery Clip 9V transistor battery type

# NOTES:

- 1. The Memory Test is adapted from "Memory Test" by Jim Butterfield which appears on pages 122 and 123 of THE FIRST BOOK OF KIM, edited by Butterfield, Ockers and Rehnke, published by Hayden Book Company. The book sells for \$9.00 and is a must for any 6502 user.

- 2. The program listings in this manual were produced by the Micro-ADE Assembler on a KIM-1 with a MEMORY PLUS board. The COMPUTERIST version of Micro-ADE includes a cassette tape with two versions of Micro-ADE. One has the program in 2000 to 2FFF and uses 3000 to 3FFF for the Source and Symbol working areas. The other has the program in C000 to CFFF and uses 2000 to 3FFF for the Source and Symbol working areas. This second version is ready to be placed into EPROM and left resident in your MEMORY PLUS board. Micro-ADE costs \$25.00 for the Operators Manual and Cassette Tape. This Manual includes most of the Input/Output Source Listings so that the user can customize the package to his type of terminal. Complete Source Listings are available for an additional \$25.00.

# **SYM and AIM Memory Expansion**

An easy hardware modification addresses extended memory in contiguous 8K blocks with no gaps. This neat enhancement makes Memory Plus a natural for RAMming more data into the SYM and AIM.

Paul Smola Acushnet Corporation P. O. Box E916 New Bedford, MA 02742

In an attempt to implement BASIC on the SYM it became apparent that the 4K of onboard RAM was insufficient for our needs. Although we have several Memory Plus boards around, the RAM on these boards is addressable in 8K byte blocks decoded at 8K boundaries, beginning at location 2000. Unfortunately, this decoding scheme leaves a 4K block of memory unimplemented. That block of memory is from address 1000 through 1FFF.

In order to overcome this shortcoming, it is desirable to decode the Memory Plus board in 8K blocks that are addressable at 4K boundaries; that is, at locations 1000, 3000, 5000, etc. With this scheme several MP boards could be added on to expand the SYM memory in a continuous fashion. There are methods available for making this change, but most of these require changes on the MP board itself. This is undesirable, especially if servicing becomes a problem.

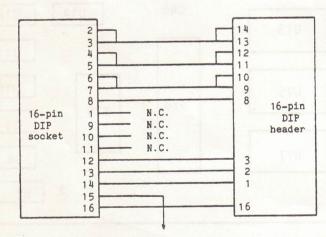

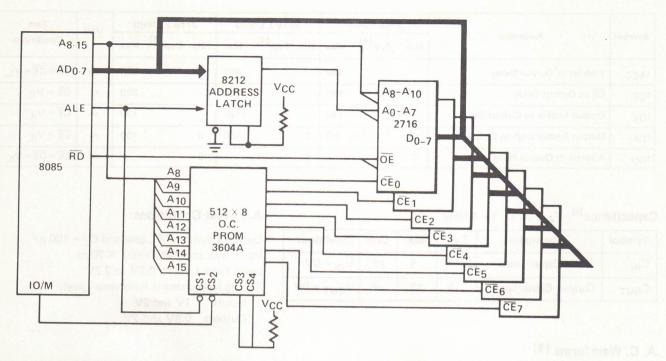

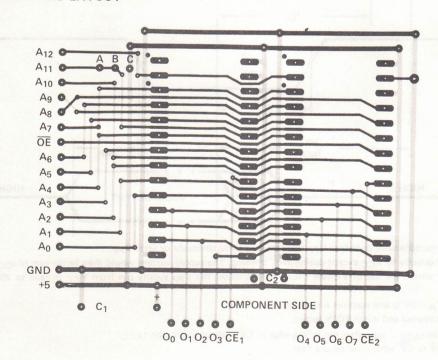

The solution lies in replacing the three high order address line decoding schemes with one that will address memory at 4K boundaries. This can be accomplished by bringing addresses A12, A13, and A14 into the inputs of the 74LS138, as opposed to the present A13, A14, and A15. With this change any position of the rotary switch which selects the RAM decoding address enables the RAM at 4K boundaries, and also only in 4K blocks.

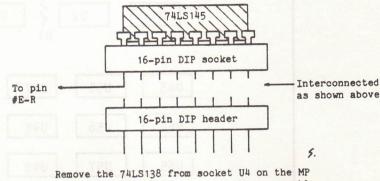

Remove the 74LS138 from socket U4 on the MP board and replace it with the above assembly

### Figure 2

If we were to OR two adjacent outputs together, we would have 4K boundaries with 8K blocks. However, because the outputs of a 74LS138 are totem-pole, ORing them must be done with additional gating and not simply by tying the outputs together, as is done with open-collector outputs.

One method of doing this is by replacing the '138 with a 74LS145 BCD-to-decimal decoder driver. This device has open collector outputs enabling them to be wire OR'ed together. However, the pin out on the '145 is radically different from that on the '138.

The way to get around this is to mount the '145 in a 16 pin dip socket which is in

turn connected to a 16 pin dip header. However, rather than matching the pins number for number, the connection diagram in Figure 1 is followed. This is most easily accomplished by using a three level wire-wrap socket and cutting short all the pins except 8 and 16. These shortened pins are then wired to the correct position on the header by soldering jumpers on. This causes the pin out connections to be changed and thus allows the '145 to operate in the socket which was previously loaded with the '138.

The 16 pin dip header is then loaded into the MP board into socket U4 as shown in Figure 2. The '145 has the advantage of having four address input lines. Thus address lines A12, A13, A14, and A15 are brought into it and fully decoded. Since address line A12 is not brought to socket U4, it must be separately wired. A convenient place to make this connection is on the MP expansion connector pin #E-R.

With these changes, the RAM select rotary switch now selects hex locations 1000-2FFF at the first two positions. At the second two positions RAM is selected at 3000-4FFF. In the third two positions RAM is selected at locations 5000-6FFF. RAM will not be selected with the selector switch in the seventh position.

With the switch in the first or second position, BASIC on the SYM can be implemented with 12K memory; the 4K onboard, plus the 8K from the MP. The addition of another MP board set up the same way with the RAM selection switch in either position 3 or 4 would yield a system with 20K of continuous memory.

Solder to pin #E-R on the Memory Plus Expansion Connector

Figure 1

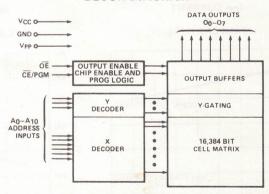

# 2716\* 16K (2K × 8) UV ERASABLE PROM

- Fast Access Time

- 350 ns Max. 2716-1

- 390 ns Max. 2716-2

- 450 ns Max. 2716