# G65SC32

# **Microcircuits**

# CMOS RAM, I/O, Timer

# Features

- CMOS process technology for low power consumption

- Fully compatible with NMOS 6532 devices

- · Bus compatible with 6500 and 6800 microprocessors

- Low power consumption (2 mA at 1 MHz)

- 128 X 8 bit static RAM

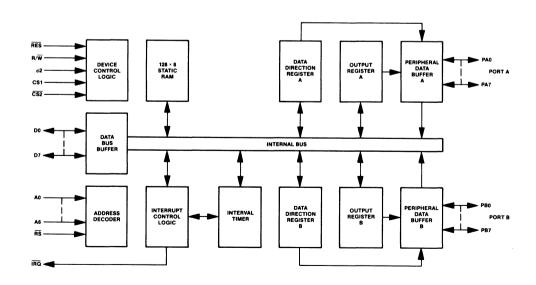

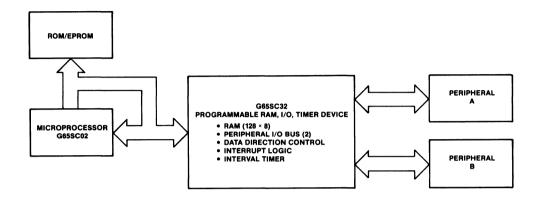

**Block Diagram**

- Two 8-bit bidirectional peripheral data ports

- Two programmable Data Direction Registers

- · Programmable Edge Sense Interrupt function

- · Interrupt Timer with programmable interrupt intervals

- Peripheral I/O Port B allows direct transistor drive

- · High impedance three-state Data Bus

- Available in 40-pin dual-in-line package or 44-pin PLCC

# **General Description**

The G65SC32 is a programmable RAM, I/O, Timer device for use with the G65SCXXX series 8-bit microprocessor family. The G65SC32 includes functions for programmed control of up to two peripheral devices (Port A and Port B). These functions include:

- 128 X 8 bit static RAM for microprocessor scratch pad activity.

- Two program controlled 8-bit bidirectional Data Ports for direct interfacing between the microprocessor and selected peripheral units.

- Two programmable Data Direction Registers (A and B) for data direction control at each peripheral Data Port.

- A programmable Interrupt Timer with interrupt timing capability in intervals ranging from 1 to 262,144 clock periods.

- Edge-detect interrupt circuitry for interrupt generation on active edge transitions.

The G65SC32 offers the many advantages of GTE's leading edge CMOS technology, i.e., increased noise immunity, higher reliability, and greatly reduced power consumption.

# Absolute Maximum Ratings: (Note 1)

| Rating                | Symbol | Value               |  |  |

|-----------------------|--------|---------------------|--|--|

| Supply Voltage        | VDD    | -0.3V to +7.0V      |  |  |

| Input/Output Voltage  | Vin    | -0.3V to VDD + 0.3V |  |  |

| Operating Temperature | TA     | -40°C to +85°C      |  |  |

| Storage Temperature   | Ts     | -55° C to +150° C   |  |  |

This device contains input protection against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of voltages higher than the maximum rating.

#### Notes:

1. Exceeding these rating may cause permanent damage, functional operation under these conditions is not implied.

DC Characteristics: VDD =  $5.0V \pm 5\%$ , VSS = 0V, TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C Industrial,  $0^{\circ}$ C to  $+70^{\circ}$ C Commercial

| Parameter                                                                                                    | Symbol                   | Min. | Max.                     | Unit                 |

|--------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|----------------------|

| Input High Voltage                                                                                           | Viн                      | 2.0  | VDD + 0.3                | V                    |

| Input Low Voltage                                                                                            | VIL                      | -0.3 | 0.8                      | v                    |

| Input Leakage Current (VIN = 0 to VDD),<br>Input Only Pins, A0-A6, ¢2, CS1, CS2, R/W, RES, RS)               | lin                      |      | ±1.0                     | μΑ                   |

| Three-State, Leakage Current (VIN = 0.4 to 2.4V),<br>D0-D7, IRQ                                              | ITSI                     |      | ±10.0                    | μA                   |

| Input High Current (Vi∺ = 2.4V), Peripheral Inputs with Pullups,<br>PA0-PA7, PB0-PB7                         | Ін                       | -200 |                          | μΑ                   |

| Input Low Current (VI∟ = 0.4V), Peripheral Inputs with Pullups,<br>PA0-PA7, PB0-PB7                          | liL .                    |      | 1.6                      | mA                   |

| Output Low Voltage (Io∟ = 3.2 mA),<br>D0-D7, PA0-PA7, PB0-PB7, IRQ                                           | VOL                      |      | 0.4                      | v                    |

| Output High Voltage (IoH = -200 µA),<br>D0-D7, PA0-PA7, PB0-PB7, IRQ                                         | Vон                      | 2.4  |                          | v                    |

| Output High Current (Sourcing)<br>(Voн = 1.5V, Direct Transistor Drive), PB0-PB7                             | ЮН                       | -3.0 |                          | mA                   |

| Supply Current f = 1 MHz   (No Load) f = 2 MHz   f = 3 MHz f = 3 MHz   f = 4 MHz f = 4 MHz                   | IDD<br>IDD<br>IDD<br>IDD |      | 2.0<br>4.0<br>6.0<br>8.0 | mA<br>mA<br>mA<br>mA |

| Power Dissipation (Inputs = VSS or VDD, No Loads),<br>Operating (VDD = 5.25V, f = 1 MHz)<br>Standby (Static) | РD<br>Pdsb               |      | 11.0<br>100              | mW<br>μW             |

| Input Capacitance (f = 1 MHz)                                                                                | CIN                      |      | 5.0                      | pF                   |

| Output Capacitance (f = 1 MHz)                                                                               | Соџт                     |      | 10.0                     | pF                   |

# AC Characteristics—Processor Interface Timing: VDD = $5.0V \pm 5\%$ , Vss = 0V, TA = $-40^{\circ}$ C to $+85^{\circ}$ C

| Industrial, 0° C to +70° C Commercial |                       |           |              |           |             |           |            | 7         |            |      |

|---------------------------------------|-----------------------|-----------|--------------|-----------|-------------|-----------|------------|-----------|------------|------|

|                                       |                       | G65SC32-1 |              | G65SC32-2 |             | G65SC32-3 |            | G65SC32-4 |            |      |

| Parameter                             | Symbol                | Min       | Max          | Min       | Max         | Min       | Max        | Min       | Max        | Unit |

| Cycle Time                            | tcyc                  | 1000      |              | 500       | -           | 330       | _          | 250       | _          | nS   |

| Phase 2 Pulse Width High              | tрwн                  | 470       | -            | 240       | _           | 160       | —          | 120       | _          | nS   |

| Phase 2 Pulse Width Low               | tPWL                  | 470       | —            | 240       |             | 160       | -          | 120       | -          | nS   |

| Phase 2 Transition                    | tR,F                  | -         | 30           | -         | 30          | —         | 30         | _         | 30         | nS   |

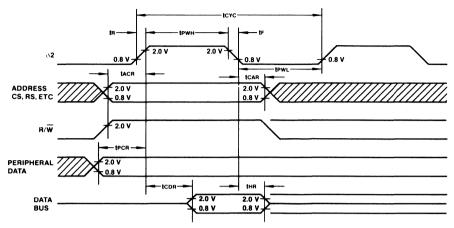

| Read Timing (Figure 1)                |                       | -         |              |           | · · · · · · |           |            |           |            |      |

| Select, R/W Setup                     | tACR                  | 160       |              | 90        | -           | 65        | _          | 45        | -          | nS   |

| Select, R/W Hold                      | tCAR                  | 0         | -            | 0         |             | 0         | -          | 0         |            | nS   |

| Data Bus Delay                        | tCDR                  | -         | 320          |           | 190         | -         | 130        | -         | 90         | nS   |

| Data Bus Hold                         | tHR                   | 10        |              | 10        | _           | 10        | -          | 10        | -          | nS   |

| Peripheral Data Setup                 | tPCR                  | 300       | _            | 150       |             | 110       | -          | 75        | -          | nS   |

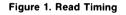

| Write Timing (Figure 2)               |                       |           |              |           |             |           |            |           |            |      |

| Select R/W Setup                      | tacw                  | 160       | -            | 90        |             | 65        |            | 45        | _          | nS   |

| Select, R/W Hold                      | tCAW                  | 0         | —            | 0         | -           | 0         | -          | 0         | -          | nS   |

| Data Bus Setup                        | tDCW                  | 195       |              | 90        | _           | 65        | -          | 45        |            | nS   |

| Data Bus Hold                         | tHW                   | 10        | -            | 10        | -           | 10        | -          | 10        |            | nS   |

|                                       | ort A) tCPW<br>ort B) | _         | 1000<br>1000 | _         | 500<br>500  | _         | 330<br>330 | -         | 320<br>250 | nS   |

# **Timing Diagrams**

Figure 2. Write Timing

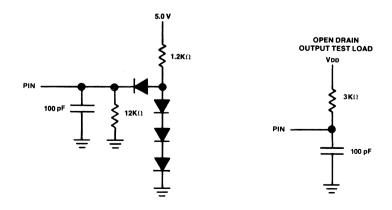

**Test Load**

## **Interface Signals**

#### Input Clock ( $\phi$ 2)

The Input Clock consists of a system  $\phi$ 2 clock source. This clock can be either a low level clock (V<sub>IL</sub> < 0.4, V<sub>IH</sub>>2.4) or a high level clock (V<sub>IL</sub> < 0.2, V<sub>IH</sub> = V<sub>DD</sub> + 0.3 "or" V<sub>DD</sub> - 0.2).

### Reset (RES)

During system initialization a Logic "0" on the RES input will cause all four I/O registers to be zeroed. This in turn will cause all lines within the I/O bus to serve as inputs. This arrangement protects external components from possible damage and/or erroneous data being written during system configuration under software control. Also, the Data Bus Buffers are placed in an Off-State during any RES. Interrupt capability is disabled during RES. The RES signal must be held low for a minimum of one clock period during a RES function.

# Interrupt Request (IRQ)

The IRQ output signal is derived from the Interrupt Control Logic, and is normally in the high state (Logic "1"). When in the low state (Logic "0"), IRQ indicates an interrupt exists within the G65SC32. This interrupt output may be activated (Logic "0") by a logical transition on line PA7 of peripheral I/O Bus A, or by timeout of the Interval Timer. Interrupt Request is an open-drain output, thus allowing several units to be wire-ORed to a common microprocessor IRQ input pin.

#### Data Bus (D0-D7)

The G65SC32 contains eight bidirectional data lines (D0-D7) for transfer of data to and from the microprocessor. The Data Buffer is active during a Read operation, and is held in the Off-State during all other operations.

#### Read/Write (R/W)

The R/ $\overline{W}$  signal is generated by the microprocessor and is used to control the transfer of data to and from the G65SC32. When R/ $\overline{W}$  is in the high state (Logic "1"), the microprocessor is allowed to read data from the G65SC32. Conversely, when R/ $\overline{W}$  is in the low state (Logic "0"), the microprocessor may write data to the G65SC32. Read/Write functions must always be preceded by proper addressing.

# Peripheral Data Ports (PA0-PA7 and PB0-PB7)

The G65SC32 contains two 8-bit peripheral I/O Ports...Port A (lines PA0-PA7) and Port B (lines PB0-PB7). An important feature of the G65SC32 is that each peripheral port bus line is individually programmable as either an input or an output. Data flow direction may be selected on a line-by-line basis with intermixed input and output lines within the same port. This feature is accomplished by the Data Direction Registers. When a "0" is written to any bit position of the Data Direction Register (DDRA or DDRB), the corresponding line will be programmed as an input. Likewise, when a "1" is written into any bit position of DDRA or DDRB, the corresponding data line will serve as an output.

When an I/O Port line has been programmed as an input and its Output Register (ORA or ORB) is read by the microprocessor, the TTL level on the I/O Port line will be transferred to the Data Bus (D0-D7). When programmed as outputs, the I/O Port lines will reflect data as written by the microprocessor into the Output Registers. I/O Port line PA7 also serves an Edge Sense Interrupt function as described in the following sections.

Address and Select Lines (A0-A6, RS, CS1 and CS2) Address lines A0-A6 serve to address the RAM, I/O Registers, Timer and Flag Register. CS1 and  $\overline{CS2}$  are used to select (enable access to) the G65SC32.

### **Functional Description**

In reference to the Block Diagram on page one, the G65SC32 is shown to consist of four basic functions; that is, RAM, I/O, Timer and Interrupt Control. RAM interfaces directly with the microprocessor by way of the Data Bus and Address Lines. The peripheral I/O functions consist of two 8-bit I/O Ports. Each port is supported by a Data Direction Register and an Output Register.

# RAM (128 Bytes, 1024 Bits)

Within the G65SC32 is a 128 X 8 bit static RAM. This RAM is used as a scratch pad or special data buffer, and is addressed by A0-A6 (Byte Select), RS, CS1 and CS2.

# Peripheral I/O Port Registers

The peripheral I/O Port Registers consist of two Data Direction Registers and two data Output Registers. The Data Direction Register (A and B) controls the direction of data into and out of the peripheral I/O Ports as described under the Peripheral Data Ports Section above. The voltage level on any I/O Port line which has been programmed as an output, is determined by the corresponding bit in the Output Register (ORA or ORB).

During a peripheral Read operation over I/O Port A, data is read directly from the I/O Port bus (PA0-PA7). During this Read operation, should a particular PA line be programmed as an output, data transferred into the microprocessor will be identical to the corresponding data in Output Register A providing that line loading is such that the line voltage is  $\ge$ 2.4 volts for a Logic "1", and  $\le 0.4$  volts for a Logic "0". Under severe loading conditions where these voltage limits cannot be guaranteed, the resulting Read operation may not match the contents of Output Register A.

The output buffer which services I/O Port B (PB0-PB7) is different from the buffers for I/O Port A. The buffers for Port B are push-pull devices capable of sourcing 3 mA at 1.5 volts. This allows these lines to directly drive transistor circuits. To ensure valid data will be read during a peripheral Read operation, I/O Port B contains logic which allows the microprocessor to read the contents of Output Register B instead of reading directly from the Port B data bus.

#### **Interval Timer**

Figure 3 shows the three basic functions of the Interval Timer section. These functions include: a preliminary divide-down register, a programmable 8-bit register, and all necessary interrupt logic.

Figure 3. Basic Functions of Interval Timer

The Interval Timer can be programmed to count up to 256 time intervals. Each time interval can be selected as 1T, 8T, 64T, or 1024T increments, where T is the system clock ( $\phi$ 2) period. When a full interval count has been reached, the interrupt flag is set to the Logic "1" state. Once the flag has been set, the internal clock starts counting down at a 1T rate to a maximum count of -255T. This arrangement allows the user to read the counter and thus determine the elapsed time since the interrupt was set.

The G65SC32's internal Data Bus is used to transfer data to and from the Interval Timer. For example, if a count of 52 time intervals is desired, the pattern 00110100 would be put on the Data Bus and written into the Interval Time Register, During the time when data is being written into the Interval Timer, timing intervals 1,8,64 and 1024T are decoded from address lines A0 and A1. During Read and Write operations, address line A3 controls the interrupt capability of IRQ. That is, when A3=1, IRQ is enabled. When A3=0, IRQ is disabled. In either case, when timeout occurs, bit 7 of the Interrupt Flag Register is set. This flag is cleared when the Timer register is either read to or written from by the microprocessor. When IRQ is enabled by A3 and an interrupt occurs, IRQ will go low. Should the Timer be read prior to the interrupt flag being set. the number of remaining time intervals will be read, i.e., 51, 50, 49, etc.

Once the Timer has counted down to 0000000, an interrupt will occur on the next count time which will result in the Timer reading 1111111. Following the interrupt, the Timer registers decrements at a divide by "1" rate of the clock system. After interrupt, should the Timer read a value of 11100100, then the time since the last interrupt is 28T. The value read is in two's complement as follows:

Value read = 11100100 Complement = 00011011 Add 1 = 00011100 = 28Τ (28 φ2 clock periods)

Thus, to arrive at the total elapsed time since the Timer count was originally program set, simply perform a two's complement of the Timer value and add this to the original time value written into the Timer. For example, assume the original time written was 00110100 (=52). With a divide-by-8T, total time to interrupt would be (52 X 8) + 1 = 417T. In this case, total elapsed time would then be 416T + 28T = 444T, assuming the value read after interrupt was 11100100.

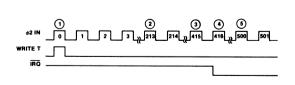

Following an interrupt, whenever the Timer is read or written the interrupt is reset. However, should the Timer be read at the same time the interrupt occurs, the interrupt flag will not reset. Figure 4 is an example of Timer Interrupt Timing.

- 1. Data written into Interval Timers: 00110100 = 5210

- 2. Data in Interval Timer: 000110100 =  $25_{10}$ i.e., 52 -  $\frac{213}{8}$  - 1 = 52 - 26 - 1 = 25

- 3. Data in Interval Timer: 00000000 =  $0_{10}$ i.e., 52 -  $\frac{415}{8}$  - 1 = 52 - 51 - 1 = 0

- Interrupt occurred at φ2 clock pulse number 416 Data in Interval Timer = 11111111

- 5. Data in Interval Timer: 10101100 Two's complement: 01010100 = 84<sub>10</sub> Therefore, 84 + (52 x 8) = 500<sub>10</sub>

When reading the timer following an interrupt, address line A3 must be low such that  $\overline{IRQ}$  will be disabled. This procedure prevents future interrupts until a future Write operation has occurred.

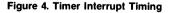

# Interrupt Flag Register

The Interrupt Flag Register consists of two bits ... the Timer interrupt flag (bit 7) and the PA7 Edge Sense Interrupt flag (bit 6). Whenever a Read operation is performed on the Interrupt Flag Register, the two bits are transferred to the microprocessor via the internal Data Bus. Figure 5 shows the Interrupt Flag Register bit configuration.

It should be noted that the PA7 flag is cleared when the Interrupt Flag Register is read. Also, the Timer flag is cleared when the Timer is either read or written.

#### Addressing

The G65SC32 is addressed by way of the 7-bit Address Bus (A0-A6), the  $\overline{RS}$  input, and the two Chip Select inputs (CS1 and CS2). To address the RAM, CS1 must be high with  $\overline{CS2}$  and  $\overline{RS}$  must be high with  $\overline{CS2}$  and  $\overline{RS}$  must be high with  $\overline{CS2}$  and  $\overline{RS}$  must be high with  $\overline{CS2}$  advector  $\overline{CS1}$  and  $\overline{RS}$  must be high with  $\overline{CS2}$  advector  $\overline{CS1}$  and  $\overline{RS}$  must be high with  $\overline{CS2}$  advector  $\overline{CS1}$  and  $\overline{RS}$  must be high with  $\overline{CS2}$  advector  $\overline{CS1}$  must be high and  $\overline{CS2}$  must be low. The  $\overline{RS}$  input is used to distinguish between the RAM and the I/O — Interval Timer Sections. When  $\overline{RS}$  is low, RAM is addressed. When  $\overline{RS}$  is high, the I/O — Interval Timer and I/O, address line A2 is used. With A2 high, the Interval Timer is accessed. Table 1 provides addressing requirements for the G65SC32.

### Edge Sense Interrupt

In addition to its use as a peripheral I/O line, PA7 can also function as an Edge Sense Interrupt input. In the interrupt mode, an active transition on line PA7 will set the internal interrupt flag (bit 6 of the Interrupt Flag Register). When this occurs, providing the PA7 interrupt has been enabled, the IRQ output will go low.

Control of the PA7 edge detection logic is accomplished by a Write operation to one of four addresses. The data lines for this Write operation are "don't care" and the addresses to be used can be found in Table 1.

Setting the internal interrupt flag by an active transition on PA7 is always enabled, independent of whether PA7 is set up as an input or output by the Data Direction Register.

The Reset signal (RES) will disable the PA7 interrupt and at the same time set the active transition logic to the negative edgedetect state. During the RES operation, the interrupt flag may

Address Decoding

be set by a negative transition of PA7. This being the case, it may therefore be necessary to clear the interrupt flag prior to being enabled for its normal use as an edge detecting input. This special Reset can be achieved by reading the Interrupt Flag Register.

#### I/O Register—Timer Addressing

Table 1 provides the address decoding for all internal functions and Timer programming. Address line A2 distinguishes the I/O registers from the Timer. When A2 is low and  $\overline{RS}$  is high, the I/O registers are addressed. Once the I/O registers are addressed, address lines A1 and A0 may be used to address the desired register.

With A2 high and  $\overline{RS}$  high, the Timer is selected, and address lines A1 and A0 are available to decode the "divide-by" matrix as defined in Table 1. Address line A3 is used to enable the interrupt flag to the IRQ output.

| Operation                                                     | RS               | R/W                   | A4          | A3                              | A2               | A1               | A0                    |

|---------------------------------------------------------------|------------------|-----------------------|-------------|---------------------------------|------------------|------------------|-----------------------|

| Write RAM<br>Read RAM                                         | 0                | 0                     | _           | =                               | _                | =                | _                     |

| Write Output Reg A<br>Read Output Reg A                       | 1                | 0<br>1                | _           | _                               | 0                | 0<br>0           | 0<br>0                |

| Write DDRA<br>Read DDRA                                       | 1                | 0<br>1                | _           | _                               | 0<br>0           | 0<br>0           | 1                     |

| Write Output Reg B<br>Read Output Reg B                       | 1                | 0<br>1                | _           | _                               | 0<br>0           | 1                | 0<br>0                |

| Write DDRB<br>Read DDRB                                       | 1                | 0                     | _           | _                               | 0<br>0           | 1                | 1                     |

| Write Timer<br>÷ 1T<br>÷ 8T<br>÷ 64T<br>÷ 1024T<br>Read Timer | 1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>1 | 1<br>1<br>1 | (a)<br>(a)<br>(a)<br>(a)<br>(a) | 1<br>1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0 |

| Read Interrupt Flag<br>Write Edge Detect Control              | 1                | 1                     |             |                                 | 1                | (b)              | 1<br>(c)              |

# Table 1. G65SC32 Address Decoding

Notes: — = Don't Care, "1" = High Level ( $\ge 2.4V$ ), "0" = Low Level ( $\le 0.4V$ )

(a) A3 = 0 to Disable Interrupt from Timer to IRQ

A3 = 1 to Enable Interrupt from Timer to IRQ

(b) A1 = 0 to Disable Interrupt from PA7 to  $\overline{IRQ}$

A1 = 1 to Enable Interrupt from PA7 to IRQ

(c) A0 = 0 for Negative Edge-Detect

A0 = 1 for Positive Edge-Detect

G65SC32

# **Application Diagram**

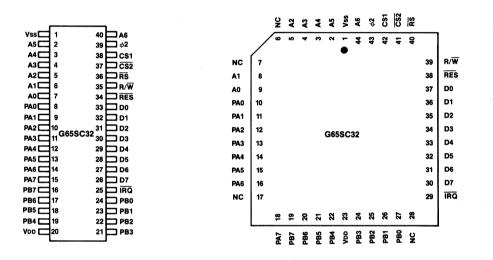

# Pin Function Table

| A0-A6   | Address Bus            | RS  | Function Select       |

|---------|------------------------|-----|-----------------------|

| D0-D7   | Data Bus               | R∕₩ | Read/Write            |

| PA0-PA7 | Peripheral I/O Port A  | RES | Reset                 |

| PB0-PB7 | Peripheral I/O Port B  | IRQ | Interrupt             |

| φ2      | Phase 2 Internal Clock | VDD | Power Supply (+5V)    |

| CS1/CS2 | Device Select          | Vss | Internal Logic Ground |

# **Pin Configuration**

# **Ordering Information**

|                                    |                                                            | <u>G</u> 65SC32 | <u>P I -2</u> |

|------------------------------------|------------------------------------------------------------|-----------------|---------------|

| Description                        |                                                            |                 |               |

| C-Special C                        | -Standard                                                  |                 |               |

| Product Identi                     | fication Number                                            |                 |               |

| Package                            |                                                            |                 |               |

| P—Plastic<br>C—Ceramic<br>D—Cerdip | E—Leaded Chip Carrier<br>L—Leadless Chip Carrier<br>X—Dice |                 |               |

| Temperature/F                      | rocessing                                                  |                 |               |

|                                    | to +70° C, ± 5% P.S. Tol.<br>to +85° C, ± 5% P.S. Tol.     |                 |               |

| Performance D                      | Designator                                                 |                 |               |

| Designators se                     | lected for speed and power                                 | specifications  |               |

| —1 1MHz<br>—2 2MHz                 | —3 3 MHz<br>—4 4 MHz                                       |                 |               |