Er is ooit een vergelijking gemaakt tussen mens en computer: de hardware is het vlees en bloed, de software de geest. Vanaf een zekere leeftijd is de lichamelijke groei van de mens voltooid; de geestelijke groei gaat gewoon door. De junior-computer is nu volgroeid; alle nodige hardware is beschikbaar. De software kan verder groeien. Vergeten we even gebruikersprogramma's in machinetaal, en ook allerlei systeemsoftware (zoals de twee "softwarehulpstukken" die in een ander artikel in dit nummer aan bod komen), dan is natuurlijk de hamvraag: hoe zit het met een hogere programmeertaal? Het staat hoe groot de kaart is) als het gaat om de vraag wat de gebruikersmogelijkheden ervan zijn. Bij de behoefte aan uitbreidingen is dat "alles" op één kaart" vaak een blok aan het been. Men heeft verkeerd gegokt bij de aanschaf: dat krijg je als je alles op één kaart zet.

"Single board" wordt vooral toegepast bij oefen/leersystemen en bij relatief eenvoudige procesbesturingen (waarbij de computer permanent is ingeschakeld). In zijn standaardvorm is de junior-computer een "single board"computer. En bedoeld voor de al genoemde toepassingen. Duizenden

# resterende soldeerpunten

# **junior - hardware kompleet**

In dit artikel worden de laatste stenen aangedragen waarmee, samen met al eerder door Elektuur gepubliceerde computerbouwstenen, het junior-computerbouwwerk kan worden voltooid. De interface-kaart speelt daarbij een sleutelrol als verbindingsschakel met een video-display plus ASCII-toetsenbord (elekterminal), als drager van extra RAM- en EPROM-geheugen en van extra I/O, als begin van een gebufferde bus voor de aansluiting van (een) geheugenkaart(en) en last but not least als data-doorgever van en naar cassette-band.

Dit artikel is een korte vooruitblik op een paar honderd bladzijden boek 3 (verschijnt binnenkort, in twee delen). Kort, dus het verhaal kan niet anders dan onvolledig zijn. Dat neemt niet weg dat het verhaal gaat over de nu volledige hardware. wel vast dat de voorkeur uitgaat naar BASIC. Het staat ook wel vast dat, als het feest doorgaat (hoe groot is uw belangstelling eigenlijk?), zo'n BASIC (bijvoorbeeld 8K-BASIC op cassette in kombinatie met 16K-RAM) zal zijn gebaseerd op bestaande, niet door Elektuur ontworpen of te ontwerpen software. U gelieve hierover hardop na te denken; individueel of in gebruikersklubverband.

(Een 16K-dynamische-RAM-kaart staat hoe dan ook op stapel. Geen wezenlijke hardware-uitbreiding, maar een goedkoop alternatief voor twee RAM/ EPROM-kaarten met elk 8K-RAM).

Maar alles op zijn tijd. Terug naar wat nu aan de orde is. Welke aanvullende hardware is er (nodig)? En hoe ziet het systeem er dan uit? Of liever gezegd: kan er uitzien? Want er "moet" niets.

# Bus, kaart en buskaart

Vooral voor amateurgebruik bedoelde computersystemen zijn er in twee soorten: bussystemen en "single board"systemen. Bij een bussysteem is elk onderdeel op een kaart (= print) ondergebracht. De kaarten zijn onderling even groot (bijvoorbeeld eurokaart: 100 x 160 mm) en doorverbonden via een 'bus", dat is een raamwerk van leiwaarbij punten met gelijke ainaen positie (bijvoorbeeld konnektorpennen) onderling zijn doorverbonden. De praktische uitvoering is soms via draadverbindingen, soms via een print: de buskaart. De lengte van de bus is in principe onbeperkt. Het bussysteem is universeel; het kan (gaandeweg) zeer uitgebreid worden met als gevolg een computer met vele gebruiksmogelijkheden.

Bij een "single board"-systeem is alles op één kaart gezet. Het hangt er maar helemaal van af wat er op zit (en dus

Scanned by HansO 2003

gebruiken hem zo. Er is kennelijk sprake van een "Campari"-effekt: je hoort en leest zo veel over "chips" en "computers" dat het interessant wordt om er zelf iets mee te gaan doen, al is het maar één keer in je leven. Vele applikaties (gebruik van de poorten) van de juniorcomputer zijn ons bekend, variërend van A/D-omzetters tot de sturing van een opdampproces bij de halfgeleiderfabrikage. Er is niets op tegen om het te te houden bij de (legio) mogelijkheden van de standaard-junior-computer en gewoon te vergeten dat er een uitbreidingskonnektor is.

Toch is die uitbreidingskonnektor er niet zo maar. Hij biedt de mogelijkheid om de meest voor de hand liggende (lees: de meest noodzakelijke) uitbreidingen te realiseren, te weten: voorzieningen voor het gebruik van de magnetische geluidsband als achtergrondgeheugen (zodat een RAM met geheugenverlies geen RAMp meer hoeft te betekenen), de mogelijkheid om de maximale hoeveelheid geheugen (64K) te gebruiken en alles wat nodig is om randapparatuur zoals bijvoorbeeld een video-terminal aan te sluiten. Eventuele extra I/O is mooi meegenomen.

Zodra de uitbreidingskonnektor wordt gebruikt is de junior-computer niet meer 'single board". Wil dat zeggen dat het nu zo'n in meerdere opzichten "eindeloos" bussysteem gaat worden? Nee. Er is al iets gezegd over afrondende hard ware. Dat is iets anders dan "eindeloos" Verder lijkt de fysieke opzet van het uitgebreide systeem helemáál niet op een zuiver bussysteem. Al de reeds genoemde uitbreidingen (op het grootste deel van de geheugenuitbreiding na) zitten op de interface-kaart, die net zo groot is als de basiskaart (hoofdprint) van de junior-computer, en daaronder wordt geplaatst. Aan de interface-kaart

kan een bestaande SC/MP-buskaart worden gekoppeld, die als drager dient voor één of meerdere geheugenkaarten. Ondanks de mogelijke aanwezigheid (mogelijk, want hij kan achterwege blijven) van een buskaart is de uit-gebreide junior-computer geen bus-systeem. Maar wat dan wèl? Gezien de sandwich-konstruktie van interface-kaart en basiskaart kun je misschien nog het beste spreken van "double single board". Nog belangrijker dan de vraag welke naam het beestje moet krijgen is de beschrijving van het beestie. En wel nu.

# De interface-kaart

Het woord "interface" betekent koppeling, aanpassing. In ons geval de koppeling van de junior-computer met de buitenwereld via extra I/O, de koppeling met de magnetische band (cassetteinterface), de koppeling met randapparatuur (RS-232-interface) plus een interne interface van en naar de standaardkaart via buffering.

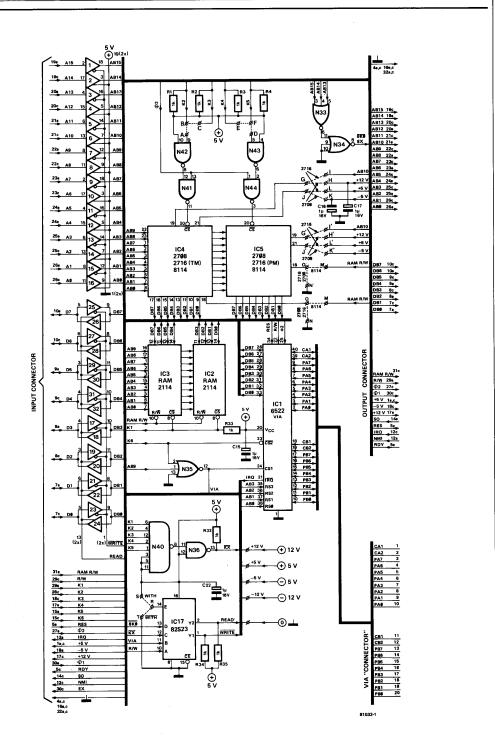

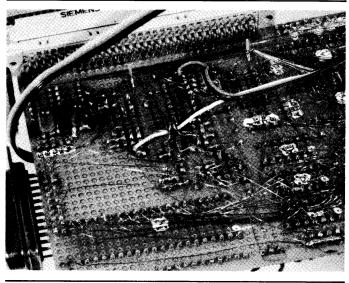

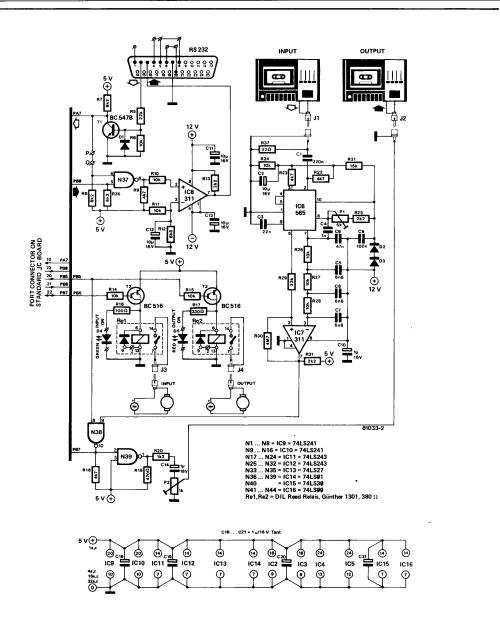

Alle elektronica op de interface-kaart is terug te vinden in de figuren 1 en 2. Die elektronica is omvangrijker dan die van de basiskaart en zit toch op een print met gelijke afmetingen. Dat is geen eenvoudige zaak geweest, neem dat van ons aan. De diverse onderdelen zullen nu stuk voor stuk worden besproken.

#### Buffering: tegen een stootje kunnen

Links in figuur 1 zien we alle aansluitingen van de ingangskonnektor (INPUT CONNECTOR), Via deze konnektor en via vijf verbindingen met de poortkonnektor (zie figuur 2) verloopt de kommunikatie met de standaardjunior-computer. Op de leidingen EX en  $K1 \dots K6$  na – die zijn uitsluitend van belang voor de interface-kaart - vinden we alle leidingen terug bij de uitgangskonnektor (OUTPUT CONNECTOR), rechtsboven in figuur 1. De uitgangskonnektor dient voor de koppeling met de buskaart, die op zijn beurt zorg draagt voor de koppeling met één of meer geheugenkaarten.

Adreslijnen A zien we terug als AB en datalijnen D als DB. De B staat voor: gebufferd. Waarom buffering? Om twee redenen. Ten eerste is buffering noodzakelijk om elektrische overbelasting als gevolg van een te groot aantal aansluitingen te voorkomen. Ten tweede omdat het in het geval van de datalijnen nu mogelijk is om de datastroom tussen de standaard-junior-computer en alles daarbuiten (interface-kaart, één of meer geheugenkaarten) te blokkeren als dat wenseliik is.

De adresbuffers zijn N1 . . . N16. Omdat adressering altijd vanuit de 6502 op de standaardkaart plaatsvindt, staan de driehoeken in de aangegeven richting: ingang links, uitgang rechts. De databuffers zijn N17 . . . N32. Hier is sprake van een even genummerde groep buffers met ingang rechts, uitgang links, en een groep oneven genummerde buffers met ingang links, uitgang rechts. Er zijn drie situaties modelijk:

De oneven genummerde poorten N17...N32 zijn aktief, de even genummerde inaktief. Dat is het geval als WRITE en READ "0" zijn. Er is een datastroom mogelijk van de standaardkaart naar de uitbreidingen. Dat is het geval bij het schrijven van data in nietstandaardgeheugen of -I/O.

De oneven genummerde poorten N17...N32 zijn inaktief ("tri-state" oftewel hoogohmig aan ingang en uitgang), de even genummerde aktief. Dat is zo als WRITE en READ "1" zijn. Er is een datastroom mogelijk van de uitbreidingen naar de standaardkaart. Dat is het geval bij het lezen van data uit niet-standaardgeheugen of -I/O.

Alle poorten N17...N32 zijn inak-tief, als WRITE ''1" is en READ ''0". De datastroom is geblokkeerd. Deze situatie is relevant bij het lezen of schrijven van data op standaardgeheugen of -I/O. De signalen WRITE en READ komen uit de PROM IC17. Daarover later meer.

# N.B. De vierde mogelijkheid:

WRITE = "0" en READ = "1" houdt in dat alle poorten N17... N32 tegelijkertiid aktief ziin. Deze situatie is ongewenst.

# Extra I/O

De VIA IC1, van het type 6522, is een hoofdstuk apart. En wel een hoofdstuk van de tweede helft van boek 3. Hier zij opgemerkt dat deze "Versatile Interface Adapter" nog meer mogelijkheden in huis heeft dan de standaard-I/O-bouwsteen (PIA) van het 6532. De relevante verbindingen met de buitenwereld zijn te vinden bij de VIA "CONNECTOR" in figuur 1 (is geen echter konnektor, vandaar de aanhalingstekens). De 6522 wordt gestuurd vanuit de adreslijnen ABØ...AB3 en met diverse signalen van de stuurbus. De aanwezigheid van acht datalijnen zal ook niemand verbazen, evenals het uitgangssignaal IRQ (interrupt na de time out van een timer).

Evenals de 6532 heeft de 6522 twee chipselect-signalen.  $\overline{CS2}$  is net zoals de CS2 van de 6532 verbonden met het uitgangssignaal K6 van de adresdekoder IC6 op de standaardkaart van de juniorcomputer; CS1 ligt aan de uitgang van N35, die wordt gestuurd door K6 en AB9. Voor de aktivering van de VIA moet niet alleen CS2 "0" zijn, maar ook CS1 "1". Nu is N35 een NOR-poort; de uitgang ervan is "1" als alle ingangen nul zijn, dus als AB9 en K6 nul zijn (voor de 6532 moet A9 juist "1" zijn). Als we verder bedenken dat A8 (AB8) niet is aangesloten op de 6522 en ook niet op de 6532, dan geldt voor de VIA 6522 het volgende adresbereik:

1800 = 1900 . . . 18FF = 19FF (AB8 = X; AB9 = "0"; K6 = "1")

en voor de PIA 6532 het adresbereik: 1AØØ = 1BØØ . . . 1AFF = 1BFF (A8 = X; A9 = ''1''; K6 = ''1'')

Sluiten we de dubbeladressering vanwege A8 = AB8 = X uit, dan zijn er zoveel voor de PIA als voor de VIA 256 adressen beschikbaar. Net als bij de 6532-PIA (19 verschillende "geheugen-plaatsen" die meervoudig zijn geadresseerd) zijn bij de VIA niet op al die 256 adressen 256 verschillende geheugenplaatsen aangesloten. Zoals men ziet in figuur 1 zijn de adreslijnen AB4...AB7 niet aangesloten. Er zijn dus 16 verschillende VIA-geheugenplaatsen.

#### Extra geheugen

Op de interface-kaart is plaats voor extra geheugen. En wel zo veel (maxi-

junior-hardware kompleet

1

Figuur 1. Deze schakelingen van de interface-kaart hebben betrekking op geheugenuitbreiding, extra I/O, buffering inklusief databuffersturing en volledige adresdekodering. maal 5K, geselekteerd door K1...K5) dat de volledige standaard-gedekodeerde 8K wordt benut (met inbegrip van 1K voor de PIA plus VIA).

Allereerst RAM. Los van andere mogelijkheden heeft men sowieso de beschikking over 1K RAM via IC2 en IC3 van figuur 1 (1024 data-nibbles per IC). De RAM wordt geselekteerd als K1 =  $\overline{CS}$  "0" is. Dit betekent voor deze RAM het adresbereik: 0400...07FF.

Dat zijn dus de vier pagina's Ø4...07; dat sluit mooi aan op de standaard-RAM-pagina's Ø0...03, zodat grotere gebruikersprogramma's "aan één stuk" mogelijk worden.

Voor zowel IC4 als IC5 kan men naar keuze 1K-RAM (8114), 1K-EPROM (2708) of 2K-EPROM (2716) nemen. De selektie gebeurt met één of twee signalen K2...K5 per IC en met behulp van het clock-signaal  $\Phi 2$ (poorten N41...N44). Dat laatste vanwege een goede timing van het lezen en (indien van toepassing) schrijven. De adressering ziet er als volat uit:

$\begin{array}{l} K2=`'0'' \rightarrow adressen \ 0800 \ldots 0 BFF \rightarrow \% \ of \ 1 \times 1C4 \\ K3=''0'' \rightarrow adressen \ 0C00 \ldots 0 FFF \rightarrow \% \ of \ 1 \times 1C4 \\ K4=''0'' \rightarrow adressen \ 0000 \ldots 13FF \rightarrow \% \ of \ 1 \times 1C5 \\ K5=''0'' \rightarrow adressen \ 1400 \ldots 17FF \rightarrow \% \ of \ 1 \times 1C5 \end{array}$ Voor 1K-RAM (8114) of 1K-EPROM (2708) heeft men per IC meerdere selektiemogelijkheden. Voor 2K-EPROM (2716) worden twee K's gekombineerd: K2 & K3 voor IC4 = 2716 (adresbereik Ø8ØØ....ØFFF) en K4 & K5 voor IC5=2716 (adresbereik 1ØØØ...17FF). Ten behoeve van deze adresselektie zijn de soldeerpennen A . . . F aanwezig; deze moeten afhankelijk van de keuze voor IC4 en IC5 op een bepaalde manier met elkaar worden doorverbonden. Hetzelfde geldt voor de pennen G ... 0 en G'... O'. Verbindingen tussen deze punten hangen samen met de keuze van de voedingsspanningen en met de vraag of een extra adresijin AB10 of het signaal RAM-R/W nodig is of niet.

### Volledige adresdekodering

In de standaard-junior-computer is slechts 8K van de 64K gedekodeerd; de adreslijnen A13, A14 en A15 spelen dan geen enkele rol. Met als gevolg dat elk adres acht keer voorkomt. Pagina's  $\emptyset X$ , met  $X = \emptyset ... F$ , bereik je óók op de pagina's 2X, 4X, 6X, 8X, AX, CX en EX. Pagina's 1X, met  $X = \emptyset ... F$ , kom je ook tegen op de pagina's 3X, 5X, 7X, 9X, BX, DX en FX. Het gaat om de situatie waarbij het punt D van de adresdekoder IC6 op de basiskaart van de junior-computer aan massa ligt via een draadbrug.

Willen we een geheugenuitbreiding van meer dan 5k, dus moeten we een beroep doen op (een gedeelte van) het adressbereik 2000...FFFF, dan zal de adresdekodering volledig(er) moeten zijn. Gaan we ervan uit dat de aanvullende 5K op de interface-kaart zit, dan moet de adresdekodering dus worden aangepakt in het geval dat er één of meerdere geheugenkaarten via de buskaart op de interface-kaart zijn aangesloten. Dus als men zich beperkt tot geheugenuitbreiding, uitsluitend op de interface-kaart, dan is een volledige(r) adresdekodering niet strikt noodzakelijk.

De adresdekodering maken we als volgt volledig: Allereerst komt punt D van IC6 van de standaard-junior-computer aan het punt EX te liggen; draadbrug verleggen naar EX! (in dit teorie-verhaal alvast een belangrijke bouwtip). Het punt EX = D ligt aan de uitgang van inverter N34, die wordt gestuurd uit de NOR-poort N33, die op zijn beurt de adreslijnen AB13, AB14 en AB15 ontvangt. Zodra één van deze drie adreslijnen ook maar "1" is wordt EX en daarmee punt D van IC6 "1", met als gevolg dat geen van de uitgangssignalen КØ . K7 van IC6 laag is. Zijn alle drie adreslijnen AB13...AB15 nul, dan is punt D van IC6 nul (ligt als vanouds aan massa) en wordt één van de signalen KØ . . . K7 nul. Met andere woorden: te adresseren I/O of geheugen op de standaardkaart en op de interface-kaart is nu uitsluitend bereikbaar op de pagina's  $\emptyset X$  en 1X, met  $X = \emptyset \dots F$ ; de pagina's 2X en hoger zijn te bereiken via de buskaart. Aanvullende adresdekodering op de RAM/EPROM-kaart of de 16K-dynamische RAM-kaart is nodig voor de keuze van één of meerdere geheugengebieden uit het relevante adresbereik 2000 ... FFFF.

Het uitgangssignaal EX gaat, verkleed als 8KØ, eveneens naar een adresingang van de PROM IC17. Deze PROM bevat 32 bytes van elk 8 bits, van die acht zijn alleen de bits Y1 (= WRITE) en Y2 (= READ) van belang. Deze bits sturen de databuffers N17...N32. Voor 32 bytes zijn de vijf adreslijnen E...A genoeg; die adreslijnen bestaan uit vijf, direkt nader te omschrijven signalen. Waarom doen we zo moeilijk met die PROM? Tenslotte moet je die (laten) programmeren (kan bij Elektuur: ESS508) en uit wat er in het hoofdstukje over buffering is gezegd zou je kunnen konkluderen dat kan worden volstaan met de aansluiting van het signaal R/W op READ en op WRITE. Waarom moeilijk doen als het makkelijk kan?

Om twee redenen. Ten eerste: stel we lezen data van RAM, EPROM of I/O op de basiskaart van de juniorcomputer. Als R/W direkt is aangesloten op READ = WRITE, staan er tijdens dat lezen acht databuffers met de ingang gericht op de standaard-databus. Hun ingangen hangen niet effektief aan geheugen (omdat dat geheugen immers niet is geadresseerd). Die ingangen leiden dus een vrij leven: elke ingang kan nul zijn of één. De uitgangen van de buffers zijn laagohmig (daar zijn het buffers voor) en ze kunnen dus de databus "hun vrije wil opleggen", met als gevolg mogelijk foute gelezen data. Om dit allemaal te voorkomen is het verreweg het beste om in dat geval de databuffers stuk voor stuk te blokkeren de 6502 heeft dan achter de buffers immers niets te zoeken. N.B. Bij het schrijven van data op de basiskaart doen dergelijke problemen zich niet voor.

Er is nog een tweede reden voor die PROM. De vektoren NMI, RES en IRQ kunnen nu (lees: met volledige adresdekodering) worden opgehaald op de echte adressen FFFA...FFFF, in plaats van op de adressen 1FFA... ..FFF (standaard-EPROM ESS503; versie D). Dat is alleen zinvol als op (onder meer) pagina FF daadwerkelijk EPROM is aangesloten, met de juiste vektordata (pagina FF zit op een via de buskaart aangesloten RAM/EPROMkaart; in zo'n geval spreken we voortaan

#### junior-hardware kompleet

van buskaartgeheugen). Als dat allemaal niet het geval is moeten de vektoren uit de standaard-EPROM komen. Dat gebeurt net als vroeger door de zaak te beduvelen: isoleer de databuffers en de adreslijnen A15, A14 en A13 zijn net als vroeger niet van belang omdat ze nergens zijn aangesloten op de basiskaart.

tabel 1

(hex)

l-adres

PROM-

ØØ Ø Ø

Ø1 Ø Ø Ø Ø

Ø2 Ø Ø

ØЗ Ø Ø Ø

Ø4 Ø Ø

Ø5 Ø

Ø6 Ø

Ø7 Ø

Ø8

Ø9

ØA

ØВ Ø 1 Ø

ØC Ø

ØD Ø 1

ØF Ø 1

ØF

10 1 Ø Ø Ø Ø Ø

11

Ø

Ø

Ø

Ø 1

1

E = WITH of WITH

8K0

-0 °,

Ø

Ø

Ø

1

Ø Ø Ø 1

⊠

Ø

Ø 1

> Ø ¢ 1

Ø

1 1

N.B. Zodra er buskaartgeheugen is aangesloten moet er (onder meer) op pagina FF EPROM zijn aangesloten met gespecificeerde vektor-data. Er is dan geen keuze mogelijk tussen vektoren ophalen in pagina FF en vektoren ophalen in pagina 1F. Dat laatste zou namelijk isolatie van de buffers betekenen, en dan heeft buskaartgeheugen geen zin.

Terug naar de adressering van de PROM IC17 De vijf adressignalen, die via WRITE en READ invloed uitoefenen op de toestand van de databuffers zijn: A. Het signaal R/W of eigenlijk  $R/\overline{W}$  (is

niet konsekwent zo gedaan bij al het geschrevene over de junior-computer; het streepje betekent: aktief indien logisch nul). Hangt samen met de vraag of er sprake is van lezen of schrijven. Vrij logisch dat-ie erbij hoort.

B. Het signaal VIA. Komt uit N35 en is tevens de CS1 van de VIA IC1. Is "1" als K6 en AB9 nul zijn. Dus als de VIA is geselekteerd. Van het 1K-gebied met K6 = "Ø" zit de PIA vóór de databuffers en de VIA erachter. C. Het signaal  $\overline{KX}$ . Dit is afkomstig uit

N36, die de uitgang van N40 aktiveert, ls nul als één van de leidingen K1...K5 nul is, dus als er geheugen op de interface-kaart aan bod is.

D. Het signaal 8KØ is gelijk aan EX (eerder al behandeld) en is nul als de eerste 8K wordt gedresseerd (geheugen en I/O op de basiskaart en op de interface-kaart) en "1" als buskaartgeheugen is geadresseerd.

E. Punt E van IC17 is of met +5 V verbonden (draadbrug RS), of met massa (draadbrug RT). Punt E moet nul zijn als er geen buskaartgeheugen is aangesloten (vandaar het bijschrift WITH, hetzelfde als WITHOUT) en één als dat wel het geval is (bijschrift WITH, hetzelfde als WITHOUT). Waarom hier een draadbrug RS of RT? Wel, heel simpel omdat u dan de vrijheid heeft om buskaartgeheugen aan te sluiten of niet. U ziet het: niets moet, alles mag.

In tabel 1 is de inhoud van de PROM IC17 overzichtelijk samengevat (ESS508). De bits Y3...Y8 zijn nul en spelen verder geen enkele rol. In prin-cipe zijn er 32 verschillende situaties mogelijk die leiden tot een keuze uit één van de drie toegestane kombinaties van READ & WRITE. In werkelijkheid zijn het er veel minder. Afgezien van de opdeling in lezen en schrijven blijven er acht situaties over:

1. Schrijven of lezen van geheugen op interface-kaart (IC2 . . . IC5). de Acht databuffers staan in de door lezen of schrijven bepaalde richting ("enabled") (PROM-adressen ØØ en Ø1).

Ø Ø Ø Ø Ø 12 Ø Ø ø Ø Ø ø ØØ 1 1 13 Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø ØØ 1 14 1 ¢ Ø Ø Ø Ø Ø Ø Ø Ø Ø Ø1 15 Ø Ø Ø Ø Ø Ø Ø Ø Ø1 1 Ø 1 1 16 1 Ø Ø Ø Ø ø Ø Ø Ø Ø ØØ Ø Ø 17 Ø Ø Ø Ø Ø Ø 1 ØЗ 1 1 1 Ø Ø Ø 18 1 Ø Ø Ø Ø Ø Ø Ø ØØ 1 Ø Ø Ø ø Ø ØØ Ø Ø Ø 19 1 Ø Ø 1 Ø 1 Ø Ø Ø ØØ Ø Ø 1A Ø Ø Ø Ø Ø 1 1 1 ø Ø Ø Ø Ø ØØ 1B Ø ø Ø Ø 1 1 1 1 Ø Ø Ø Ø Ø Ø Ø Ø Ø ØØ 1C Ø 1 1 1 Ø Ø Ø 1D Ø Ø Ø 1 Ø3 Ø Ø Ø Ø Ø 00 1E Ø Ø Ø Ø 1F Ø Ø Ø Ø ø Ø ØØ ø Ø Tabel 1. De inhoud van de PROM IC17. Men kan hem door Elektuur (ESS 508) laten

A = R/W

Ø Ø Ø Ø

Ø Ø Ø Ø Ø Ø Ø Ø Ø

1

Ø Ø

Ø Ø Ø Ø Ø Ø Ø Ø Ø

1 Ø Ø Ø Ø Ø Ø Ø Ø

1 Ø

۲8 5 χ

Ø Ø Ø Ø Ø Ø

Ø Ø Ø Ø Ø Ø Ø Ø

Ø 1

> Ø Ø Ø Ø Ø Ø Ø Ø

Ø Ø Ø Ø Ø

Ø Ø

Ø Ø Ø

Ø Ø Ø

Ø

Ø Ø Ø Ø

Ø

Ø Ø Ø

Ø

Ø Ø

Ø Ø Ø Ø

۲I

II C

Ø Ø Ø Ø Ø

Ø 1 Ø

Ø Ø Ø

Ø Ø Ø Ø Ø Ø Ø Ø

Ø 1 Ø Ø

1 Ø Ø

programmeren of dat zelf doen (bijvoorbeeld met behulp van schakeling 97 uit de halfgeleidergids 1980). Andere, pin-kompatibele PROM's zijn op zich bruikbaar (bijvoorbeeld de 74S188), maar kunnen niet worden geprogrammeerd via ESS 508 of met die schakeling 97.

Y2 = READ Y1 = WRITE**PROM-data**

Ø Ø

Ø

Ø

Ø Ø

Ø

0

Ø

Ø

Ø

1

Ø

ø ØØ

Ø

Ø

Ϋ́

Ø

Ø

Ø

Ø

Ø

Ø

Υ5

Ø Ø

Ø Ø ø

Ø Ø Ø

74

ø Ø

> Ø Ø Ø

Ø Ø

Ø Ø (hex)

ØØ

ØЗ

ወወ

ØØ

Ø1

Ø1

ØØ

Ø3

00

ØØ

00

00

Ø1

Ø1

ØØ

ØØ

ØЗ

#### 4-46 -- elektuur april 1981

Lezen van EPROM en lezen of schrijven van RAM of PIA op de basiskaart. Databuffers geblokkeerd ("disabled") (PROM-adressen Ø4 en Ø5).

3. Schrijven of lezen van de VIA. Zit op de interface-kaart, dus acht databuffers staan in de door lezen of schrijven gedikteerde richting (PROMadressen Ø6 en Ø7).

4. Schrijven of lezen van buskaartgeheugen (PROM-adressen ØC en ØD). Omdat, evenals in de gevallen 1...3, E nul is (WITH = WITHOUT), is er kennelijk geen buskaartgeheugen aangesloten; de databuffers *moeten* in dit geval zijn geblokkeerd. De vektoren NMI, RES en IRQ worden automatisch uit de standaard-EPROM van de juniorcomputer gehaald.

Zie 1 (PROM-adressen 10 en 11).

Zie 2 (PROM-adressen 14 en 15).

Zie 3 (PROM-adressen 16 en 17).

8. Voor een deel zie 4 (PROMadressen 1C en 1D). Omdat, evenals in de gevallen 5...7. E "1" is

als in de gevallen 5...7. E "1" is (WITH = WITHOUT), is er kennelijk buskaartgeheugen aangesloten. Nu moeten de databuffers wêl open staan voor dataverkeer in een bepaalde richting. Zoals al opgemerkt: de drie vektoren worden nu uit pagina FF opgehaald. Daar moet EPROM op zijn aangesloten, die op FFFA ... FFFF de drie vektoren specificeert.

We zien dat de helft van de 32 bytes van de PROM IC17 echt nodig is. De andere 16 toestanden zijn onbelangrijk, omdat de overeenkomende kombinaties van  $D = \frac{8K\emptyset}{8K}$ ,  $C = \frac{KX}{K}$  en B = VIAgewoonweg niet voorkomen. Ondanks dat zijn in alle 16 overige gevallen Y1 en Y2 nul. Dat betekent dat de databuffers op schrijven staan ingesteld en dat is volkomen ongevaarlijk. Figuur 1 is nu helemaal besproken. Nu

Figuur 1 is nu helemaal besproken. N figuur 2 nog.

#### Cassette-hardware

Het grootste gedeelte van figuur 2 betreft elektronica ten behoeve van de cassette-interface: alles wat, afgezien van de software (zie een ander artikel in dit nummer) nodig is voor het zenden van data naar de cassette-recorder (schrijven) of het lezen van data van de cassette-recorder. Tijdens het lezen van data wordt data van de band weergegeven, tijdens het schrijven data op de band opgenomen.

De data gaat naar of komt van de 6502-  $\mu$ P via poortlijn PB7 van de poortkonnektor. Tijdens het schrijven van data, dus tijdens de subroutine DUMP/ DUMPT van het systeemprogramma TAPE MANAGEMENT, is PB7 uitgang, net zoals PB5 en PB6. Poort PB5 is dan "0" en PB6 "1". Dat heeft tot gevolg dat de ingang van N38 met pennummer 8 ook laag is en de uitgang van N38 dus hoog (N38 heeft een open-kollektoruitgang, die hoogohmig is als-ie "1" is). Omdat PB5 "0" is wordt via R15 de PNP-darlington T3 opengestuurd, met als gevolg dat de *rode* LED D5

(OUTPUT ON) oplicht en dat relais Re2 is bekrachtigd; de twee kontakten van uitgang J4 zijn met elkaar doorverbonden. Nemen we deze kontakten op in serie met de motor van de opnamerecorder OUTPUT (afstandsbediening), dan kan deze worden gestart via de software (de recorder moet dan wel gereed staan voor opname).

Omdat tijdens het schrijven PB6 "1" is, is T2 gesperd, de groene LED D4 gedoofd, relais Re1 niet bekrachtigd en zijn de kontakten van J3 geopend. De uitgang van N39 voert ons via R20 en C14 naar P2, waarmee het maximale opnamenivo moet worden ingesteld. De data-uitgang is J2.

Tijdens het lezen van data van de band, dus tijdens de subroutine RDTAPE van TAPE MANAGEMENT, is PB7 als ingang geschakeld; ook nu zijn PB5 en PB6 uitgang, Poort PB5 is nu "1" en PB6 "0". Met als gevolg dat N38 het uitgangssignaal van IC7 geïnverteerd aan PB7 kan doorgeven. Poort N39 blijft gewoon doorverbonden. Dat betekent dat er ook signalen terechtkomen op de data-uitgang J2, maar dat kan helemaal geen kwaad. Omdat PB5 "1" is, is de rode LED D5

Omdat PB5 "1" is, is de rode LED D5 gedoofd en zijn de kontakten van J4 geopend. Daarentegen is PB6 nu nul, en dat heeft tot gevolg dat T2 geleidt, de groene LED D4 (INPUT ON) oplicht, relais Re1 bekrachtigd is en dat de kontakten van J3 (afstandsbesturing van de weergave-recorder INPUT) gesloten zijn.

Men is niet verplicht om gescheiden recorders te nemen voor het opbergen en ophalen van data. Bij het gebruik van één recorder voor beide taken vervalt het nut van de beide relais, omdat afstandsbesturing dat niet zo nodig moet. Het kån natuurlijk wèl: een kwestie van doorverbinden van de kontakten van J3 en J4 (*beide* relais moeten aanwezig zijn!).

De sturing van T2 en T3 levert in ieder geval nuttige visuele informatie op over wat men eigenlijk aan het doen is. De groene LED licht op tijdens het lezen van data en de rode LED doet dat tijdens het schrijven van data. De kleurkeuze is logisch; denk aan de rode lampen in opname-studio's en elders, en aan groene verkeerslichten.

Het gedeelte van figuur 2 tussen de data-ingang J1 en de ingang van N38 met pennummer 9 is nu aan bespreking toe. De schakeling rond IC6 en IC7 dus. De KIM-kenners onder u zullen ongetwijfeld bij het zien van dit gedeelte van figuur 2 zeggen: "Hé, waar heb ik dat meer gezien". Klopt. Omdat we van mening zijn dat het geen zin heeft om het wiel opnieuw uit te vinden. Wèl zijn de hoekige kanten van het wiel afgerond. Anders gezegd: het gaat om verbeterde KIM-hardware (zie ook schakeling 31 uit de halfgeleidergids 1980). Voor de bespreking van IC6, IC7 en

voor de bespiering van 100, 107 en omstreken is het voldoende om te weten dat de data op de band staat in de vorm van een reeks van een toontje met een frekwentie van ca. 3600 Hz, afgewisseld door eentje met een frekwentie van ca. 2400 Hz. Dus een tijdje 3600 Hz, daarna een tijdje 2400 Hz, daarna weer 3600 Hz, en daarna weer 2400 Hz, enzovoorts. Bij een bit hoort een 3600 Hz-tijdje en een dito 2400 Hz.

Uit de 3600 Hz-tijdsduur ten opzichte van de 2400 Hz-tijdsduur blijkt dat het bit "1" dan wel "0" is. De schakeling rond IC6 en IC7 zorgt ervoor dat de uitgang van IC7 "1" is als er 3600 Hz op de ingang J1 staat en "0" als er sprake is van 2400 Hz. De software van RDTAPE zorgt ervoor dat uit de twee tijdsduren van een 3600 Hz/2400 Hz-cyclus een bit "0" of "1" wordt gedestilleerd (zie het 2

Figuur 2. Deze schakelingen van de interface-kaart hebben betrekking op het zenden of schrijven van data en het ontvangen of lezen van data ten behoeve van RS232-randapparatuur en cassette-band.

software-artikel elders in dit nummer). De schakeling van IC6 vormt samen met de omringende komponenten een zogenaamde PLL (Phase Locked Loop: fasevergrendelde regellus). Dat klinkt erg "duur" en het is mogelijk om een hele jaargang Elektuur te vullen met formules over dat ding. Neem ons niet kwalijk als we dat niet doen en in plaats daarvan de werking uitleggen in een paar zinnen. Zie de PLL, met name in de toepassing op de interface-kaart als een "frekwentievolger". Net zoals bij een emittervolger de uitgangsspanning de ingangsspanning volgt past een interne oscilla tor zich in de frekwentie aan aan de frekwentie van het ingangssignaal, binnen een zeker frekwentiebereik en boven een minimum-nivo van het ingangssignaal. Die interne oscillator heeft een frekwentie die afhangt van een stuurspanning (VCO). Zonder ingangssignaal is de frekwentie ca. 3000 Hz, dus precies tussen 2400 Hz en 3600 Hz. Staat er 3600 Hz op de ingang, dan gaat de frekwentie met 600 Hz omhoog; bij 2400 Hz op de ingang met 600 Hz omlaag. Voor een verlaging van de frekwentie is een verhoging van de stuurspanning nodig en voor een frekwentieverhoging een verlaging van de stuurspanning. De hoogte van de stuurspanning hangt dus samen met de 4-48 — elektuur april 1981

frekwentie van het ingangssignaal en biedt na vergelijking met een vaste spanning de mogelijkheid om logisch onderscheid te maken tussen frekwenties : "1" voor de ene frekwentie, "0" voor de andere, geheel in overeenstemming met het principe van FSK (Frequency Shift Keying; zeg maar: frekwentieverschuivingslogica). De PLL wordt uit +12 V gevoed via de

parallelschakeling van D2 + D3 en C8. Dit wat merkwaardige netwerk zorgt ervoor dat de PLL via pen 10 behoorlijk verschoond blijft van allerlei stoorspanningen op de voeding, die de werking van de PLL zouden kunnen verstoren. De "schone 12 V" (ca. 11 V vanwege de dioden) wordt eveneens gebruikt voor de gelijkspanningsinstelling van de ingangen (pennen 2 en 3 van IC6) via R21 . . . R24. Bij de KIM wordt daarvoor een 5 V-voedingsspanning gebruikt die vergeven is van stoorspanningen die regelrecht de (weliswaar gebalanceerde) ingangen ingaan. En dat terwijl er daar óók zo'n "schone 12 V" voorhanden is! Verder is er hier, anders dan bij de KIM, geen sprake van een ca. tienvoudige verzwakking van het ingangssignaal voordat pen 2 is bereikt. Alle genoemde verbeteringen hebben tot gevolg dat men van goeden huize moet komen om nu ingangsdata de mist in te laten gaan (bijvoorbeeld door "dropouts" op de band, een vuile of niet goed afgestelde kop, enzovoorts). Het is ons al een paar keer overkomen dat achteraf bleek dat er data werd ingelezen, terwijl een massaverbinding met de recorder ontbrak!

Van de ingangen 2 en 3 (een soort verschilversterkeringang) wordt alleen ingang 2 gebruikt (asymmetrische sturing). De koppeling met J1 gaat via C1, die een veel kleinere waarde heeft dan de KIM teneinde veel meer storing

beneden 2400 Hz buiten de deur te houden. Weerstand R37 is nodig in het geval dat gebruik wordt gemaakt van de luidsprekeruitgang (of koptelefoonuitgang) van een cassette-recorder, waarbij de luidspreker automatisch wordt afgekoppeld.

Van invloed op de VCO-frekwentie zonder ingangssignaal zijn C3, R25 en P1. De metode, volgens welke P1 wordt ingesteld bepaalt in grote mate de kwaliteit en betrouwbaarheid waarmee data wordt gelezen van de band. In boek 3 zullen verschillende metoden worden gegeven voor de juiste instelling/ afregeling van P1.

Punt 7 van IC6 is de uitgang van de

PLL. Deze voert de al eerder behandelde regelspanning die ervoor zorgt dat de VCO-frekwentie in de pas loopt met het ingangssignaal. Dit punt is via C9 ver-bonden met +12 V. Deze kondensator vormt samen met een weerstand van 3K6 in het IC het zogenaamde loopfilter (lusfilter). Dit filter is van groot belang voor het goed, niet al te "emotioneel" (overshoot) reageren van de PLL op frekwentieveranderingen aan de ingang. De uitgang van de PLL gaat via het ladderfilter R26...R28 & C5...C7 naar de min-ingang van de komparator (= vergelijker) IC7. De plus-ingang hiervan ligt via R29 aan een door IC6 geleverde vaste gelijkspanning (op pen.6). De dimensionering van dat ladderfilter hangt samen met de snelheid waarmee 3,6 kHz- en 2,4 kHz-frekwenties de elkaar opvolgen. En dat hangt op zijn beurt weer samen met de snelheid waarmee de bits op de band zijn geschreven, en van de band moeten worden gelezen. Dat is de zogenaamde baudrate, het aantal verzonden of ontvangen bits per sekonde: 800 (baud) voor de junior-cassette-hardware en -software.

We herinneren ons nog wel dat een verhoging van de VCO-frekwentie tot 3600 Hz een verlaging van de uitgangsspanning op punt 7 tot gevolg had (in een gesloten regellus zijn oorzaak en gevolg moeilijk van elkaar te onderscheiden), en een verlaging naar 2400 Hz een verhoging van die spanning. Er van uitgaand dat de gefilterde uitgangsspanning op de min-ingang van IC7 van lager resp. hoger is dan de gelijkspanning op de plus-ingang van IC7, krijgen we de situatie dat de uitgang van IC7 "hoog" is (+5 V, via R31) als de ingangsfrekwentie 3600 Hz is, en "laag" (praktisch op aardpotentiaal) als de ingangsfrekwentie 2400 Hz is. Dat is precies wat

#### junior-hardware kompleet

we nodig hebben. De uitgangsspanning van IC7 wordt via N38 geïnverteerd (hoog wordt laag, en omgekeerd) en op PB7 gezet.

N.B. De PLL reageert niet oneindig snel op veranderingen van de ingangsfrekwentie. Dat heeft tot gevolg dat de uitgang van IC7 niet in één keer omklapt van "1" naar "0" of van "0" naar "1" tijdens de overgang van 3600 Hz naar 2400 Hz respektievelijk van 2400 Hz naar 3600 Hz. Nee, de uitgang fietst een aantal keren heen en weer tussen het ene en het andere nivo alvorens definitief het eindnivo aan te nemen: de zogenaamde PLL-jitter, die erg veel lijkt op kontaktdender van (bijvoorbeeld) toetsen. De software van de subroutine RDTAPE weet echter wel raad met dat tijdelijke wispelturige gedrag.

# Randapparatuur via RS232C

De ter bespreking resterende schakelingen van figuur 2 (linksboven) stellen weinig voor in vergelijking tot de enorme hoeveelheid "moeilijke" elektronica, inklusief science fiction-achtige kreten als "UART", die zit in de randapparatuur, die via de voornoemde simpele schakelingen op de juniorcomputer kan worden aangesloten.

Het gaat om een data-zender en een data-ontvanger. Poort PA7 doet dienst als ingang, PBØ als uitgang. De ontvanger is T1 met wat spul eromheen. Het is belangrijk om vast te stellen dat T1 enen op de ingang (bovenkant R5) omtovert in nullen, en omgekeerd. . Nemen we aan dat ingang 6 van N37 aan +5 V ligt via R8 en vergeten we even wat er via de draadbrug P-Q gebeurt, dan inverteert N37 het ingangsnivo PBØ. De uitgang van N37 stuurt via R10 de vergelijker IC8. Er wordt vergeleken met de spanning op het knooppunt R11/R12/C12, Is de uitgang van N37 "1", dan is de uitgang van IC8 ca. +12 V; in het geval "0" ca. --12 V. Ook nu stellen we vast dat er tussen

$PB\emptyset$  en de uitgang van IC8 – Ios van nivo-aanpassing – sprake is van omkering van logische nivo's.

Data-ingang (via R5) en -uitgang (IC8) zijn aangesloten op een genormaliseerde 25-polige D-konnektor, ook wel RS232konnektor genoemd. Dat "RS232" is niet zo maar een kreet, maar een norm, afspraak voor seriële datakommunikatie: bit voor bit. Elk byte van acht bits wordt voorafgegaan door een startbit, ten teken dat begonnen is met het verzenden van een byte. Bytes zijn gekodeerd volgens de ASCII-kode.

De RS232-norm legt de twee mogelijke logische nivo's vast van een data-kommunikatieleiding, inklusief de bijbehorende spanningsnivo's. Later is daar de pinning van de D-konnektor bijgekomen. Voor een logische nul geldt een lijnnivo tussen +5 V en +15 V (versie RS232C), voor een logische eén een lijnnivo tussen -5 V en -15 V. Bij "ons" is het circa +12 V respektievelijk -12 V. U ziet dat bij een "1" een lage spanning hoort en bij een "0" een hoge; dat noemen ze negatieve logika. Door nu zowel na het ontvangen als voor het zenden data (bits) te inverteren hoeft er in de computer niet met "gespiegelde" data te worden gewerkt.

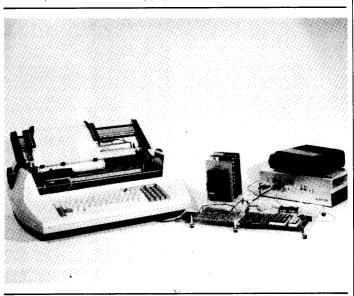

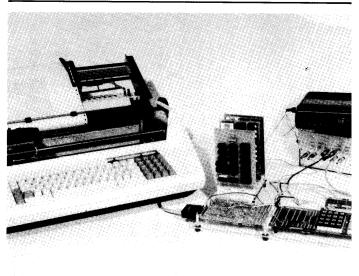

De D-konnektor heeft een aantal pennen die onderling zijn doorverbonden. Andere doorverbindingen zijn mogelijk, afhankelijk van de soort aan te sluiten randapparatuur. Wat is er zo al konkreet aan te sluiten op de juniorcomputer via de RS232-konnektor? We denken met name aan de Elekterminal, een video-terminal, inklusief ASCIItoetsenbord (met de toetsen van een tiepmachine *plus* een aantal speciale toetsen), die is ontworpen in het kader van de SC/MP-computer, maar eveneens uitermate geschikt is voor de juniorcomputer.

Het systeemprogramma PRINTER MONITOR is gebaseerd op het ASCIItoetsenbord als invoer (diverse toetskommando's) en de eigenlijke Elekterminal of een geschikte printer (*niet*, althans voorlopig niet, de eerder door Elektuur gepubliceerde metaalfolie-printer) als uitvoer (display).

Tot zover de beschrijving van de hardware. De aangepaste, zwaardere voeding van de junior-computer is niet besproken, evenals een paar wijzigingen van de basiskaart. Voor deze zaken, alsmede voor een korte bouwbeschrijving – mèt de printen – verwijzen we u naar de Elektuur van de volgende maand. In boek 3a zal e.e.a. nog eens dunnetjes (d.w.z. uitgebreid!) worden overgedaan.

elektuur april 1981 –4-49