# BASIC MICROPROCESSOR APPLICATION SYSTEM MA02/1

EXPERIMENT MANUAL

· .

## CONTENTS

## INTRODUCTION

# SECTION 1

| COMPUTI | ER AR  | ITHMETIC AND NUMBER REPRESENTATION    | abaya . | Pages    |

|---------|--------|---------------------------------------|---------|----------|

| Chapter | 1.1    | Introduction to Digital Technology.   |         | 1 - 9    |

| Chapter | 1.2    | Binary Arithmetic.                    |         | 9 - 18   |

| Chapter | 1.3    | Computer Arithmetic.                  |         | 19 - 25  |

| Chapter | 1.4    | ASCII Codes and Parity.               |         | 26 - 29  |

| Chapter | 1.5    | Octal and Hexadecimal Number Systems. |         | 30 ~ 35  |

| SECTION | 12     |                                       |         |          |

| INTRODU | JCTIO  | N TO MICROCOMPUTERS                   |         |          |

| Chapter | 2.1    | Introduction to the Microprocessor.   |         | 1 - 9    |

| Chapter |        | Microcomputer System Elements.        |         | 10 - 17  |

| Chapter |        | Introduction to Programming.          |         | 18 - 22  |

| Chapter |        | The Intruction Set.                   |         | 23 - 29  |

| SECTION | 1 3    |                                       |         |          |

| PROGRAM | 4M ING | THE EMMA MICROCOMPUTER                |         |          |

| Chapter | 3.1    | Introduction to Emma.                 |         | 1 - 7    |

| Chapter | 3.2    | Program Entry and Execution.          |         | 8 - 15   |

| Chapter | 3.3    | Using 6502 Instructions.              |         | 16 - 25  |

| Chapter | 3.4    | Writing a Program.                    |         | 26 - 41  |

| Chapter | 3.5    | Arithmetic Operations.                |         | 42 - 53  |

| Chapter | 3.6    | Logical Operations.                   |         | 54 - 58  |

| Chapter | 3.7    | Sub-routines.                         |         | 59 - 62  |

| Chapter | 3.8    | Stack Processing.                     |         | 63 - 65  |

| Chapter | 3.9    | Software Delays.                      |         | 66 - 73  |

| Chapter | 3.10   | Interrupts.                           |         | 74 - 87  |

| Chapter | 3.11   | Using the VIA.                        |         | 88 -108  |

| Chapter | 3.12   | Program Debugging.                    |         | 109 -112 |

| Chapter | 3.13   | Using the Cassette Interface.         |         | 113 -114 |

|         |        | a 1                                   |         | MP126/A  |

# APPLICATIONS HARDWARE

| Chapter | 4.1 | Using the Application Hardware. | 1 - 15  |

|---------|-----|---------------------------------|---------|

| Chapter | 4.2 | Further Application Programs.   | 16 - 18 |

# SECTION 5

# APPENDICES

| 1 | Conversion Tables          |        |

|---|----------------------------|--------|

|   | Standard Coding Sheet      | 1 - 3  |

| 2 | Application Modules        | 1 - 11 |

| 3 | Emma Monitor Sub-Routines. | 1 - 9  |

| 4 | Emma Memory Map.           | 1 - 4  |

| 5 | Oscilloscopes.             | 1 - 6  |

| 6 | Instruction Set.           | 1 - 19 |

| 7 | Microcomputer Glossary.    | 1 - 26 |

| 8 | Solutions to Questions.    | 1 - 8  |

# SECTION 1

# COMPUTER ARITHMETIC AND NUMBER REPRESENTATION

| Chapter | 1.1  | Introduction to Digital Technology.  | Pa ge | 1  |

|---------|------|--------------------------------------|-------|----|

| Chapter | 1.2  | Binary Arithmetic                    | Pa ge | 9  |

| Chapter | 1'.3 | Computer Arithmetic                  | Page  | 19 |

| Chapter | 1'.4 | ASII Codes and Parity                | Pa ge | 26 |

| Chapter | 1.5  | Octal and Hexadecimal Number Systems | Pa ge | 30 |

#### INTRODUCTION

The Microprocessor Application Manual provides a course of study based around the L'.J'. ELECTRONICS Basic Microprocessor Application System MAO2 which comprises the following items of equipment:

```

1451

Emma Microcomputer.

MS3

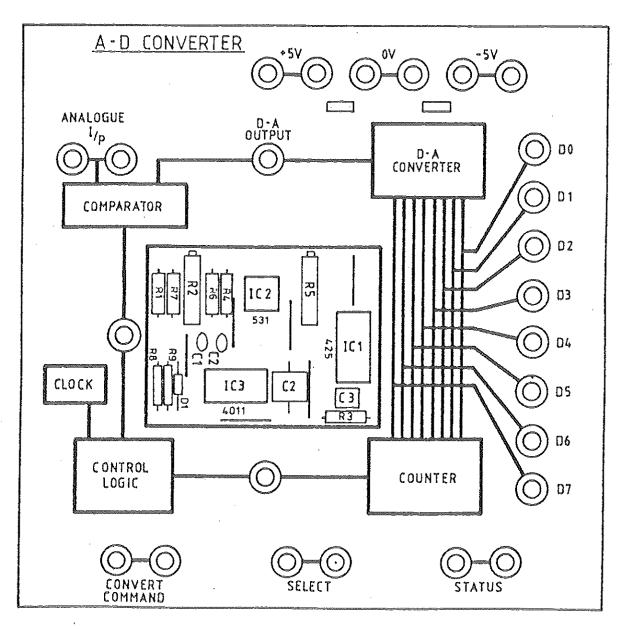

A/D Converter'.

MS5

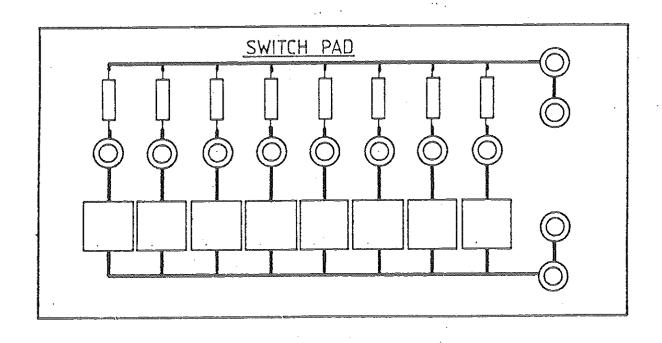

Switch Pad.

MS6

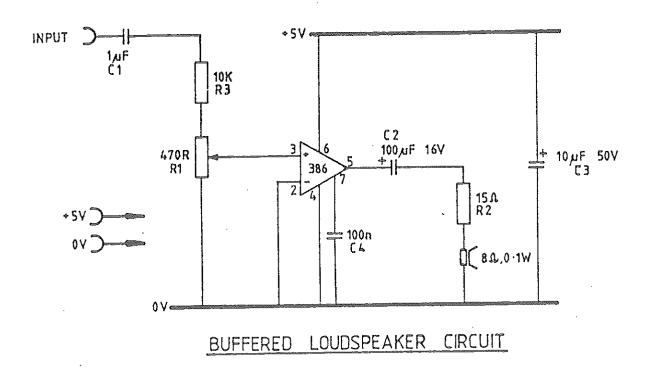

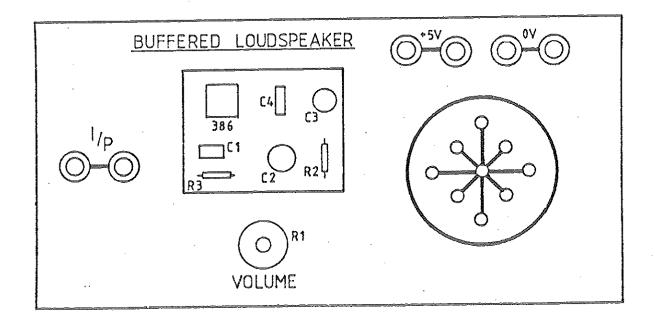

Buffered Loudspeaker.

MS7

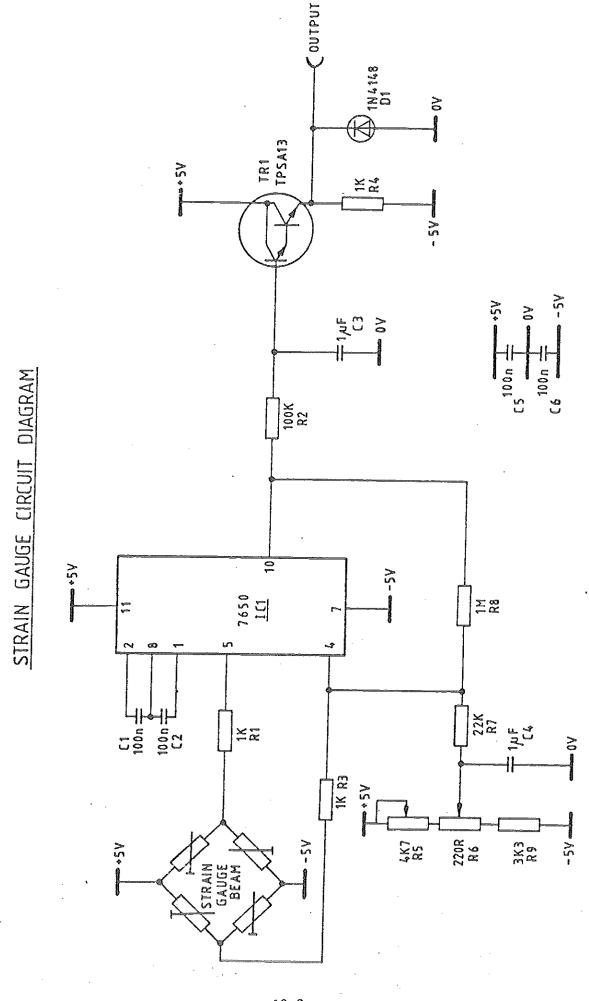

Strain Gauge.

MS12

I/O Port Monitor.

PS4

System Power 90.

HM203

Dual Trace Oscilloscope.

HZ35

x1 Voltage Probe Kit (2 off).

CS1.

Set of 36 x 4mm Leads.

Emma Cassette Interface - DIN Plug Lead'.

CS2

Also required but not part of the set.

CR1

Cassette Recorder - with AUX DIN socket: tape counter and

2 x C12 casettes.

```

This manual considers the EMMA Microcomputer and selected Application hardware Modules to provide an understanding of the basic principles and practice of microprocessors: especially with "Control" applications in mind. It is primarily intended to introduce EMMA (The Microcomputer) which forms the central element of the L.J. ELECTRONICS Microprocessor Teaching System.

A basic understanding is gained through graded examples and exercises using low-level programming techniques - both machine code and assembly language. To explore the considerable capabilities of the microprocessor more fully: a selection of peripheral items are introduced: and used in conjunction with EMMA: to form an integrated working control system.

The oscilloscope: while not necessarily forming an essential part of a particular application: is used to permit the examination of waveforms and so serves as an early introduction to system fault diagnosis. It also enhances the understanding of system operation.

Programs of even the most ingenious and meticulous programmers do not always function the first time. To cater for such possibilities the program debug feature of the EMPIA Microcomputer is introduced.

To expedite the saving of programs: the use of a Cassette recorder is considered. Program "dumping" is an important aspect and this facility utilises the EMMA on-board cassette interface.

Numerous examples are used and exercises set to facilitate the learning process. To obtain maximum benefit it is strongly suggested that these be systematically and methodically worked through. Solutions to the exercises are published in a separate manual: reference number MP101. However a set of self-test questions are provided at the end of each Chapter with solutions given in Appendix 9.

Having completed the course of study detailed in this manual L.J. ELECTRONICS provide a wide range of equipment for more advanced studies: these include:

- More complex Application Hardware Modules.

- VISA expansion unit providing ASSEMBLY and BASIC language programming.

- Memory Expansion/EPROM Programming module.

- Floppy Disc System.

- Test and Fault Diagnosis equipment.

- Robotics equipment.

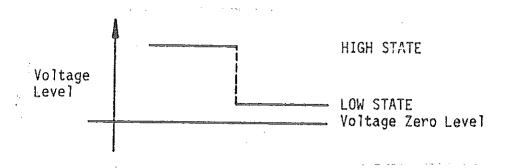

#### LOGIC STATES

The inputs and outputs of digital devices are represented by two discrete voltage levels or states which are often referred to as either "high" or "low" with respect to each other.

We also refer to the high state as a "logical one" (1) and the low state as a "logical zero" (0). Since these devices are used to implement logical functions, we use the term "Binary Logic" to describe them. This is the technology of information processing.

#### **ELECTRONIC REPRESENTATION OF INFORMATION**

Information (data) is encoded using a binary format for processing purposes, the smallest unit being the binary digit or **Bit**. A number of bits are grouped together and the resulting sequence of 1's and 0's made to represent a unique piece of digitally or binary encoded data. A typical bit sequence would be

1010 1110

8 bits are used to encode the data item.

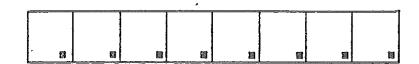

For machine processing the number of bits grouped together is usualy fixed and such a group is termed a **word**. A **word** can therefore represent any fixed length of bits but it is normal to find standard word lengths of 8, 16 and 32 bits, especially in computing systems. We also define a word length of 8-bits as a **byte** and a **nibble** as being a group of 4-bits. The term byte is used extensively in the field of micro-processing.

#### MICROCOMPUTER DATA REPRESENTATION

The way in which data is represented in computer systems depends upon who or what is going to use the encoded information. We have already seen that "machines" require data presented in a binary format, however to the user of such machines this presentation is by no means convenient. We therefore encode data according to whether it will be used internally (within the machine) or externally (by the machine programmer). We will deal with these two aspects separately:

#### MICROCOMPUTER INTERNAL DATA REPRESENTATION

Computer systems operate to a strict sequential list of instructions called a **Program**. This is written by a Computer Programmer and designed to manipulate data. The program will be stored within the system memory and will perform operations upon data either stored within the system or obtainable as required from system peripherals\*.

\*See Glossary of Terms

Both the program, and the data upon which it operates, will need to be encoded into a binary format for use by the machine. We can, however, identify two distinct data groups which will require representation - Numeric Data and Alphanumeric Data. We will briefly outline these and then look at them in some detail.

**Numeric Data** is used to quantify things, for example, how many of these or those do we have. We then try to process this data by means of arithmetic or logical operations.

Computer systems excel at this type of processing; they are able to perform data processing operations both quickly and accurately. However, numbers must be represented on computer based systems in such a way that the arithmetic can be performed both easily and accurately.

We will examine the way in which numbers that require arithmetic operations are represented and how the arithmetic is performed later.

Alphanumeric Data comprises characters such as all the letters of the alphabet (both upper and lower case), numeric symbols, 0 through to 9, together with additional special symbols, such as question marks, quotes and brackets. We can easily accommodate these within 7-bits which allow for 128 possible codes. As you may imagine, standard codes have been devised but by far the most common for use in microprocessors is termed ASCII (pronounced Ask-ee) Code. ASCII stands for "American Standard Code for Information Interchange".

We will examine ASCII Code in some detail later.

## MICROCOMPUTER EXTERNAL DATA REPRESENTATION

Much of the data input to a computer system is generated by human beings, also much of its output is frequently used by them. We can identify three formats which are suitable for computer user presentation - Binary, Octal or Hexadecimal and Symbolic.

We will deal with these in detail later.

Now let us consider in detail the whole problem of data representation and its manipulation.

#### DATA REPRESENTATION AND MANIPULATION

Various representations are in use and different methods of manipulation are available to us. All have advantages and disadvantages. In general, the designer is faced with a compromise situation and hence no two designs are exactly the same. However, it is our intention, throughout the rest of this section to provide you, the reader, with a few tools which will help you better understand the technology of microprocessors and their application.

**Direct Binary** is used to encode integers or whole numbers. Let's consider a sequence of 8-bits or a single byte. Each bit is numbered 0 through to 7.

$${}^{\mathrm{B}}{}_{7}\ {}^{\mathrm{B}}{}_{6}\ {}^{\mathrm{B}}{}_{5}\ {}^{\mathrm{B}}{}_{4}\ {}^{\mathrm{B}}{}_{3}\ {}^{\mathrm{B}}{}_{2}\ {}^{\mathrm{B}}{}_{1}\ {}^{\mathrm{B}}{}_{0}$$

In any number system the digit position carries a "weighting" and the binary system is no exception to this. For example, the eighth bit (bit 7) has a greater significance than the first bit (bit 0). We refer to these particular bits as the most significant bit (MSB) and least significant bit (LSB), respectively. The weighting represented by the bit position is evaluated by raising the number system base (2 for binary) to a power indicated by the bit position, e.g.:

| BIT      | BIT       | DENARY     |

|----------|-----------|------------|

| POSITION | WEIGHTING | EQUIVALENT |

| 0        | 20        | 1          |

| 1        | 21        | 2          |

| 2        | 22        | 4          |

| 3        | 23        | 8          |

If you evaluate the weighting of the remaining bit positions  $(B_4 - B_7)$ you should find them to be 16, 32, 64 and 128 respectively. We are now in a position to decode any direct binary number into its denary equivalent.

#### **EXAMPLE:**

Decode the following single byte direct binary encoded number into its denary equivalent: Binary Number 0110 1101

We will solve by tabulation:

| BIT<br>POSITION             | BINARY<br>VALUE                 | DENARY<br>WEIGHTING                                                                                                     | DENARY<br>YALUE                                                                                                                                                              |       |                                   |  |

|-----------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------|--|

| 0 (LSB) 1 2 3 4 5 6 7 (MSB) | 1<br>0<br>1<br>1<br>0<br>1<br>1 | 2 <sup>0</sup> 2 <sup>1</sup> 2 <sup>2</sup> 2 <sup>3</sup> 2 <sup>4</sup> 2 <sup>5</sup> 2 <sup>6</sup> 2 <sup>7</sup> | 1 x 2 <sup>0</sup><br>0 x 2 <sup>1</sup><br>1 x 2 <sup>2</sup><br>1 x 2 <sup>3</sup><br>0 x 2 <sup>4</sup><br>1 x 2 <sup>5</sup><br>1 x 2 <sup>6</sup><br>0 x 2 <sup>7</sup> |       | 1<br>0<br>4<br>8<br>0<br>32<br>64 |  |

|                             | L.,                             | L 19-20-1-1-1                                                                                                           | Total D                                                                                                                                                                      | enary | 109                               |  |

The denary equivalent of binary 0110 1101 is therefore 109.

#### EXERCISE 1.1.1

Decode the following direct binary numbers into their denary equivalents:

#### EXERCISE 1.2.2

Determine the maximum denary whole number that can be encoded by:

- Q1. A Nibble

- Q2. A Byte

We will now encode a denary whole number in direct binary format. An example is probably the best way of doing this.

#### EXAMPLE:

Encode denary 124 into direct binary. We proceed by dividing our denary number by 2 and then successively dividing resultant quotients until zero is obtained. For example:

| DIVIDEND                        | DIVISOR                              | QUOTIENT        | REMA I NDER                | BINARY<br>DIGIT               |

|---------------------------------|--------------------------------------|-----------------|----------------------------|-------------------------------|

| 124<br>62<br>31<br>15<br>7<br>3 | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 62' 31 15 7 3 1 | 0<br>0<br>1<br>1<br>1<br>1 | 0 (LSB) 0 1 1 1 1 1 1 1 (MSB) |

You should notice that 7 bits were required and that the binary equivalent of 124 is 111 1100. Since machines operate on a fixed number of bits, denary 124 would be represented in a single byte as 0111 1100.

##

Encode the following denary whole numbers into their direct binary, single byte equivalent.

## QUESTIONS

- 1. Define a bit.

- 2. Define a byte.

- 3. What is alphanumeric data?

- 4. What is the denary equivalent of bit 5  $(B_5)$  in an eight binary word.

- 5. Convert the following direct binary numbers into their denary equivalents.

- (a) 1101 (b) 0011 1001 (c) 1111 0000

- 6. Convert the following denary numbers into their direct binary equivalents.

- (a) 38 (b) 120 (c) 201

#### **OBJECTIVES OF THE CHAPTER**

Having studied this chapter you should:

- Be able to perform simple binary addition and subtraction.

- Understand the concept of signed binary numbers.

- Be able to calculate the two's complement of a negative binary number.

- Be able to perform binary subtraction by two's complement addition.

#### BINARY ARITHMETIC

We will now address ourselves to performing simple computations on direct binary numbers.

**Binary Arithmetic** is carried out according to simple rules. The rules for addition are:

#### EXAMPLE:

Using these rules we will add together two 4-bit direct binary coded numbers:

1001

Plus 0101

1110 RESULT

1 CARRIES

You may like to check this by using denary equivalents'.

#### FURTHER EXAMPLE:

Perform an addition on the following 8-bit direct binary coded numbers:

0100 1111 and 0101 1100

now:

Plus 0100 1111 0100 1010 1011 RESULT 1 11 1 CARRIES

Again check using denary equivalents. You will notice the method is exactly the same as when using denary numbers.

#### ● EXERCISE 1.2.1

Compute the SUM of the following pairs of direct binary numbers:

- Q1'. 0110 and 1001

- Q2'. 0101 and 1001

- Q3'. 0100 1001 and 1000 1000

- Q4'. 0011 1000 and 0110 1111

As with addition, so with subtraction; the rules are:

The Borrow is taken from adjacent more significant column.

#### EXAMPLE:

Subtract 0101 from 1001

1001

Minus 0101

0100 RESULT

1 BORROWS

Again you should check using denary equivalents.

#### EXERCISE 1.2.2

Convert the following denary numbers to direct binary and then perform the subtraction:

Q1.

$$(6-3)$$

Q2.  $(12-5)$  Q3.  $(24-18)$

Signed Binary allows us to represent both positive and negative numbers, that is numbers which have both magnitude and sign. You may already have noticed that the numbers we have been operating upon are both small (a maximum of 255 for denary numbers encoded in 8 bits of direct binary) and positively signed.

Let us consider the problem of "signing" our binary numbers. Clearly we have to encode our "sign" (+ or -) using the binary symbols 0 and 1 since these are the only ones available to us. Conventionally, we assign the

left-most bit to providing the "sign" and the rest of the bits to the "magnitude" of our encoded number. Thus in **signed binary** notation the format is:

sign MSB ---- LSB

$$B_7$$

$B_6$  ---  $B_0$

If the sign bit is "0" then positive sign is denoted, and if the sign bit is "1" then negative sign is denoted. For example:

| SIGNED    | SIGN | MAGNITUDE | DENARY     |

|-----------|------|-----------|------------|

|           | BIT  | BITS      | EQUIVALENT |

| 0110 1001 | 0    | 110 1001  | + 105      |

| 1110 1001 |      | 110 1001  | - 105      |

If you compute the values of signed binary 0111 1111 and 1111 1111 you will notice that our range of numbers is now from  $\pm 127$  through zero to  $\pm 127$  as against 0 through to 255 in direct binary.

#### EXERCISE 1.2.3

Determine the denary representation of the following signed binary numbers:

#### EXERCISE 1.2.4

Encode the following denary numbers in signed binary format:

We sometimes use the term **sign-magnitude** for this representation and we will use it to perform simple addition on the denary numbers +6 and -4:

- +6 is represented by 0000 0110

- -4 is represented by 1000 0100

1000 1010 RESULT

Decoded our Sum is -10, clearly this is incorrect and should be +2. We must look for another method of representation if computations of this nature are to take place.

The solution to our problem lies in a representation called two's complement.

Two's Complement provides correct results when performing binary arithmetic computations, but first let us consider an intermediate step - one's complement. In this representation, all POSITIVE whole numbers are represented in signed binary format, thus +4 is 0000 0100 as usual, however its complement (-4) is represented by 1111 1011 and not 1000 0100 as it is in signed binary.

We obtained the **one's complement** by changing all 1's to 0's and all the 0's to 1's for example:

+4 is represented by: 0000 0100

-4 is represented by: 1111 1011

You will notice that the left-most bit can still be reserved to indicate the sign (O for positive and 1 for negative).

If we perform simply arithmetic processes of addition and subtration using this method we will find that the method does not always work. However, this method is used in large computers together with suitable tests, and corrections are carried out if necessary. Two's complement has evolved from this representation - it does work and is used almost exclusively in microcomputer based systems.

In two's complement representation positive numbers are still represented as for signed binary, but negative numbers are encoded in two's complement notation. Let's consider the signed denary number +5. In two's complement +5 is represented as 0000 0101:

Its complement (-5) is obtained by first obtaining the one's complement and then adding 1 to it, for example:

Where the RESULT is the two's complement of +5 or, we may say, the RESULT is -5 represented in two's complement notation.

#### To summarise:

+5 is represented by 0000 0101

-5 is represented by 1111 1011 in two's complement notation

You should notice that the left-most bit is still 0 for positive and 1 for negative numbers.

We will now check our method and assure ourselves that it does indeed function correctly. To do this we will perform a number of arithmetic operations.

#### Add +5 to +3:

RESULT CORRECT

Subtract +5 from +3:

We can do this in either of two ways:

a) Using rules of binary subtraction given on page 1.8

$$+3$$

0000 0011

(Subtract)  $+5$  0000 0101

1111 1110 RESULT

1 1111 1 BORROWS

The result is obviously negative since the bit  $(B_7)$  is set to 1. If we cannot easily recognise the magnitude (since it is in two's complement notation) as 2 we can perform a two's complement to find its positive equivalent.

For example:

The result 1111 1110 is thus -2 in two's complement notation. The RESULT is CORRECT.

Now let's do the computation the second way. This time we will change the sign of the (+5) and ADD rather than subtract.

The +5 must now be two's complemented to give -5.

$$^{+5}$$

0000 0101

1's complement 1111 1010

Add 1 1111 1011

now for the computation:

The RESULT is the same as before.

YOU WILL SEE LATER THAT THIS IS AN IMPORTANT FINDING.

#### Add -5 to +3:

Again we must represent the negative denary number (-5) in two's complement and perform an addition.

now for the computation:

Clearly the RESULT is negative. Performing a two's complement on 1111 1110 to find the magnitude will indicate a value of -2.

The RESULT is CORRECT.

#### Subtract -5 from +3

Again we will represent -5 in two's complement which (from previous example) is 1111 1011 and perform the subtraction:

You will notice that to perform our computation we required an EXTERNAL BORROW; that is, we borrowed externally to our 8-bits. If we now ignore this borrow the RESULT (0000 1000 which is +8) is CORRECT.

Now let's perform the computation a different way. Instead of performing a subtraction we will perform a two's complement on (-5) and ADD.

-5 is 1111 1011 in two's complement notation Complement 0000 0100 Add 1

$$\frac{1}{0000\ 0101}$$

2's complement of -5

Now ADD +3 (0000 0011) and the two's complement of -5 which is +5 (0000 0101):

The RESULT is the same, i.e. +8 and is CORRECT.

#### Add -5 to -3:

We have now generated an EXTERNAL CARRY. If we ignore this the result (1111 1000 which is -8) is CORRECT.

#### Subtract -5 from -3:

Rather than subtract directly we will ADD the two's complement of -5 (+5) to -3.

Again we have generated an EXTERNAL CARRY and again if we ignore it the result is CORRECT.

You should now be convinced that representing negative numbers in two's complement does enable us to perform computations using the rules of binary arithmetic addition only and still get correct results in terms of both sign and matnitude.

Now let's have some practice!

#### EXERCISE 1.2.5

Using normal binary arithmetic rules and two's complement to represent negative numbers, perform the following computations after having encoded each number into 8-bits.

In this chapter we have restricted ourselves to small numbers, in the next chapter we will investigate the consequences of using larger numbers for our computation.

#### QUESTIONS

- 1. Perform the following binary operations:

- (a) 1001 + 0101

- (b) 0011 + 0101

- (c) 1111 0101

- (d) 1001 0111

- 2. What is the range of values (in denary) for an 8-bit signed binary number.

- 3. What is the two's-complement of -38.

- 4. Perform the following subtraction using two's complement addition. 47 + (-22).

#### OBJECTIVES OF THIS CHAPTER

Having studied this chapter you should:

- Understand the use of CARRY AND OVERFLOW flags in microcomputers.

- Be able to determine whether or not these flags will be set as the result of a calculation.

- Understand the use of multiple precision arithmetic.

The numbers you have been using in previous exercises were deliberately chosen small. We must now ask ourselves what would happen if larger ones were used.

Let's try adding together +127 and say +6

+127 0111 1111

+ 6 <u>0000 0110</u> 1000 0101 RESULT

The answer appears to be (-5). Clearly this is INCORRECT.

Have we discovered a flaw in two's complement notation arithmetic?

Not really. The problem lies in the fact that although the magnitude of the individual numbers could be encoded in seven bits the result of the computation required eight bits. The result was a CARRY between bit 6 and bit 7 (sign bit) which corrupted both the magnitude and the sign. You may be interested to treat all 8-bits as magnitude and decode as such. The result would then be correct (+133).

Technically an **OVERFLOW** has occurred due to the internal carry. Problems of this nature must be taken care of in any computing system.

#### Let us recapitulate:

- So-far all computations have been performed using a total of 8-bits to encode both sign and magnitude.

- A tacit assumption has been made that a ninth bit has been available for both external BORROWS and CARRIES, indeed we even ignored them when decoding our results.

- We have discovered that subtractions can be performed using COMPLEMENT and ADD methods. We therefore only need the ability to ADD and not both add and subtract

Carries and Overflows are an important concept and must be considered in some detail.

The majority of microprocessors use a fixed bit length of 8-bits (one byte). They also provide a separate bit for use of the external carry. We will adopt this format and perform a number of additions specifically to explore the concept of OVERFLOW.

Our computations are tabulated overleaf:

| DENARY    | BINARY                                     |         |           | RESULT  | BIT    |                |                  |

|-----------|--------------------------------------------|---------|-----------|---------|--------|----------------|------------------|

| NUMBERS   | NUMBER                                     | NUMBERS |           |         | MOV    | EMENT          |                  |

|           | CARRY                                      | SIGN    | MAGNITUDE |         | С      | S              | <sup>B</sup> 6   |

| + 3       |                                            | 0       | 000 0011  |         |        | Wild William   |                  |

| + 5       |                                            | 0       | 000 0101  |         |        |                |                  |

| . 0       |                                            | 0       | 000 1000  | CORRECT |        |                |                  |

|           | 0                                          |         |           |         | ΝО     | NE             |                  |

|           |                                            |         |           |         |        |                |                  |

| +127      |                                            | 0       | 111 1111  |         |        |                |                  |

| + 1       |                                            | 0       | 000 0001  |         | į      | <b>3</b> April | 0                |

|           |                                            | 1       | 000 0000  | ERROR   |        |                |                  |

|           | 0                                          | 1       | 111 111   |         |        |                |                  |

| ÷ 8       |                                            | 0       | 000 1000  |         |        |                |                  |

| - 2       |                                            | 1       | 111 1110  |         |        | 0 🧇            | •                |

| ь         |                                            | 0       | 000 0110  | CORRECT | 9 4    | •              |                  |

|           | 1                                          | 1       | 111       |         |        |                |                  |

|           | 78. 12. 101. 101. 101. 101. 101. 101. 101. |         |           |         | 34     |                | Arcestanium Emir |

| + 2       |                                            | 0       | 000 0010  | ·       |        |                |                  |

| - 8       |                                            | 1       | 111 1000  |         |        |                |                  |

|           |                                            | 1       | 111 1010  | CORRECT |        |                |                  |

|           | 0                                          |         |           |         | N O    | NE             |                  |

| - 2       |                                            | 1       | 111 1110  |         |        |                |                  |

| - 8       |                                            | 1       | 111 1000  |         |        | 0 4=           | •                |

| _         |                                            |         | 111 0110  | CORRECT | A 4000 | . 6            |                  |

|           | 1.                                         | 1       | 111       |         |        | , <b>-</b>     |                  |

| - Company |                                            |         |           |         |        |                |                  |

| -128      |                                            | 1       | 000 0000  |         |        |                |                  |

| - 1       |                                            | 1       | 111 1111  |         |        |                |                  |

|           |                                            | 0 .     | 111 1111  | ERROR   | , opos | ¥              |                  |

|           | 1                                          |         | :         |         |        |                |                  |

|           |                                            |         |           |         |        |                |                  |

Note

Arithmetic Notation - Two's Complement

Abbreviations: C = Carry Bit

S = Sign Bit

$B_6$  = Most significant Bit of Number

• ← • = Bit Movement

If we examine the table we will notice that ERRORS occurred when results exceeded +127 and -128. Obviously such results require more than our allotted 8-bits. OVERFLOW is said to have occurred.

If we now examine the bit movement, we will find that an OVERFLOW occurs only when there is a bit movement from

Sign Bit → Carry Bit.

If both bit movements occur for the same computation OVERFLOW has  $\underline{\mathsf{not}}$  happened.

We have already stated that computation in microprocessors is performed in 8-bit registers with a 1-bit device for the external carry. An additional bit may also be provided to automatically indicate an overflow condition. We term these separate bits, STATUS FLAGS.

#### EXERCISE 1.3.1

Let us assume we have 8-bit registers for computation purposes and two status flags, carry (c) and overflow (v). These flags will be set (contents made equal to logical '1') when carries or overflow occur. Perform the following computations and hence determine the status of the two flags and state whether overflow has occurred.

| Q.1 | 1101 | 1001 | Q.2       | 0110 | 1010 |

|-----|------|------|-----------|------|------|

| Add | 0111 | 1111 | Subtract  | 1010 | 1111 |

| Q.3 | 0100 | 1111 | Q.4       | 1001 | 0000 |

| Add | 1100 | 0001 | Sub tract | 1101 | 0000 |

All our computations have been performed in a fixed number of bits. It is easier for a machine to perform arithmetic calculations if this is so rather than have a variable bit length. If the number of bits are fixed we refer to this as being FIXED FORMAT.

Fixed format does present problems in as far as the range of numbers that can be accommodated (without special provision) is also fixed. Using Two's Complement representation for negative numbers then the range for an 8-bit register is +127 and -128. Clearly this is insufficient for many applications. We will now address this problem.

Multiple Precision Arithmetic is a method which involves using a two or more byte format to accommodate the required magnitude. If two bytes were sufficient we would use a high byte and a low byte thereby effectively giving us a 16-bit DOUBLE-PRECISION format.

High byte Low byte 8-Bits 8-Bits

A number would be "stored" as:

| NUMBER | FORMAT    |           |

|--------|-----------|-----------|

|        | High Byte | Low Byte  |

| 0      | 0000 0000 | 0000 0000 |

| 1      | 0000 0000 | 0000 0001 |

| -1     | 1111 1111 | 1111 1111 |

| 32767  | 0111 1111 | 1111 1111 |

The sign bit is still the left most bit.

A computation would be performed as below:

| NUMBER       | HIGH BYTE | LOW BYTE COMMENT                     |

|--------------|-----------|--------------------------------------|

| -1<br>+32767 | 1111 1111 | 1111 1111<br>1111 1111               |

| +32766       |           | 1111 1110 RESULT<br>1111 111 CARRIES |

Two other formats are also used. These are Binary Coded Decimal (BCD) and Floating point. However, we will not touch on these at this stage, only to say that BCD gives absolutely accurate results but uses a large amount of memory. It is normally used for accounting purposes. Floating point extends the capacity for handling large numbers beyond that of the fixed format. It also generally makes for ease of programming.

In general it would be true to say that these later two formats are more usefully employed in data processing rather than in control applications for which the microprocessor is admirably suitable.

In the next chapter we will investigate a means of encoding alphabetic as well as numeric characters into a digital format suitable for microcomputers.

## QUESTIONS

- 1. When does an overflow occur.

- 2. Determine whether or not the CARRY and OVERFLOW flags will be set by the following calculations.

- (a) 120 25

- (b 83 + 52

- (c) 8 23

- Use double precision arithmetic to perform the following binary calculations.

- (a) 32767 255

#### ASCII CODES AND PARITY

CHAPTER 1.4

#### OBJECTIVES OF THIS CHAPTER

Having studied this chapter you should:

- Be familiar with the use of ASCII codes to represent alphamuneric characters.

- Be able to deduce the ASCII code, for any particular character, from the table given.

- Understand the use of parity bits as an aid to error detection.

ASCII Codes we have already mentioned. They arise because we need to encode alphanumeric data or characters. 7-bits are sufficient for this purpose, but 8-bits will probably be available. This eighth bit is sometimes used as a PARITY bit and helps us to perform a check to see whether data has been corrupted during transmission especially when this takes place between a peripheral outstation and its centrally situated microcomputer. There are two methods of implementing a parity check. The parity bit (bit 7) may be set to make up an even sum of all bits, in which case it is referred to as EVENS PARITY or set to make up an odd sum to give ODDS PARITY.

#### EXAMPLE:

1110 0111 EVENS PARITY

1110 0110 ODDS PARITY

The parity bit is the left most bit.

$\ensuremath{\mathsf{ASCII}}$  is a standard coding system and perhaps a table is the best way of expressing it.

## ASCII CODES

|      |    |   |   |   |     |                | COLUMNS |   |   |    |   |    |     |   |     |

|------|----|---|---|---|-----|----------------|---------|---|---|----|---|----|-----|---|-----|

|      |    |   |   |   |     |                |         | 0 | 1 | 2  | 3 | 4  | 5   | 6 | 7   |

|      |    |   |   |   |     | <sup>B</sup> 6 |         | 0 | 0 | 0  | 0 | 1  | 1   | 1 | 1   |

|      |    |   |   |   |     | B <sub>5</sub> |         | 0 | 0 | 1  | 1 | 0  | 0   | 1 | 1   |

|      |    |   |   |   |     | B <sub>4</sub> |         | 0 | 1 | 0  | 1 | 0  | 1   | 0 | 1   |

| ,    |    |   |   |   |     |                |         |   |   |    |   |    |     |   |     |

|      |    |   |   |   |     |                |         |   |   |    |   |    |     |   |     |

|      | 0  | 0 | 0 | 0 | 0   |                |         |   |   | SP | 0 |    | Р   |   | Р   |

|      | 1  | 0 | 0 | 0 | 1   |                |         |   |   | İ  | 1 | Α  | Q   | a | q   |

|      | 2  | 0 | 0 | 1 | 0   |                |         |   |   | II | 2 | В  | R   | b | r   |

|      | 3  | 0 | 0 | 1 | 1   |                |         |   |   | £  | 3 | C  | S   | С | s   |

|      |    |   |   |   |     |                |         | • |   |    |   |    |     |   |     |

|      | 4  | 0 | 1 | 0 | 0   |                |         |   |   | \$ | 4 | D  | T   | đ | t   |

|      | 5  | 0 | 1 | 0 | 1   |                |         |   |   | %  | 5 | E  | U   | e | u   |

|      | 6  | 0 | 1 | 1 | 0   |                |         |   |   | &  | 6 | F  | V   | f | ٧   |

|      | 7  | 0 | 1 | 1 | . 1 |                |         |   |   | :  | 7 | G  | W   | g | W   |

| ROWS |    |   |   |   | _   |                |         |   |   |    |   |    |     |   |     |

|      | 8  | 1 | • | 0 | 0   |                |         |   |   | (  | 8 | Н  | Χ   | h | Х   |

|      | 9  | 1 | 0 | 0 | 1   |                |         |   |   | )  | 9 | I. | Υ   | i | У   |

|      | 10 | 1 | 0 | 1 | 0   |                |         |   |   | *  | : | J  | Z   | j | Z   |

|      | 11 | 1 | 0 | 1 | 1   |                |         |   |   | +  | ; | K  |     | k |     |

|      | 12 | 1 | 1 | 0 | 0   |                |         |   |   | ŧ  |   | L  |     | 1 |     |

|      | 13 | 1 | 1 | 0 | 1   | _              |         |   |   | .= |   | М  |     | m | Б   |

| -    | 14 | 1 | 1 | 1 | 0   | =              |         |   |   | 0  |   | N  |     | n |     |

|      | 15 | 1 | 1 | 1 | 1   |                |         |   |   | /  | ? | 0  | . = | 0 | DEL |

|      |    |   |   |   |     |                |         |   |   |    |   |    |     |   |     |

$^{\mathsf{B}}_{\mathsf{3}}$   $^{\mathsf{B}}_{\mathsf{2}}$   $^{\mathsf{B}}_{\mathsf{1}}$   $^{\mathsf{B}}_{\mathsf{0}}$

If you now consider the table you should notice the following:

- The seven bit code (no parity) is represented by  $B_0$   $B_6$ . Bit six being the most significant.

- The first four bits (BO B3) appear in the left-hand vertical column while the last three bits (B4 B7) appear in the top three horizontal rows.

- The basic principle of the table is that it is conceived in binary form which makes it very suitable for processing information by computer.

- Direct binary codes 0000 0000 through to 0001 1111 (Denary 0 32) are devoted to control codes for data communication equipment. We have not specified these here.

- Bit zero through to bit three (BO B3) encode in direct binary the numerals O through to 9.

An example in finding an ASCII code for a given character is:

Find the ASCII code for the character, numeral 5.

Follow through the shading on the table. This will give us the ASCII code required. Reading both columns and rows will give:

| COLUMN 3                                           | ROW 5                                                                  |  |  |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <sup>B</sup> 6 <sup>B</sup> 5 <sup>B</sup> 4 0 1 1 | B <sub>3</sub> B <sub>2</sub> B <sub>1</sub> B <sub>0</sub><br>0 1 0 1 |  |  |  |  |  |  |  |

Therefore the ASCII Code for Numeral 5 is 011 0101.

If a parity bit is to be used then:

0011 0101 (EVEN) 1011 0101 (ODD)

|                                                                    | EXER(  | CISE 1.4         | 1.1     |          |       |       |         |        |         |        |      |       |

|--------------------------------------------------------------------|--------|------------------|---------|----------|-------|-------|---------|--------|---------|--------|------|-------|

| Q1.                                                                | Deter  | mine th          | ne ASC  | II codes | for   | the   | follow  | ing Al | phanume | ric Ch | arac | ters: |

|                                                                    | a )    | 9                | b)      |          | c)    | Z     |         | •      |         |        |      |       |

|                                                                    | d)     | А                | e)      | a        | f)    | ?     |         |        |         |        |      |       |

|                                                                    |        |                  |         |          |       |       |         |        |         |        |      |       |

| Q2.                                                                | Assig  | n the p          | parity  | bit for  | each  | of    | the cod | des de | termine | d in Q | 1. 1 | or    |

|                                                                    | Even   | Parity           | and 0   | dd Parit | λ•.   |       |         |        |         |        |      |       |

|                                                                    | _      |                  |         |          |       |       |         |        |         |        |      |       |

|                                                                    |        |                  |         | ed ourse |       |       |         |        |         |        |      | he    |

| machine. In the next chapter we will address ourselves to EXTERNAL |        |                  |         |          |       |       |         |        |         |        |      |       |

| representation.                                                    |        |                  |         |          |       |       |         |        |         |        |      |       |

|                                                                    |        |                  |         |          |       |       |         |        |         |        |      |       |

| QUESTIONS                                                          |        |                  |         |          |       |       |         |        |         |        |      |       |

| •                                                                  |        |                  |         |          |       |       |         |        |         |        |      |       |

| 1.                                                                 | What d | oes ASC          | II sta  | and for? |       |       |         |        |         |        |      |       |

|                                                                    |        |                  |         |          |       |       |         |        |         |        |      | •     |

| 2.                                                                 | Determ | ine the          | ASC I I | codes    | for:  |       |         |        |         |        |      |       |

|                                                                    |        |                  |         |          |       |       |         |        |         |        |      |       |

|                                                                    | (a)    | Q                |         |          |       |       |         |        |         |        |      |       |

|                                                                    | (b)    | 3                |         |          |       |       |         |        | ,       |        |      |       |

|                                                                    | (5)    | O                |         |          |       |       | -       |        |         |        |      |       |

|                                                                    | (c)    | o <del>ļ</del> a |         |          |       |       |         |        |         |        |      |       |

|                                                                    |        |                  |         |          |       |       |         |        |         |        |      |       |

|                                                                    | (d)    | ٧                |         |          |       |       |         |        |         |        |      |       |

|                                                                    |        |                  |         |          |       | ٠     |         |        |         |        |      |       |

| 3.                                                                 |        |                  |         | ty bit f | or th | ne co | odes of | 2(a)   | and (b) | and t  | he e | even  |

| pari                                                               | ty bit | for $2(c$        | :) and  | (d).     |       |       |         |        |         |        |      |       |

### **OBJECTIVES OF THIS CHAPTER**

Having studied this chapter you should:

- Be familiar with octal and hexadecimal number system.

- Be able to convert denary numbers to octal or hexadecimal representations and vise versa.

- Understand the use of the symbolic representation of data.

We have seen that data is stored within the machine using a sequence of bits (0's and 1's). These sequences can be output to devices termed light emitting diodes (LED's). These are illuminated to indicate a '1' and extinguished to indicate a '0'. There is some merit in having this representation available to the user for program debugging but is fairly time consuming and error prone. More convenient representations have been devised which we will consider next.

Octal and Hexadecimal are two systems fairly convenient to use.

They encode a number of bits into a unique code and are frequently used at the machine/human interface.

Three bits are encoded in the OCTAL system to form a symbol between 0 and 7.

The table below indicates:

| BINARY | OCTAL |

|--------|-------|

|        |       |

| 0000   |       |

| 001    | 1     |

| 010    | 2     |

| 011    | 3     |

| 100    | 4     |

| 101    | 5     |

| 110    | 6     |

| 111    | 7     |

A sequence of 8-bits would be encoded as:

or  $043_8$  in Octal.

The subscript 8 denotes the base of the number system used.

The **Hexadecimal** system is now universally adopted for use in microprocessor systems since it uses only two symbols to encode 8-bits, that is four bits per symbol. The symbols used in the hexadecimal representation are 0-9 and A-F, sixteen symbols in all permitting a number system to base 16.

An hexadecimal conversion table related to Decimal, Binary and Octal is given below:

| DECIMAL | BINARY | HEX | OCTAL |

|---------|--------|-----|-------|

| 0       | 0000   | 0   | 0     |

| 1       | 0001   | 1   | 1     |

|         | 0010   | 2 . | 2     |

| 2       | 1      | 1   |       |

| 3       | 0011   | 3   | 3     |

| 4       | 0100   | 4   | 4     |

| 5       | 0101   | 5   | 5     |

| 6       | 0110   | 6   | 6     |

| 7       | 0111   | 7   | 7     |

| 8       | 1000   | 8   | 10    |

| 9       | 1001   | 9   | 11    |

| 10      | 1010   | А   | 12    |

| 11      | 1011   | В   | 13    |

| 12      | 1100   | С   | 14    |

| 13      | 1101   | ם   | 15    |

| 14      | 1110   | Ε   | 16    |

| 15      | 1111   | F   | 17    |

A sequence of 8-bits would be encoded as:

0100 1110

$${\rm 4} {\rm E}$$

or  ${\rm 4E}_{16}$  in hexadecimal.

Since the representation is universally accepted it is quite normal to omit the subscript 16. However, if confusion may result it is better to include it. It is convenient to have a method of conversion rather than have to rely upon a "look-up" table. The following may help:

### Decimal to Octal

### Octal to Decimal

1378 DEC IMAL

1 3 7

$$7 \times 8^{0} = 7 \times 1 = 7$$

$3 \times 8^{1} = 3 \times 8 = 24$

$1 \times 8^{2} = 1 \times 64 = \frac{64}{95}$

Thus  $137_8$  (Octal) = 95 (decimal).

### Decimal to Hexadecimal

Hexadecimal to Decimal

1AF -DEC IMAL

1 A F

F x

$$16^{0}$$

= F x 1 = 15

A x  $16^{1}$  = A x  $16$  = 160

1 x  $16^{2}$  = 1 x  $16^{2}$  =  $\frac{256}{431}$

Thus  $^{1AF}_{16}$  (Hexadecimal) =  $^{431}_{10}$  (decimal)

EXERCISE 1.5.1

Convert the following:

- Q1. 125<sub>10</sub>, 68<sub>10</sub>, 25<sub>10</sub> into:

- a) Straight Binary (8-bits)

- b) Octal

- c) Hexadecimal

- Q2.  $-62_{10}$ ,  $-94_{10}$ ,  $-32_{10}$ , into:

- a) Two's Complement (8-bit)

- b) Octal

- c) Hexadecimal

- 03. 1BA, 39F, 21C, into:

- a) Decimal

- b) Binary

Symbolic is a representation which is extremely user friendly since data is presented in symbolic form. For example, alphabetic characters are presented as such rather than a sequence of binary digits displayed on LED's, or as coded in Octal or Hexadecimal.

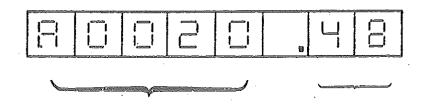

A suitable means of display is required such as a Cathode Ray Tube (CRT) Monitor or Printer. On most single board micro-processors provision for such display methods may not be available in which case communication with the microcomputer will almost undoubtedly be in hexadecimal.

# QUESTIONS

|     | (a)   | 22                                                 |

|-----|-------|----------------------------------------------------|

|     | ( a)  | -17                                                |

| 2′. | Con v | ert the following denary numbers into hexadecimal: |

|     | (a)   | 83                                                 |

|     | (b)   | <b>-45</b>                                         |

| 3′. | Conv  | ert the following hexadecimal numbers to denary:   |

|     | (a)   | 13F                                                |

|     | (b)   | 200                                                |

|     |       |                                                    |

1'. Convert the following denary numbers into octal:

# SECTION 2

# INTRODUCTION TO MICROCOMPUTERS

| Chapter | 2.1 | Introduction to the Microprocessor | Page | 1  |

|---------|-----|------------------------------------|------|----|

| Chapter | 2.2 | Microcomputer System Elements.     | Page | 10 |

| Chapter | 2.3 | Introduction to Programming        | Page | 19 |

| Chapter | 2.4 | The Instruction Set                | Page | 23 |

.

### **OBJECTIVES OF THIS CHAPTER**

Having studied this chapter you should;

Understand how the microprocessor fits into the architecturre of a microcomputer system.

Understand the function of the basic operational elements of a  $\min$  croprocessor.

Understand how the microprocessor communicates with other devices in the system.

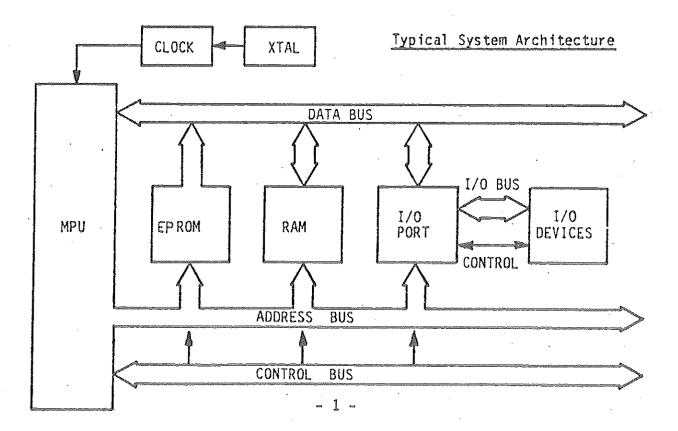

#### SYSTEM ARCHITECTURE

We have already looked fairly deeply at the way data is represented both internally and externally to the microcomputer. In this chapter we are going to consider how the microprocessor fits into the architecture of a typical microprocessor system such as Emma.

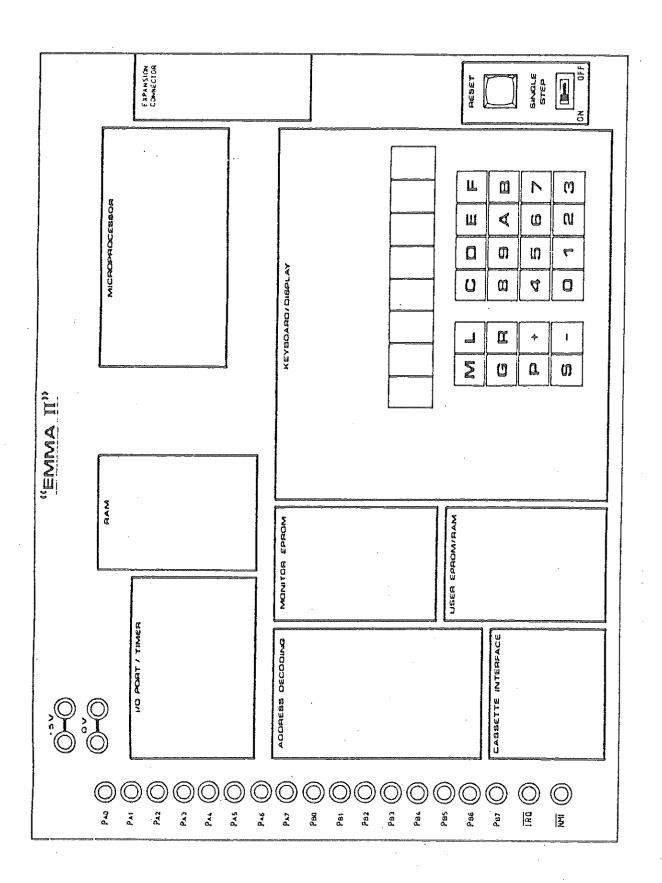

With the exception of the I/O Devices each of the component parts shown above can be identified upon the  $\it Emma$  microcomputer board. We will first examine the microprocessor followed by the other system components in the next chapter.

### A TYPICAL MICROPROCESSOR

We are going to relate our typical microprocessor to that used in  ${\bf Emma}$ . The various manufacturers of microprocessors configure their devices differently but the principles remain the same.

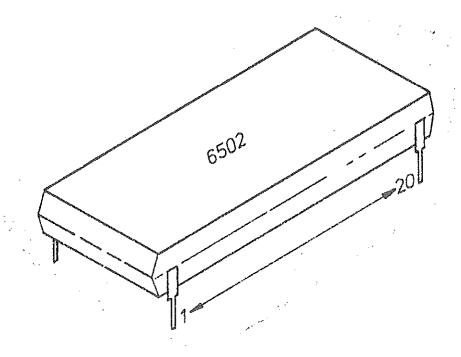

First we will pose the question "What is a microprocessor?" As a start it may be helpful if we could define what a **Process** is. One definition would be that a process is a series of operations which take place in a definite manner and a device capable of performing sequential operations in the manner defined would be referred to as a **Processor**. If the processor was physically very small as distinct to its complexity, we may well refer to it as a **Microprocessor**. In modern technological terms a microprocessor is all this. Additionally it is understood to be an **Electronic Device** contained within a small package known as an **Integrated Circuit** (I.C.). Integrated circuits are not confined solely to microprocessors and many electronic circuits are packaged in this way.

These integrated circuits are then used as electronic circuit building blocks and when appropriately connected together form a larger electronic system. An example of a system configured in this way is the Emma microcomputer which you are using.

The appearance of a typical microprocessor is shown overleaf You will easily be able to identify the one used in **Emma** by looking for the number 6502 marked on top of one of the larger IC's.

We also understand a microprocessor to be a device which performs arithmetic and logic operations on digitally encoded data. These operations are executed in sequence and as dictated by a **Program** of **Instructions** stored within **Memory**. The memory will form part of a complete system but will not necessarily be included in the microprocessor package.

The enormous power of the microprocessor lies in the speed at which it can execute these simple but humanly tedious operations and in the infinite variety of sequences which can be defined by the program of instructions.

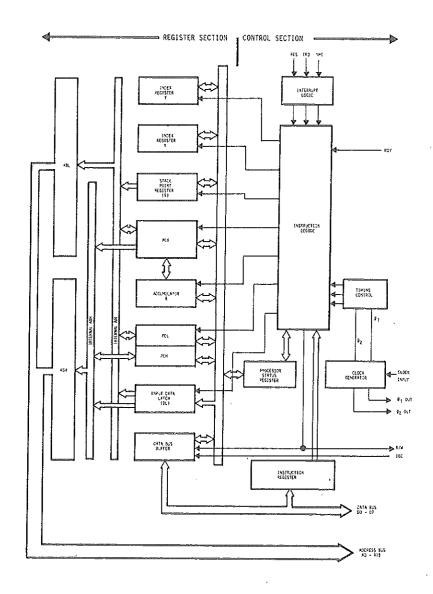

If we look at our system architecture: the microprocessor unit (MPU) appears as a single entity. Indeed it does comprise a single I.C. We can. however, identify, by function, a number of operational devices within the IC: although we cannot see them. It is these devices which we will now consider and a block diagram may help us to focus our thoughts.

INTERNAL ARCHITECTURE OF A MICROPROCESSOR The diagram is. in fact. that of the microprocessor used in Emma - the 6502. manufactured by Rockwell International.

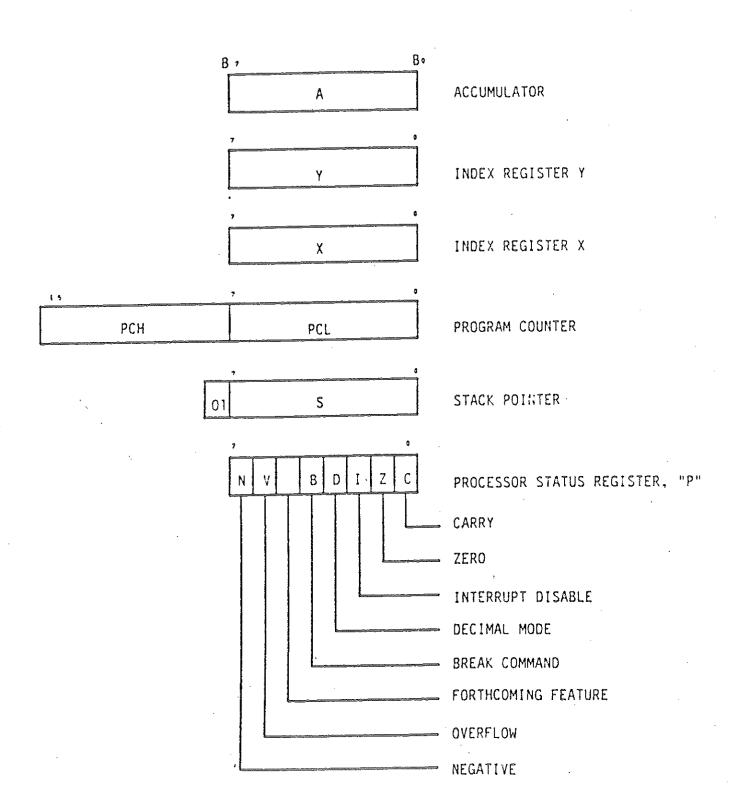

The Accumulator (A) is a general purpose register which has two basic functions:

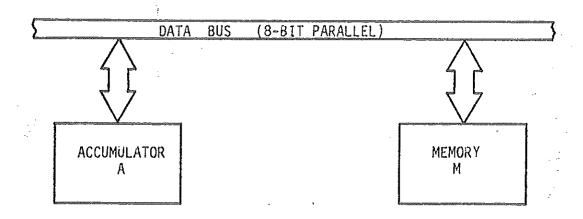

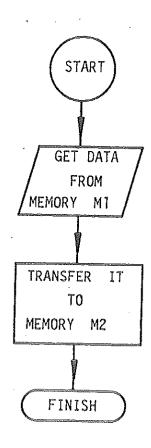

It acts as a primary storage element when data is moved from one memory location to another. Indeed all data transfers between memory locations will normally take place via the accumulator. These data transfers require a means to convey them and this is the function of the Data Bus. The diagram below indicates:

The accumulator also serves as a temporary storage element for intermediate results of arithmetic and logical operations. For example we may wish to perform an addition on two bytes of data. We can move the first byte into the accumulator. add to it the second byte, and leave the result in the accumulator.

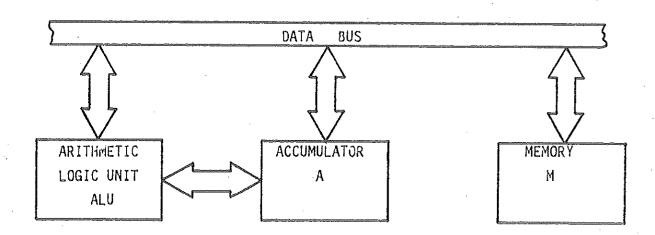

To perform these functions the accumulator works closely with the Arithmetic Logic Unit (ALU).

The Arithmetic Logic Unit (ALU) performs simple arithmetic calculations and logical operations. This is the function of the ALU and as can be seen from the diagram overleaf, data transfers can take place directly between the accumulator and the arithmetic logic unit.

The arithmetic logic unit comprises many parts and performs all the necessary operations to implement two's complement arithmetic. logical operations such as ANDing two bytes of data and testing the results of these and also many more functions.

All these operations and many more are under the control of a Timing Control Unit.

The Control Unit (CU)keeps track of each specific cycle of operation which takes place within a data transfer or manipulation. Each instruction, for example when adding two bytes of data together, will require a number of cycles of operations to completely execute the requested instruction. It is the function of the timing control unit to provide these timing pulses. To will mark the first cycle at the beginning of each instruction. If the second cycle and In the last cycle to complete the instruction. The control unit derives its accurate timing from a system clock.

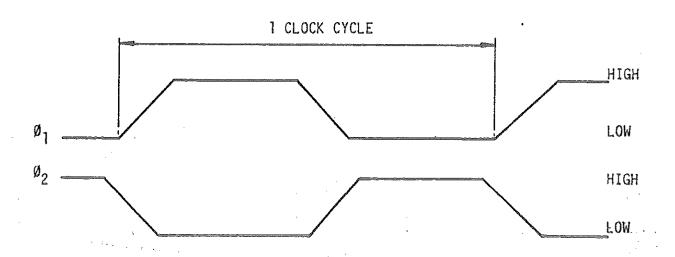

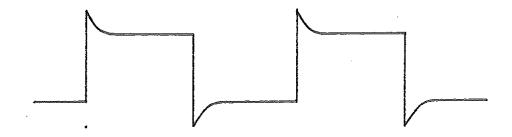

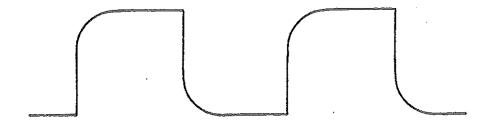

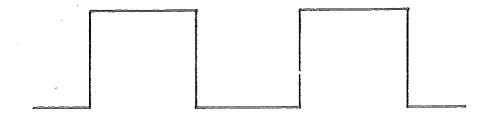

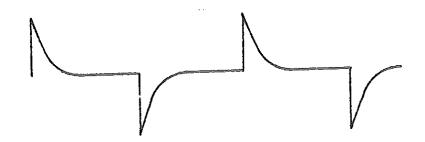

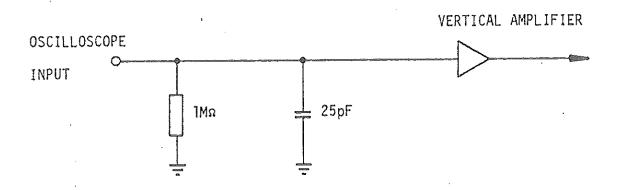

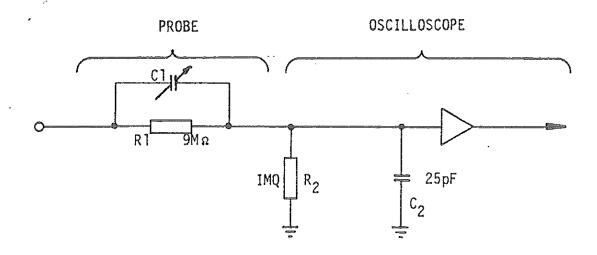

The Clock Generator is a device which produces two continuous waveforms whose frequency is accurately controlled by means of a quartz crystal (XIAL) which is external to the 6502 chip. The crystal maintains a frequency of 1MHz and the combination effectively acts as the 'heart beat' for the microcomputer system providing all timing reference points. We refer to the clock as being 'two phase' (Ø1 and Ø2) and non-overlapping. An exaggerated diagram of the waveforms is as shown below.

It will be noted that  $\emptyset_1$  and  $\emptyset_2$  are not at logic 1 (High) at the same time. That is they are not allowed to overlap. The events which take place within the microprocessor (or microcomputer system) depend upon whether  $\emptyset_1$  or  $\emptyset_2$  is at logic one.

The Instruction Decode/Instruction Register works closely with the Control Unit. The block diagram for the microprocessor can be seen to be split roughly into two parts; a 'control' side and a 'register' side. Data is processed in the register side and the sequence of operations performed for each instruction (such as ADD two bytes of data together) by the elements on the control side. However, the overall sequence of instructions that the microprocessor may be called upon to obey are dictated by the program of instructions. The data representing the program is latched into the INSTRUCTION REGISTER and then decoded by the INSTRUCTION DECODE circuitry, this, along with the timing control output, to generate Control Signals FOR EACH OF THE VARIOUS REGISTERS. These control signals may also be influenced by external incoming signals such as those produced by external devices interrupting the actual processing functions. These would appear via the Interrupt Logic Circuitry but others, such as the Ready (RDY) signal, may also hold up processing for various reasons.

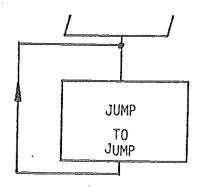

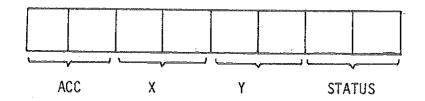

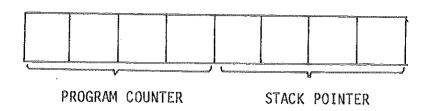

The Program Counter (PC) is simply a register which holds the address in memory of the next data item which the microprocessor will call for. The counter is incremented each time an instruction, or data upon which the instruction may operate, is fetched from the system memory.

The program counter may be modified, other than simply incremented, by events which may occur through execution of the program.

Index Registers (X) and (Y)/Stack Pointer (S) are simple 80it latches which store data that is to be used in calculating addresses in data memory. We will discuss these in more detail when actually writing programs to run on Emma.

The Process Status Register (P) is a register which consists of eight individual latches. These may be set or cleared either under program control, or automatically by the microprocessor. The contents of these latches reflect the current Status of the microprocessor and may be inspected by the programmer under program control.

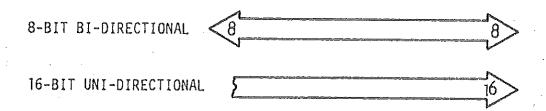

DATA AND ADDRESS BUSES are simply a group of electrically conducting paths grouped together by function. Data, in the form of a memory address or data to be operated upon, is pressed along these. The data bus is typically an &bit parallel bus while the address bus is typically a 16bit parallel bus. It is normal to symbolise these buses as follows:

The data bus is normally bi-directional (data can pass in either direction) since data will be required to pass both into and out of the microprocessor.

The address bus is normally uni-directional (data passes in one direction only) since all addresses will be generated by the microprocessor.

**Buffers** are devices which "buffer" or isolate the microprocessor internal buses from the buses external to it. In the case of the 6502 they provide TTL compatible bus drivers delivering sufficient capacity for 1 standard TTL load and at least 130 pF.

The address bus buffers also provide latches which hold the addresses when used in accessing peripheral devices such as RAM, ROM and I/O.

The data bus has been seen to be bi-directional and as it connects together a number of devices all capable of feeding data on to it, conflict can exist. This is overcome by making the buffers enter a high impedance state (third state other than high and low) when not transferring data.

# QUESTIONS

- 1. What is the accumulator andwhat is its purpose.

- 2. What is the ALU used for.

- 3. What is stored in the program counter?

- 4. Is the data bus unidirectional or bidirectional.

- 5. Why is it necessary to have a third: high impedence state other than logic '1' or '0') on some devices.

### OBJECTIVES OF THIS CHAPTER

Having studied this chapter you should:

- Be familiar with the different types of memory device used in a microcomputer.

- Understand the function of the monitor program.

- Be familiar with the use of input/output ports for communication with external devices.

- Understand how the microcomputer execute a single instruction.

### A TYPICAL MICROCOMPUTER SYSTEM

As we did with the microprocessor, we will relate our discussion to the **Emma** microcomputer. However, the devices used are common to microcomputers in general and hence generally applicable.

We have suggested that in general the microprocessing unit does not possess any program or data storage capacity. Also, it has limited capability to converse directly with the outside world in the shape of peripherals (printers, visual display units, control devices etc.). We will deal with each of these in turn.

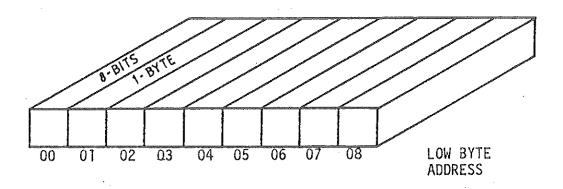

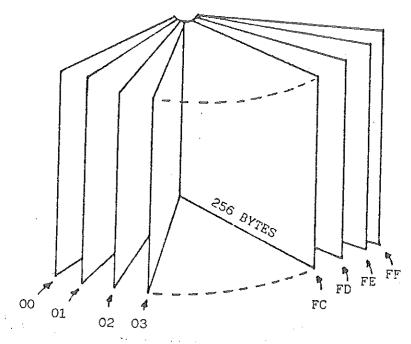

Memory Devices are simply registers. We have already familiarised ourselves with the term 'register' as being a device capable of storing a binary word. If a number of registers are grouped together, each capable of being individually addressed and holding a single byte, we have the concept of a memory device. In practical terms these devices may contain 1024 (1K) or 2048 (2K) or more of memory locations. If the device is only capable of being READ (we can only look at the data already stored) it is known as a Read Only Memory or ROM.

If, on the other hand, we can WRITE (input data) into the device under program control as well as READ it, we refer to it as a **Random**Access Memory or RAM.

Both devices are, in fact, random access in the sense that we can access any desired memory location. We do not have to start at the first and work our way through until we arrive at the one we wish to either read (ROM) or read/write (RAM).

A simple ROM Device can only be written into once; there is no way in which the data stored can be erased. The **Eprom** however is a device which can be erased and then used again - it is both an erasable (E) and reprogrammable (P), ROM.

There is another feature of these devices which is of importance. ROM devices are non-volatile, that is when the supply is removed from the system the data contained within them remains; it is not lost. RAM devices lose their data upon loss of supply unless special provision is made to maintain the data, for example, provide a back-up battery. We would refer to such memory as **battery-backed** RAM. It should be noted that under conditions of 'back-up' the system cannot be used in an operational sense.

We may ask why use both ROM and RAM within a system. All microprocessors require a program which will operate automatically when the machine is switched on and/or when a reset button is pressed. This program is termed the **Monitor**. It is designed by the system manufacturer and must not be lost when the system supply is removed. It must be stored in non-volatile memory. Monitors have various features in common:

- They permit the system user to address any memory location and display its contents.

- They permit the user to modify the data stored in any addressed memory location.

- They permit the system user's program to take control of the microprocessor and to return control back to the monitor as required.

Various other features may be present.

For example, the Emma monitor provides.

facilities for the loading or storing of programs

from or to magnetic tape via a cassette tape

recorder. It also provides a means of debugging user

programs by allowing the operator to run a program

and inspect automatically the content of important

registers such as the accumulator and status register

etc. In addition to all this, the EMMA monitor allows

the programmer to make use of some of its program

routines and hence simplify his program.

A schematic organisation of the individual memory functions is as shown in the diagram below:

Each location stores effectively 8-bits of encoded data and has a unique address encoded in hexadecimal for programming convenience.

A 2K EPROM would have 2048 locations starting at address 0000 and ending at address 07FF. We will return to the topic of memory addressing later.

INPUT/OUTPUT PORTS are referred to as I/O devices. Their function is to act as an imput or output route for transferring data to or from microprocessor and application devices such as keypads, transistorised drive circuits for electromechanical devices (solenoids, stepper motors, relays etc.) and displays of various sorts.

I/O ports generally appear to the microprocessor as memory locations of 8-bits. Each bit can usually be set under program control to act as either an input port or an output port. Other features may well be available. For example the 6522 I/O port used in the Emma system comprises two 8-bit programmable I/O ports, two programmable timers and means whereby data can be input or output in a serial mode. It is a powerful device in its own right. We will look more deeply at I/O ports later.

Peripheral Device is a general term used to describe machines which are not physically part of a computer system, but may act in conjunction with it. They are used typically to display data either on a visual display unit or printer or store data on a disc or magnetic tape. The matrix printer and the cassette recorder which you will use with Emma are examples. Some of these devices may use an I/O port to communicate with the microprocessor (as when using the matrix printer) or a special interface as used for the cassette recorder. The display monitor used with the Emma-Visa combination uses a dedicated Cathode Ray Tube Controller (CRTC).

We have now completed a brief look at the various components which go to make up a microcomputer system. More complete details are to be found in the **Emma User and Technical Manuals** and you are encouraged to consult these.

We will now address ourselves to how these components operate within the concept of a microcomputer system.

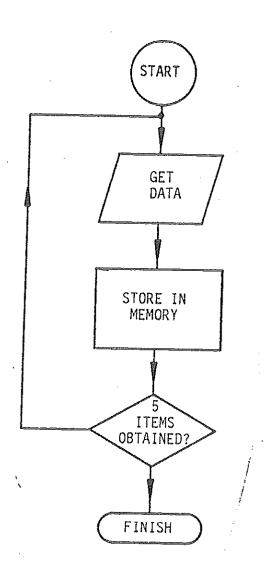

# MICROCOMPUTER SYSTEM OPERATION

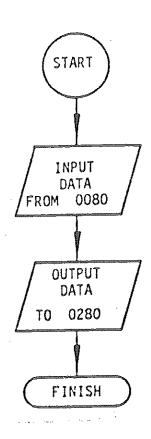

We have already intimated that a microcomputer is capable of performing extremely complex functions by means of a series of simple operations. Control of the microcomputer system is largely the responsibility of the microprocessor. This causes the system to perform the desired operations by reading the first instruction of a program, and then 'executing' that instruction. The microprocessor will then 'fetch' the next instruction from memory, decode (interpret) it and then execute it. It will repeat these 'fetch/execute' cycles for each instruction until the program is terminated. Let us look at this in more detail.

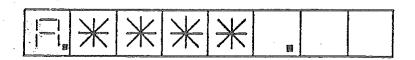

A program instruction will usually, but not always; comprise two parts:

| 02. | CODE | OPERAND |

|-----|------|---------|

|     |      |         |

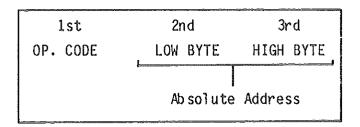

- he term **Op. Code** is short for 'Operation Code'. It is a single byte which specifies the type of operation which is to be performed. These codes are determined by the manufacturer of the microprocessor and are listed in the **Instruction Set** (see Appendix 7) for the particular microprocessor in use.

- The **Operand** may comprise either one or two bytes. If it is a single byte it may be data which is to be directly operated upon or it may specify the address of the data which is to be operated upon. Where two bytes are used for the operand: they specify an absolute address for data.

Let us consider a particular instruction which occurs frequently in any program of instructions:

Load Accumulator with Memory (LDA).

The instruction performs the operation - Transfer the contents of a specifed memory into the accumulator. We can specify this operation symbolically as (M)-- A: where () means "contents of". and -- means "transfer to".

The specified Op. Code for this instruction is AD(HEX) (encoded in hexadecimal).

Let us assume the following:

- The data we wish to transfer into the accumulator is FF(HEX).

- The data is located at absolute address 0360(HEX).

The program is to commence at absolute address 0020(HEX).

Our program is to be stored in RAM and can be tabulated as:

|       | CONTENTS                                                                                                       |             | COMMENTS             |

|-------|----------------------------------------------------------------------------------------------------------------|-------------|----------------------|

| (HEX) | (HEX)                                                                                                          | (BINARY)    |                      |

|       | المسارات المساورة العروب مدين مدين مدين مدين المساورة المساورة المساورة المساورة المساورة المساورة المساورة ال |             |                      |

| 0020  | AU                                                                                                             | 1010 1101   | Or. Code             |

| 0021  | 60                                                                                                             | 0110 0000   | low byte of address  |

| 0022  | Ŭ <b>3</b>                                                                                                     | 0000 0011   | high byte of address |

| 0023  | OP. Code o                                                                                                     | f next inst | ruction              |

0360 FF 1111 1111 data to be transferred

Let us now see how the microcomputer would operate to effect this instruction. Under Monitor control, we would start the running of the program by pressing an appropriate control pushbutton or key. This would be detected and the user asked to provide the start address of the program to be run. Once accepted, system control would automatically be passed from the Monitor to the User program. We can best describe how our first instruction is executed by means of the table overleaf.

| TIMING CONTROL CYCLE (t <sub>n</sub> ) | DATA ON<br>ADDRESS | DATA ON<br>DATA BUS | COMMENTS                                                |

|----------------------------------------|--------------------|---------------------|---------------------------------------------------------|

| To                                     | P.C.               | 0.P. Code           | Fetch OP. Code.                                         |

| <sup>†</sup> 1                         | РС + 1             | ADL                 | . Decode OP Code.<br>. Fetch low order<br>address byte. |

| T <sub>2</sub>                         | PC + 2             | ADH                 | Fetch high order address<br>byte.                       |

| T <sub>3</sub>                         | ADH. ADL           | DATA                | Fetch Data                                              |

| То                                     | PC + 3             | NEXT OP. CODE       | . LUAD Accumulator with Data FEICH next op. code.       |

All instructions performed by the processor can be tabulated in this way and are in fact done so. You will find them under the heading 'Summary of Single Cycle Executions' in the Emma Technical Manual.

The important points to notice from the table are:

- The instruction takes a definite known time to execute.

- The data appearing on both the address and data buses for any clock cycle is known.

# QUESTIONS

| <ul> <li>(a) RAM</li> <li>(b) ROM</li> <li>(c) EPROM</li> <li>2. Which of the above are suitable for:</li> <li>(a) Writing to?</li> <li>(b) Random access?</li> <li>3. How does the microcomputer access I/O ports?</li> <li>4. What is an Up Code?</li> <li>5. What is meant by (W) → A?</li> <li>6. What is the next operation performed by the processor after the completion of an instruction.</li> </ul> | T.  | and c do the following appreviations staild for: |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------|

| <ul> <li>(c) EPROW</li> <li>2. Which of the above are suitable for:</li> <li>(a) Writing to?</li> <li>(b) Random access?</li> <li>3. How does the microcomputer access I/O ports?</li> <li>4. What is an Op Code?</li> <li>5. What is meant by (H) → A?</li> <li>6. What is the next operation performed by the processor after the</li> </ul>                                                                 | (a) | RAM .                                            |

| <ol> <li>Which of the above are suitable for:</li> <li>(a) Writing to?</li> <li>(b) Random access?</li> <li>How does the microcomputer access I/O ports?</li> <li>What is an Op Code?</li> <li>What is meant by (H) - A?</li> <li>What is the next operation performed by the processor after the</li> </ol>                                                                                                   | (b) | KOM                                              |

| <ul> <li>(a) Writing to?</li> <li>(b) Kandom access?</li> <li>3. How does the microcomputer access I/O ports?</li> <li>4. What is an Op Code?</li> <li>5. What is meant by (H) - A?</li> <li>6. What is the next operation performed by the processor after the</li> </ul>                                                                                                                                     | (c) | EPROM                                            |

| <ul> <li>(b) Kandom access?</li> <li>3. how does the microcomputer access I/O ports?</li> <li>4. What is an Op Code?</li> <li>5. What is meant by (H) - A?</li> <li>6. What is the next operation performed by the processor after the</li> </ul>                                                                                                                                                              | 2.  | Which of the above are suitable for:             |

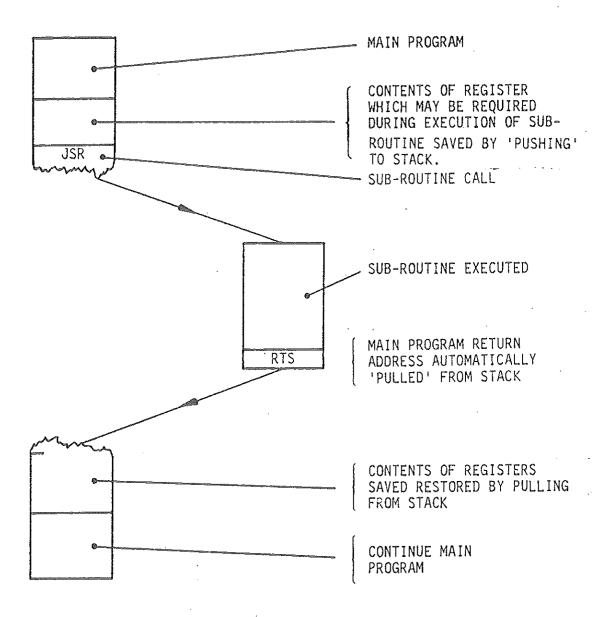

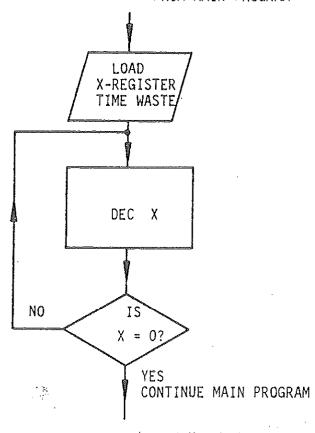

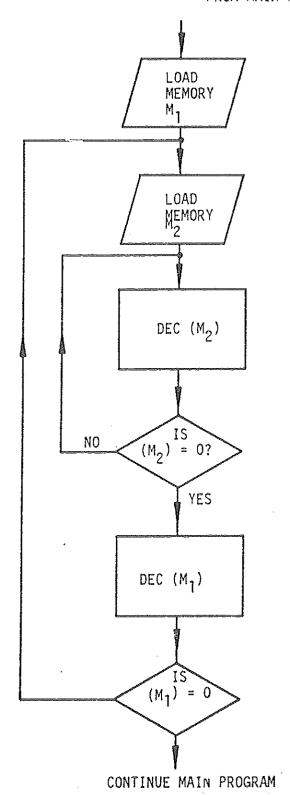

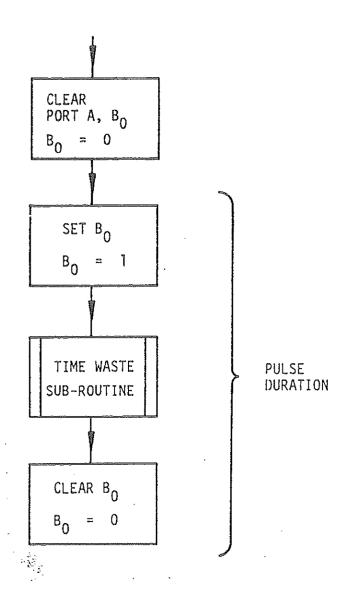

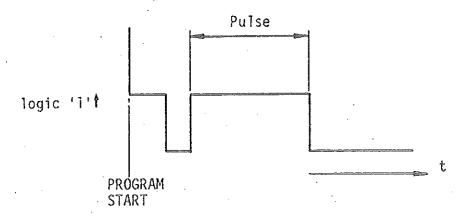

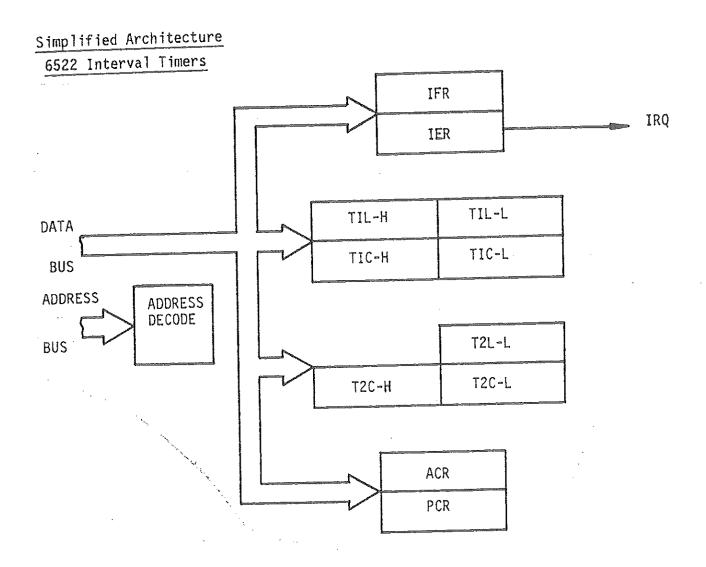

| <ul> <li>3. How does the microcomputer access I/O ports?</li> <li>4. What is an Up Code?</li> <li>5. What is meant by (H) 	A?</li> <li>6. What is the next operation performed by the processor after the</li> </ul>                                                                                                                                                                                           | (a) | Writing to?                                      |