# HANDLER SOWNER'S MANUAL

REV-B C.R.-2-8-7 by C.A..Indiha

### Western Data Systems

3650 Charles Street • Suite G • Santa Clara, Calif. 95050 • (408) 984-7804

#

#### KITS:

Western Data Systems hereby warrants all. Data Handler kits that, 1) during the first thirty (30) days of ownership all components supplied by W.D.S. to be free from defects in materials and workmanship, and 2) in the event of component failure or malfunction said components will be repaired or replaced free of charge at the descretion of W.D.S. when returned to the factory postage paid.

Any returned Data Handler kits which have been fully owner assembled and require factory repair due to normal use and service within the first thirty (30) days of ownership, will be repaired to operating order for a nominal shipping and handling charge of \$10.00.

#### ASSEMBLED UNITS:

During the first three (3) months of ownership, any factory assembled units, that we determine, under conditions of normal use and service, fail to perform according to our published specification, will be repaired or replaced, at no charge to you, at the W.D.S. factory.

The above warranty applies to the original purchaser only, and does not cover damage by use of acid-core solder, incorrect assembly, misuse, fire, floods or acts of God. If W.D.S. or a representative there of determines that your Data Handler system needs repair due to said conditions, a charge greater than the nominal amount may be required.

#### -CONTENTS-

| •                       | PAGES   |

|-------------------------|---------|

| INTRODUCTION            | -1-2    |

| SPECIFICATIONS          | - 3     |

| SYSTEM INFORMATION      | - 4 - 5 |

| MEMORY MAP              | - 6     |

| I/O PORT INFORMATION    | -7-9    |

| OPERATING INSTRUCTIONS  | -10-15  |

| SYSTEM EXPANSION        | -16-17  |

| PRE-ASSEMBLY NOTES      | -18-20  |

| ASSEMBLY INSTRUCTIONS   | -21-23  |

| THEORY OF OPERATION     | -24-27  |

| SYSTEM CHECKOUT         | 28-30   |

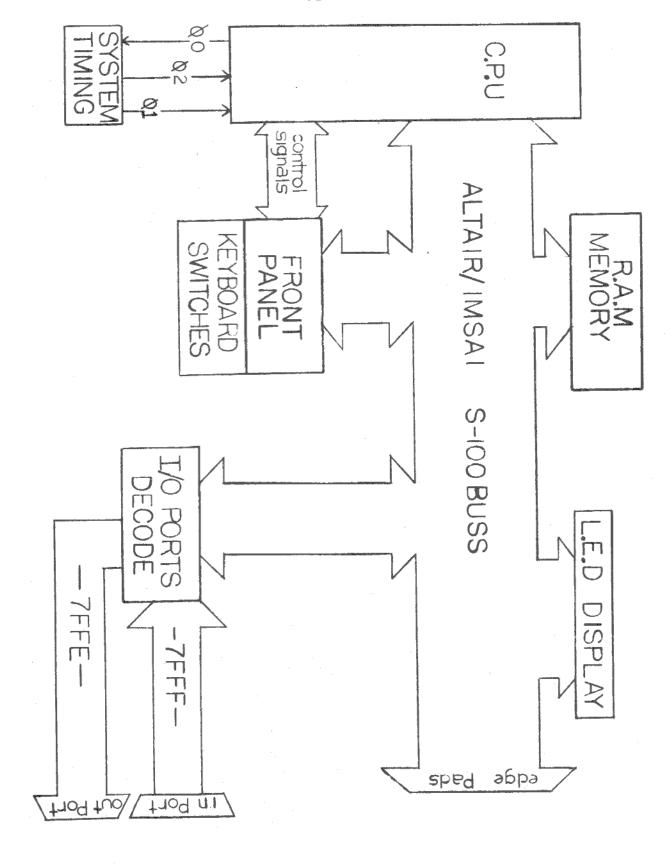

| D.H. BLOCK DIAGRAM      | 31      |

| TROUBLESHOOTING         | 32-34   |

| COMPONENT LAYOUT        | 35      |

| I.C.LOCATION/PARTS LIST | 36      |

| SCHEMATIC DIAGRAMS      | 37      |

| INSTRUCTION LISTINGS    | 38      |

| SOFTWARE                | 39      |

#### INTRODUCTION

The Data Handler is a complete microcomputer system on a single printed circuit board (P.C.B.) designed around the Mos Technology 6502 microprocessor.

This complete microcomputer system contains one thousand words (1K bytes) of random access memory (ram), one eight bit parallel input port with data latch and interrupt strobe, and one eight bit parallel output port with clearable data flag. The Data Handler contains a 26 keyboard switch hardware controlled front panel which will load data, examine data, perform single cycle and single instruction, initialize the system, run and halt the system all in hexidecimal (Base 16) format.

It contains a complete on board discrete L.E.D. hexidecimal address and data display which display the sixteen address bus lines and the eight data bus lines.

Also on the Data Handler P.C.B. are three discrete L.E.D.'s which indicates whether the Data Handler front panel is in the address or data entry mode and whether it is halted or running.

#### INTRODUCTION:

The left rear portion of the P.C.B. contains two etched rows of fifty pads to facilitate the installation of one, one hundred pin Altair/IMSAI type P.C.B. edge connection, or suitable connector to allow bus expansion.

These pads contain the tri-state buffered data, address, memory, I/O (input/output) signals, and timing signals used by the 8800 Altair/IMSAI type peripheral boards. These bus lines are pin for pin compatable, and drive/receiver matched with the 8800 Altair/IMSAI microcomputer peripherals.

These peripheral boards are the least expensive, most widely available, and offer the greatest variety in microcomputer peripherals available on the face of the earth.

The Data Handler is ideally suited as a computer instructing device due to it's easy to understand and use qualities yet retains the capabilities for gross system expansion by the advanced user, further, the Data Handler is an excellent choice as an enexpensive tool for providing computer control for machinery, video displays, or electronic projects.

Note that the assembled Data Handler requires an external power source +5 volts DC at about 1.8 amps. However a power supply capable of supplying 4 to 6 amps is recommended for future expansion.

## THE DATA HANDLER SPECIFICATIONS:

Uses the Mos Technology 6502 microprocessor.

Directly addresses 65K bytes of memory.

Contains 1K bytes of 500 ns ram on the P.C.B. (address FC00-FFFF).

Slow down circuitry for slow memories.

Direct memory access (DMA) circuitry and DMA acknowledge control lines.

Dual interrupt lines-one maskable, and one non-maskable.

On board dual I/O ports, one 8 bit latching parallel input port with interrupt strobe, and one 8 bit latching parallel output port with a data flag.

Variable speed R/C clock, or optional crystal may be used for frequency stability to 2 mhz.

8800 Altair/IMSAI identical tri-state address and data bus.

Uses single +5 volts supply @ 1.8 amps.

Large on the board ground plane for noise suppression at high operating frequency.

Discrete L.E.D.'s for address and data display.

Full function hardware controlled front panel.

Keyboard type data and control switches in hexidecimal format.

#### SYSTEM INFORMATION:

SYSTEM SPEED: The maximum operating speed of the small or expanded Data Handler system is determined by two factors.

1. C.P.U. speed, and 2. memory access time.

The 6502 microprocessor is presently available in models with operating speeds to 4 mhz (250 ns cycle time). Due to the internal characteristics of the 6502, minimum memory access time (reading stable data from memory) is to be approximately half the cycle time. A system operating at 4 mhz needs a memory with a 125 ns access time, 250 ns for 2 mhz, 500 ns for 1 mhz (supplied in the Data Handler complete kit), and so on. To double the normal data throughput of the Data Handler (operate at 2 mhz), a 6502A microprocessor should be installed, change R65 to a 1K 1/4 W, and change the memory I.C.'s (D1-D8) to 2102A-2. For general system usage the kit supplied RC timing network is perfectly adequate. By setting the 50K ohm timing potentiometer (VR1) midway, a normal system clock speed of approximately 1 mhz will be in operation with a stability factor + 20%. For time critical rock hard system stability greater than + 20% a crystal may be incorporated into the processor timing.

CRYSTAL OPERATION: If crystal frequency stability is desired for the Data Handler system a user supplied crystal may be installed in the two mounting holes on both sides of XL1 on the right rear portion of the P.C.R..

#### SYSTEM INFORMATION:

(CON'T) <u>CRYSTAL OPERATION</u>: This XL1 layout was designed to accomidate an AUGAT 8000-D crystal holder, however the crystal may be soldered directly on the P.C.B. then laid down onto the adjacent ground plane area, and the can (crystal cas soldered to the ground plane directly beneath it with a short piece of resistor lead or other type of wire.

SPARE LOCATIONS: The Data Handler P.C.B. contains three spare I.C. locations (C1,C2,D11), these spares can be used for any user designed changes made to the circuitry to tailor it for some particular use. Circuitry modifications using these spare I.C. locations can best be made with 30GA. wire wrap wire on the under side of the Data Handler P.C.B. using the point to point wireing technique.

#### MEMORY MAP:

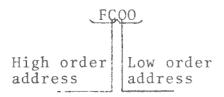

The Data Handler contains one thousand words

(1K bytes) of random access memory (ram) on the P.C.B.

These are decoded as address FC00 thru FFFF, and are used for program storage and processor vectoring which is located in the following memory locations:

FFFA- Low order address for NMI FFFB- High order address for NMI

FFFC- Low order address for front panel INT FFFD- High order address for front panel INT

FFFE- Low order address for program interrupt FFFF- High order address for program interrupt

When additional ram memory is used in the Data Handler system, it is recommended that this memory be located beginning at address 0000 to fully utilize the stack function of the processor.

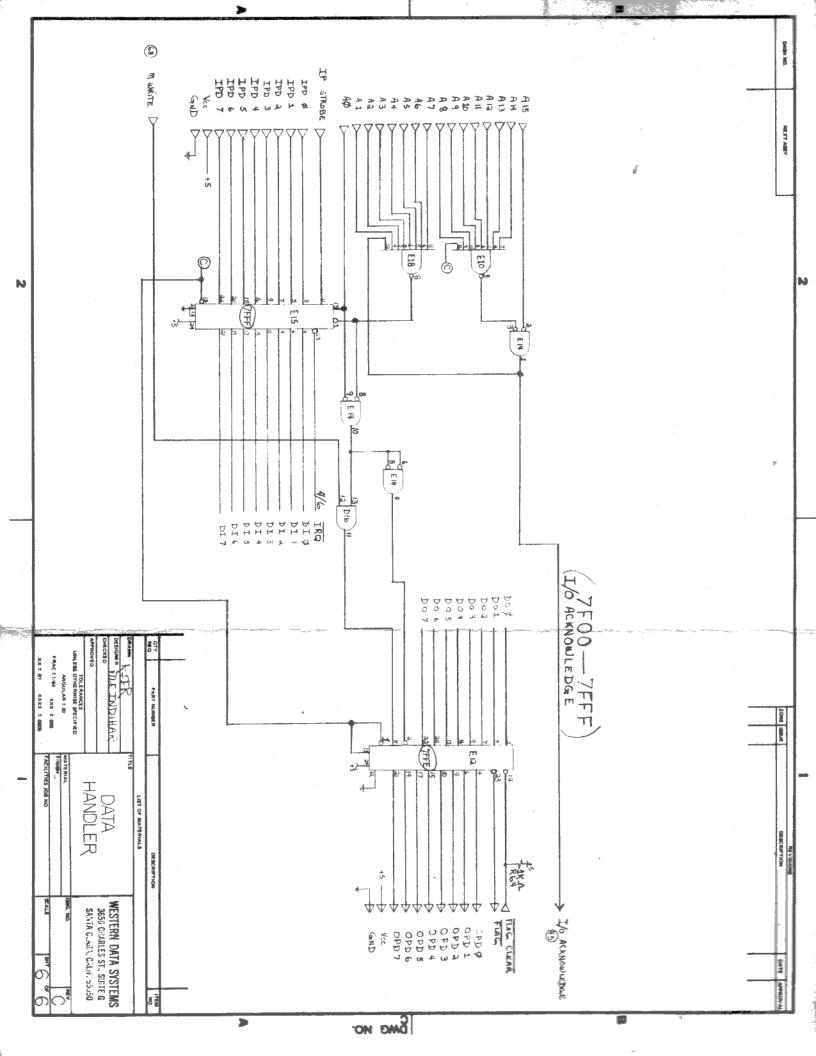

The address locations 7F00 thru 7FFF are decoded on the Data Handler P.C.B. as the I/O device code area. (the area in memory designated for input and output devices).

It is recommended that memory not be decoded to this address area.

#### I/O PORT INFORMATION:

The two parallel data ports on the Data Handler are the immediately available means for communication with external devices, the input port receives the data and the output port transmits the data. These ports exit the Data Handler by means of solder pads on the right rear portion of the P.C.B.. The individual solder pads are labled for their signal identity and were designed for wire connection directly to the external If different devices are to be used at different times it is suggested that a cable connector (a 15 pin cinch connector works excellent) be wired on the hottom of the port solder pads with matting connectors on each external device. Examples of input devices are a TVT type video display, cassett interface, OP-80A papaer tape reader, radio shack 63 key keyboa ASCII encorder board, ect. Data entering the Data Handler fro an external device can be seen visually on the data L.E.D.'s by halting the Data Handler and examining the input port (address 7FFF).

The output port has an endless number of uses.

Examples include control of solor heating, sprinkler control, computerized liquor/wine dispensor, video generation, machine control, ect.

I/O PORT INFORMATION: (EXAMPLES)

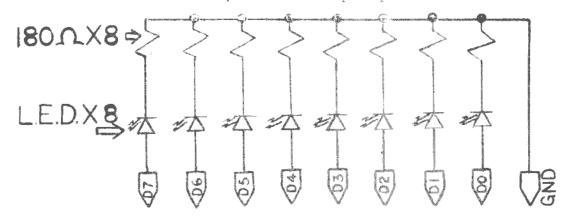

FIGURE 1. Illustrates a very simple programable L.E.D. bit display which can be built in ½ hour for the cost of about \$1.50 and can be used directly on the output port.

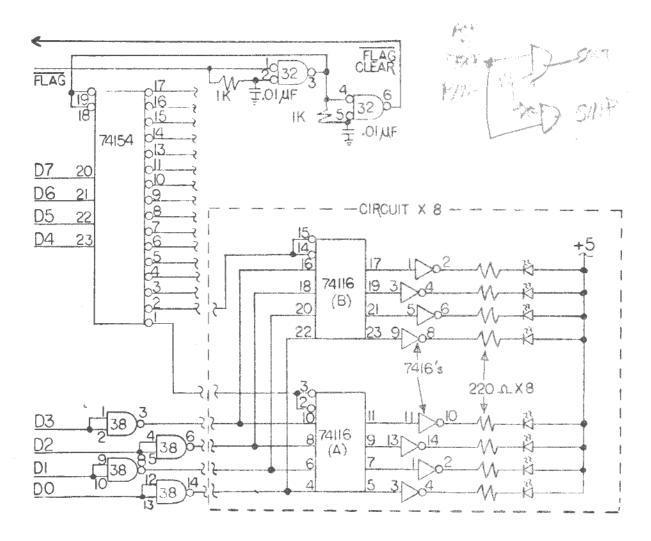

FIGURE 2. Shows a more complex programable display with 64 L.E.D.'s.

#### I/O PORT INFORMATION:

One eight bit parallel latching input port (I.C.E16) is available on the right rear portion of the P.C.B.. It is designated as address 7FFF and is loaded with positive data on the input strobe of a low to high pulse. This data strobe will output a data available flag to the Data Handler interrupt line, this interrupt line which is located to the rear of pin 24 on I.C.E16 looks like a double ended arrow. This if desired may be severed with a sharp knife. Cutting this line will isolate only the input port data available flag from the interrupt line.

Data loaded in this port and the interrupt flag will automatically be cleared to zero immediately after the cycle in which it is addressed by the user program.

One eight bit parallel latching output port (I.C.E12) is available to the left of the input port. This port is designated as address 7FFF and contains two output control signals,

(1) a data flag, and (2) a flag clear.

The data flag (data available signal) when in the high state, indicates that a data word has been latched up and is available in this port. The flag clear is an input signal to this port and when in the low state will clear the data and the data flag.

Both the input and output ports are latched/buffered with 8212 (748412) port buffers, and are capable of driving 40 MA each making them suitable for directly driving power transistors (2N3055's), SCR's ect.

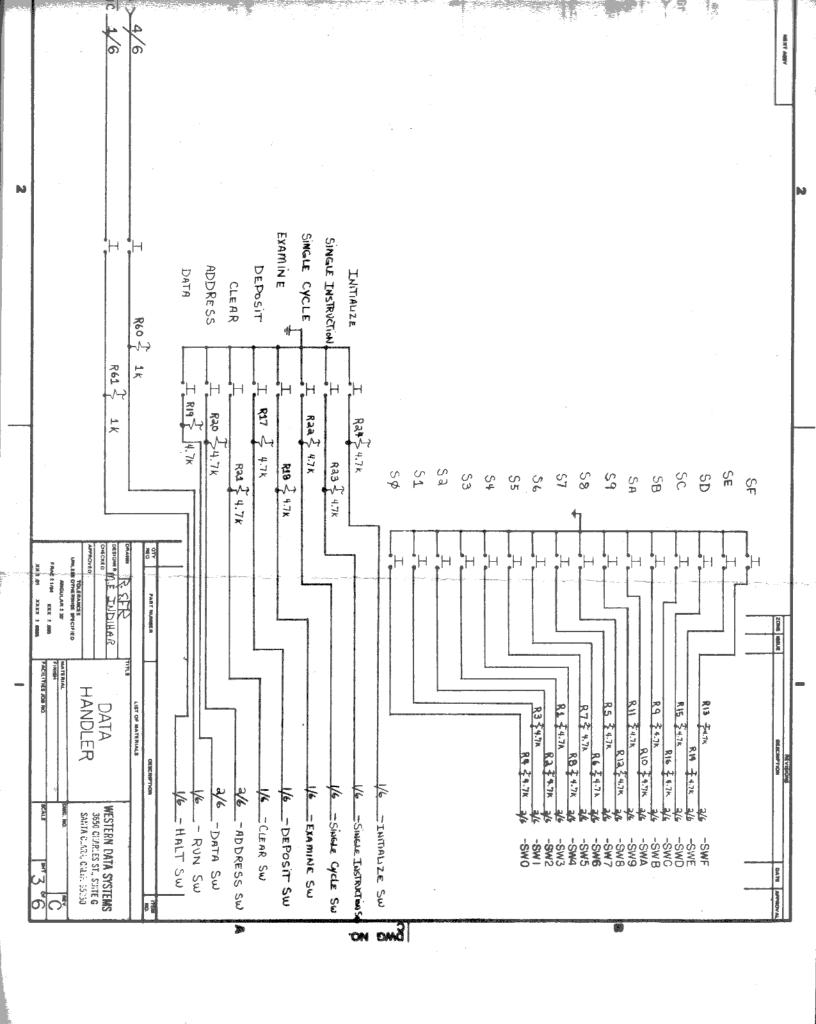

The Data Handler hardware controlled keyboard is composed of 26 keyboard switches which are divided into one group of ten, and one group of sixteen.

The group of ten contains the function switches

DP (Deposit) EX (Examine) (Clear) CL(Address) AD (Data) DA (Single Instruction) SI (Single Cycle) SC (Processor Halt) (Processor Run) RN INT (Initialize)

The group of sixteen switches contains 0 thru F (hexidecimal) for data <u>and</u> address loading.

The Data Handler information display is comprised of 27 discrete L.E.D.'s (light emitting diodes), 26 red and one yellow. This display is divided into a row (bottom row) of 16 L.E.D.'s which represent in hex format the current address, and the top row of 8 represent the current data. the M.S.B. (most signifigant bit) of each row is the left most L.F.D.

In the group of three L.E.D.'s to the left of the keyboard, the top one labeled data indicates that the keyboard switches 0 thru F will be displayed on the data L.E.D.'s. Pressing the AD function switch will change the loading to the address L.E.D.'s. The bottom yellow L.E.D. indicates that the Data Handler is free running when it is on, and in the halted mode when it is off.

#### TO DEPOSIT DATA:

Press HT--Halt the Data Handler (disregard if already halted)

Press CL--Clear the internal mode and the data holding registers.

Press AD--To switch the loading to the address lines (address L.E.D.'s)

Key in the desired address to be modified.

Press DA--To switch the loading to the data lines (data L.E.D.'s)

Key in the desired data to be loaded in the present displayed address.

Press DP--This will deposit the data currently on the data lines into the address that is currently on the address lines.

After making the deposit into memory the Data Handler will automatically increment to the next address location, so that only the data needs to be altered and deposit pressed again for loading subsequent instructions.

The Data Handler has a deposit lock out when in the examine mode to prevent inadvertant depositing of data.

To switch from the examine mode to the deposit mode or vise versa the Data Handler must be exercised through one complete instruction (press SI once) before the desired mode can be selected.

#### TO EXAMINE DATA:

PRESS HT--Halt the Data Handler (disregard if already halted).

PRESS EX--Put the internal registers in the examine mode.

PRESS AD--To place the keyboard entry on the address lines.

Load the address to be examined onto the address lines, and the data L.E.D.'s will then display the data in that location of memory.

When in the examine mode, each time the EX function switch is pressed the next address and it's data will be displayed.

Depositing and examining data will not affect the PC counter of the 6502 microprocessor, in that the Data Handler can be halted, data examined and or deposited without disturbing the existing running program sequence.

#### SINGLE INSTRUCTION:

PRESS HT--Halt the Data Handler (disregard if already halted)

PRESS SI--The Data Handler will execute the next instruction and stop. Each time the SI switch is pressed the Data Handler will execute the next instruction and stop.

#### SINGLE CYCLE:

PRESS HT--Halt the Data Handler (disregard if already halted)

PRESS SC--The Data Handler will execute one cycle of the next instruction and stop.

Using the SI and SC modes to "walk" through a newly loaded or newly written program can save countless hours in the debuging of software, in that branches, jumps, all steps of the program are displayed and executed under full control of the operator.

#### INITIALIZE:

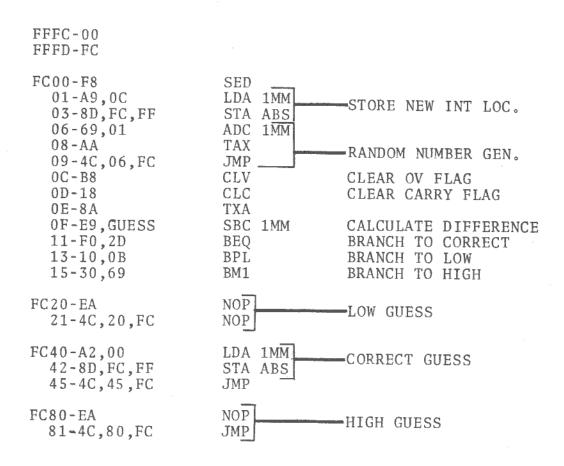

When the INT switch is pressed the 6502 MP will begin the initialize process which consist of 6 cycles in which it will dump it's present address on the stack, and load it's program counter (PC) from it's initialize vector locations. The Data Handler will then begin executing at that memory location when run is pressed.

(To demonstrate this let's load a small loop program)

Deposit the following data starting at address location

FC00 by using the format discussed for depositing data.

| ADDRESS | DATA | INSTRUCTION                             |

|---------|------|-----------------------------------------|

| FC00    | Dit  | NOP ,                                   |

| 02      | 4C   | JMP                                     |

| 03      | 0.0  | LOW ORDER ADDRESS<br>HIGH ORDER ADDRESS |

In the halt condition, to instruct the Data Handler to run the above program you would simply load the low order address of your program starting location into the first location of the initialize vector (FFFC), and the high order address into the second location of the initialize vector (FFFD), shown below.

Our loop program starts at FCOO so

So we load;

| ADDRESS | DATA |       |       |          |

|---------|------|-------|-------|----------|

| FFFC    | -00  | (low  | order | address) |

| FFFD    | -FC  | (high | order | address) |

To get the Data Handler to begin execution of our loop program press INT, begin pressing SC and watch the Data Handler step through the initialize process (6 steps). It will step to the initialize vectors (FFFC, and FFFD) and arrive at its new starting address FCOO which should be displayed on the address display. If your address is displaying OOFC you loaded your low and high order address backwards, if so go back and try again.

If you arrive at the correct address (FCOO), continue to single cycle through your loop. If you are convinced that it is looping properly you can discontinue "walking" through and let it free run by pressing RN. The Data Handler is now executing your loop program.

You will notice that the Data Handler continuously displays the exact data that we loaded in our loop program. Excellent! It's running our program exactly as we wrote it. We instructed it to perform two NOP's (EA, no operations) and then JMP (4C, jump to a new starting location) to begin execution of new data, which as we planned it turned out to be the same program we left. Very cleaver is this program, this could be the basis for some sort of keyboard monitor or other program that looped while waiting for an interrupt from an external device (possibly connected onto our input port).

#### SYSTEM EXPANSION:

The Data Handler address, data, and control lines exit the P.C.B. by way of two rows of fifty pads on the rear left portion of the Data Handler P.C.B..

These bus lines are pin for pin compatable, and driver/receiver matched with the 8800 Altair/IMSAI microcomputer peripherals.

Limited system expansion may be achieved with the addition of a 100 pin connector on the bus line pads on the left rear portion of the Data Handler P.C.B. and the installation of any particular 8800 Altair/IMSAI type of peripheral board which fits the individual need.

Larger system expansion may be accomplished with the use of an Altair type mother board or a suitable card cage setup mounted next to the Data Handler P.C.B. with the bus lines connected to the mother board with ribbon cable. Another excellent choice would be the hard wire mounting of an Altair expander board directly perpindicular below the Data Handler P.C.B.. This would enable the use of more than one peripheral board.

The Data Handler may be used with a power supply greater than +5 volts D.C. when it is configured in such a manner as to incorporate the mounting of a +5 volt 5A regulator on the P.C.B.. The left rear part of the P.C.B. directly adjacent to the bus line pads, is laid out to accept a TO-3 78HO5, or LM 323, (+5 volts @ 5 amps) type regulator.

#### SYSTEM EXPANSION:

This regulator configuration is ideal when used with an Altair type (+8 volts) power supply to provide power for peripheral boards of the 8800 Altair/IMSAI type. Note that these peripherals were designed to be powered by +8 volts with regulators dropping the voltage to +5 volts on each individual board, however, jumpers may be used in place of these regulators and a +5 volt power supply may be incorporated.

The Data Handler L.E.D. displays are driven directly from the address and data bus lines. When the system is expanded to a large degree it is suggested that a video type peripheral be added, or that the L.E.D.'s be buffered, or seven segment displays added to prevent over loading of these bus lines.

\*Note\* that with the tremendous popularity towards 8800 Altair/IMSAI type peripherals there will be an increasingly large number of them available in the future and the possibility exists that some of them will not immediately work with the Data Handler.

\*If this happens, we ask that we be contacted at Western Data Systems (408) 984-7804 so that we may investigate and resolve the problem.

DO NOT ASSEMBLE BEFORE READING COMPLETELY

#### PRE-ASSEMBLY NOTES:

(READ CAREFULLY)

- consists of mounting components to the board. The parts location list (see index) contains lettering identifying where the components are to be mounted on the board along with their proper position and direction. We recommend that you mount the components in groups, such as the integrated circuits, then the resistors, and then the capacitors. A step by step assembly procedure is provided for each major group of components.

- 2. The Data Handler printed circuit board is industrial grade, double sided, with plated through holes. This means that in a number of locations, the foil paths on the top of the board are connected to the foil paths on the bottom through holes which have plating on the inside. This plated through technique means you don't have to solder common foil areas on both sides. Soldering on the bottom side of the P.C.B. only normally will be adequate.

(\*NOTE- DO NOT USE ACID-CORE SOLDER)

#### PRE-ASSEMBLY NOTES:

- 3. Due to the small foil around the printed circuit board holes and the small areas between the foil traces, you will have to use utmost care to prevent solder bridges between adjacent foil areas. Use only a low-wattage soldering iron with a small tip. Do not use a soldering gun. Keep the tip of your soldering iron clean (frequently wipe the tip on a damp clothe or solder sponge ) and lightly coated with solder.

- 4. The Data Handler kit contains (8) 16 pin I.C. sockets, for the 2102 memory, and 1 40 pin I.C. socket for the 6502 microprocessor. Sockets may be used for all the I.C.'s. However, for system reliability sake they are not recommended.

- 5. The side with the name Data Handler is the side on which all the components are to be loaded. (component side)

- 6. On all I.C.'s facing the rear of the P.C.R., pin 1 is the left rear pin (denoted by the clipped pad on the P.C.R.) The microprocessor (E7), and the 8212's (E12, and E16) face to the left with pin 1 located on the front left row of pins (denoted by clipped pad on the P.C.B.).

- 7. I.C. B7 is the only one mounted with pin number one to the right rear facing toward the keyboard switches.

DOT OR INDENTATION

#### PRE-ASSEMBLY NOTES:

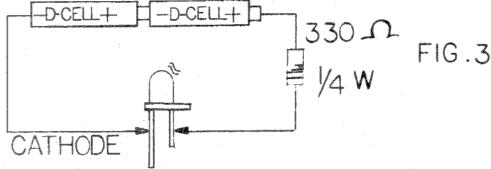

8. When installing the L.E.D.'s be absolutely sure of their polarity <u>before</u> installation. (See figure 3)

Test them first if necessary, but be sure. The base of the L.E.D. contains a small notch or flat area, this denotes the cathode of the L.E.D. as the lead closest to the flat area.

9. The cathode is to be connected to ground on all of the L.E.D.'s. On M4 thru M27 the cathodes face the front of the P.C.B., on M1, M2, and M3 they face toward the keyboard.

#### CAUTION\*

#### ASSEMBLY INSTRUCTIONS:

- 1.() With the P.C.B. component side up (see preassembly note 5). Insert and solder pins 1 and 9 of the memory I.C. sockets (D1 thru D8) on the P.C.B..

- 2.() Insert the microprocessor socket and tack solder the corner pins (1 & 21) onto the P.C.B..

- 3.() Referring to the component layout diagram, open one package at a time, and tack solder the corner pins on all the I.C.'s except B7 onto the P.C.B..

Do not install the memory I.C.'s or the microprocessor in their sockets yet.

- 4.() Install I.C. B7 according to preassembly note 7.

- 5.() Check all I.C.'s and sockets for alignment, full insertion, bent under pins, and orientation (is B7 correct?).

- 6.() With all the I.C.'s being correct, go back and finish soldering all the I.C. pins. Make sure of good clean solder joints, and lack of solder bridges.

- 7.() With all the I.C. sockets being correctly orientated, solder all the pins as in step (6).

- 8.() Again referring to your component layout diagram, open the package of resistors and istall them by groups in the following manner on the P.C.B.. Install the 4.7K ohm (yellow-violet-red) resistors in R1-R24 and solder in place.

- 9.() Insert R26-R51 (220 ohm, red-red-brown) and solder into place

- 10.() Insert R54-R64 (1K ohm, brown-black-red) and solder into place.

- 11.() Again referring to the components layout diagram insert and solder the remaining resistors along with the 50K ohm potentiometer (VR1).

- 12.() With the resistors properly in place, mount the capacitors being careful to observe proper polarity on the electrolytics C20, and C21. (Plus on the P.C.B. should correspond with the plus end on the capacitor) (Refer to component layout).

#### ASSEMBLY INSTRUCTIONS:

- 13.() Double check the placement, polarity alignment, ect. of the capacitors, and solder them into place. Trim (if needed) the excess lead length from these components from the underside of the board at this time.

- 14.() Insert the data L.E.D.'s M20 thru M27 (back row of 8 red L.E.D.'s) with the cathode (see preassembly notes). Toward the front edge of the P.C.B. (the long edge with numbers 1 thru 11 along it). Mount them all flush with the surface of the P.C.B. First solder one lead in place, then after making sure of their alignment and uniformity solder the other lead.

- 15.() Install the row of 16 red address L.E.D.'s M4 thru M19 using the procedure previously described (step 14) for the data L.E.D.'s (cathodes toward the fromt edge of the P.C.B.). Also mount them flush with the P.C.B. and solder into place.

- 16.() Install the red addr L.E.D. M2 and red data L.E.D. M3 (located just to the left of the keyboard). Mount them flush with the P.C.B. with their cathodes towards the keyboard, and solder into place.

- 17.() Insert the yellow L.E.D. (M1) in its place directly below M2. Mount it with the cathode toward the keyboard and it also flush with the P.C.B., with alignment being correct solder it into place making sure to produce good solder joints.

- 18.() Install any user provided P.C.B. edge connector (Altair bus type), crystal, connectors for the I/O ports or what have you at this time and solder into place. Turn the P.C.B. over and ensure that all component leads are clipped and properly soldered.

- 19.() The P.C.B. without the switches installed, may be cleaned of any flux, dirt ect at this time. At this point be careful not to let this sludge accumulate in the microprocessor or memory sockets. There are special chemicals available for cleaning P.C.B.'s (freon TF, flux solvent, M.E.K. ect) but they should be used with proper ventilation. If the keyboard switches are already installed be extremely careful about keeping this flux remover off of them, as it could result in destroying the switches. It is recommended that you remove the switches before the board is cleaned.

#### ASSEMBLY INSTRUCTIONS:

- 20.() Install the 26 keyboard switches one at a time soldering them from the bottom side when alignment, placement, and registration are verified with the component layout diagram.

- 21.() At this time insert the Data Handler P.C.B. into the top track of the Data Handler P.C.B. case.

- 22.() Connect and solder the wires from the user supplied power supply (plus 5 volts D.C., producing a minimum of 1.8 amps). The Data Handler requires only a plus 5 volts for power, however, consult the system expansion section (7) for other power configurations.

- 23.() Turn power to the Data Handler on at this time and quickly look around the P.C.B. and check for smoke, excessive heat or any abnormality. If any abnormality is found procede immediately to smoke, heat, and abnormalities in the system checkout section.

- 24.() If a D.C. volt meter is available check for the plus 5 volts at pin 8 on the microprocessor socket and ground (0 volts) at pin 1. If a meter is not available wait an extra moment to ensure that an abnormality will not suddenly pop up later on.

- 25.() All steps being valid up to now, turn off the 5 volt supply to the Data Handler and install the memory I.C.'s into their sockets. Install the microprocessor into its socket (read how in the preassembly notes) being careful to use the correct pin number 1 for the registration.

- 26.() Ready to turn the power on? wait, once more check that the memory I.C.'s and the microprocessor are properly in place according to the component layout diagram.

- 27.() 0,K. turn the power on and procede to the system checkout section.

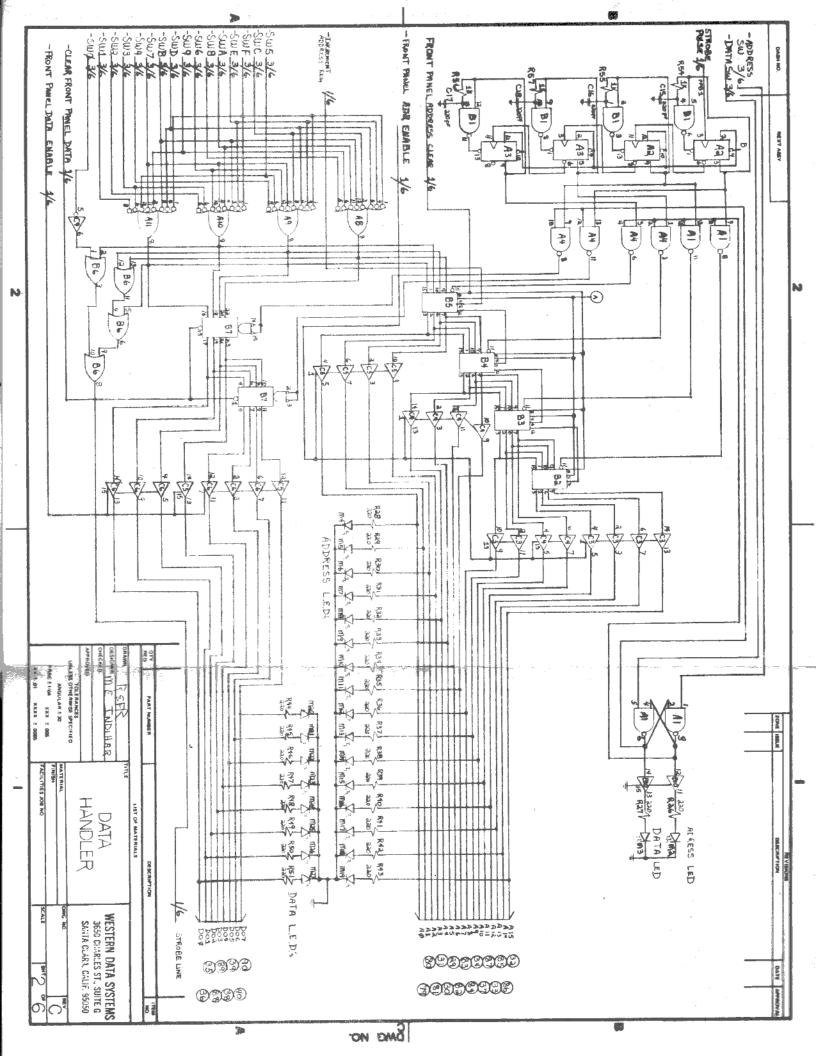

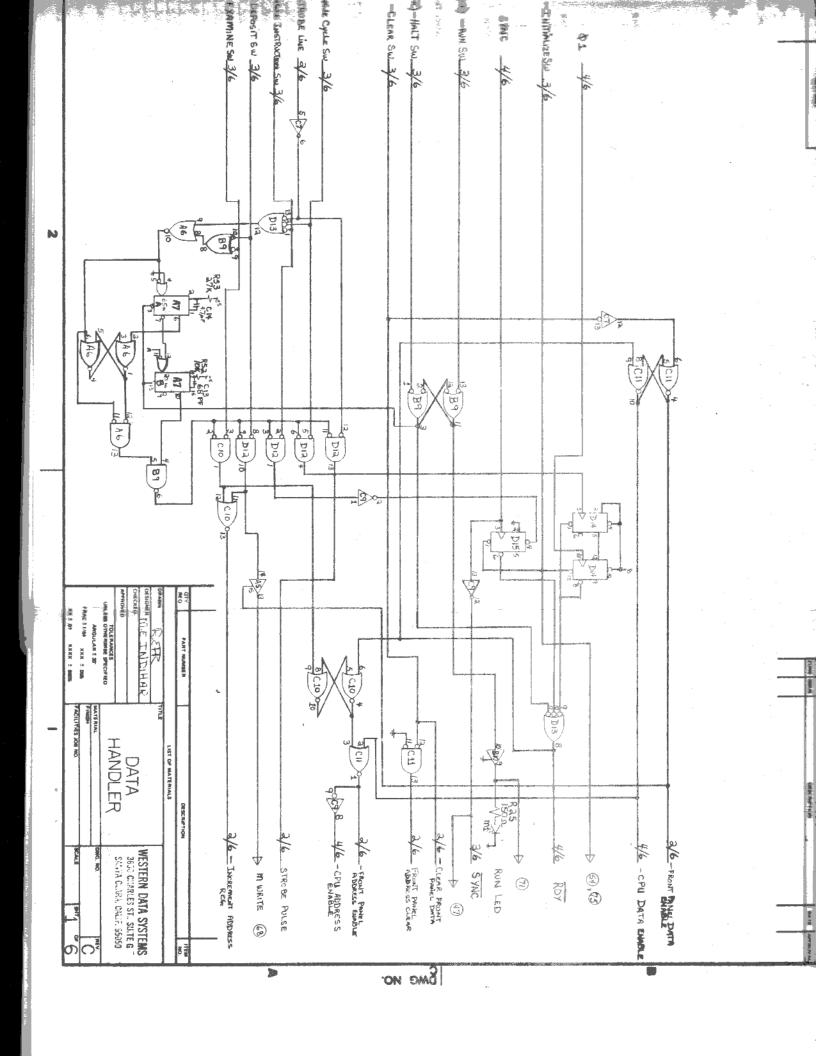

\*The following is a detailed theory of operation of the of the complete Data Handler and its associated circuitry. Refer to the schematic diagrams and the block diagram while reading this theory.

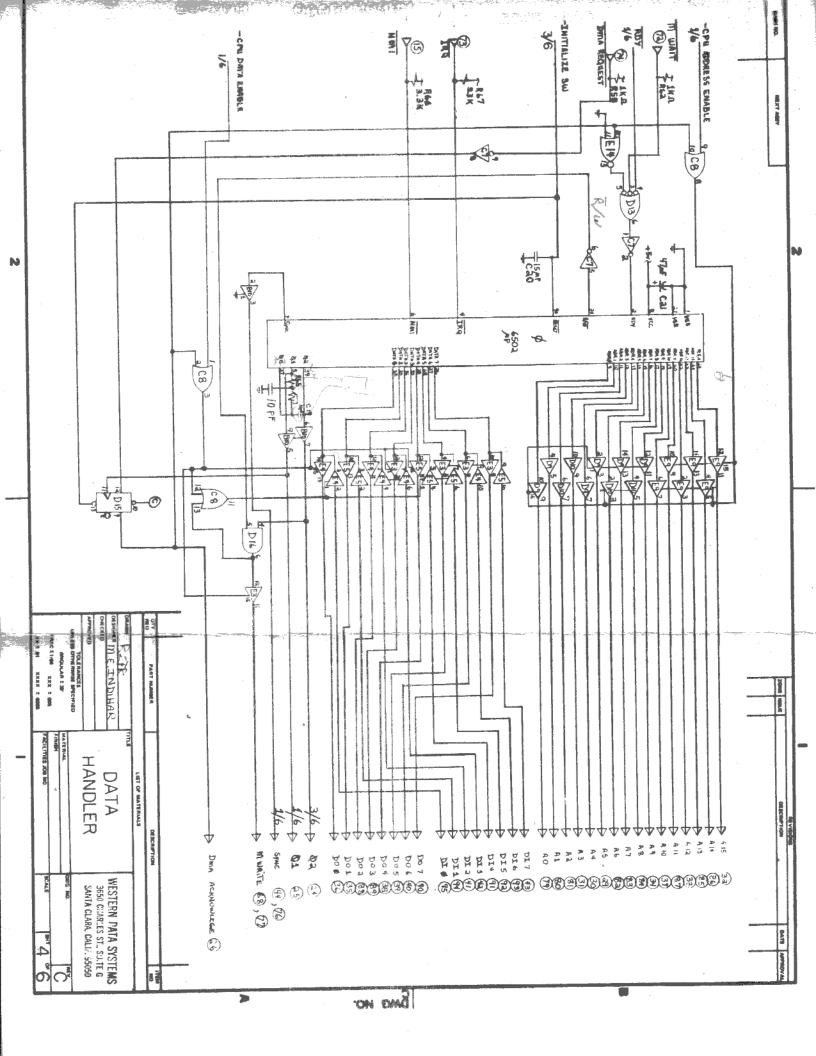

#### KEYBOARD:

The complete keyboard control is accomplished with the 10 control keyswitches, and the 16 data/address entry keyswitches (3 of 6). The set of 16 data/address entry keyswitches are hardware hex encoded by A8 thru A11 (2 of 6) and "switch sensed" by B6 (2 of 6). I.C. B6 sends a "switch sensed" strobe line signal to the one shot keyswitch debounce circuitry made up of A7, and A6 (1 of 6) which then is decoded by D12 (1 of 6) as being a strobe pulse from one of the 16 possible keyswitches.

#### **FUNCTION GENERATOR:**

The strobe pulse from the debounce circuitry activates a four pulse function generator formed from B1,A2, and A3 (2 of 6) and is mode decoded (address mode or data mode) by A4 and the second half of A1 (2 of 6). These 4 address pulses or 2 data pulses then latch (B7 for data and B2-B5 for address) the hexadecimal encoded data presently being displayed thru A8-A11 (2 of 6) by any-one of the 16 possible keyswitches.

#### ADDRESS/DATA ENTRY MODE:

Two control keyswitches (3 of 6) control the entry mode of the front panel. The entry mode is selected by either the DA (data) or AD (address) switches. This switch information sets or resets the RS latch formed from the first half of A1 (2 of 6) and decodes the function generator pulses as being either address or data loading pulses. The state of this RS latch is displayed on L.E.D.'s M2 and M3 (2 of 6) and can be changed at anytime.

#### SINGLE CYCLE AND SINGLE INSTRUCTION:

The SC (single cycle) and SI (single instruction) control keyswitches are debounced by A7 and A6 (1 of 6), and decoded by half of I.C. D12 (1 of 6). The debounced keystroke pulse from the SI (single instruction) keyswitch sets the D15 (1 of 6) flip-flop which in turn allows the RDY line on the 6502 microprocessor to go to the high state. This enables the Data Handler to run until the D15 (1 of 6) flip-flop receives a sync pulse (stat of new instruction) from the 6502 at which time D15 (1 of 6) resets and thru D13 (1 of 6) halts system operation. The SC (single cycle) keyswitch is debounced and wired to RDY in the same way as is the single instruction, however it allows the Data Handler to run only from the start of a \$1 cycle to the start of the next \$1 cycle in which D14 (1 of 6) is reset and system operation is halted.

#### CLEAR:

The CL (clear) switch accomplishes two functions when it is actuated.

- (1) It resets the RS latch C11 (1 of 6) which gives control of the S-100 bus to the front panel.

- (2) It clears the front panel data (B7) and address (B2-B5) latches.

The CL, as is INT, HT,RN,AD, and DA switches are not debounced since they are primarily used to set and reset latches in the associated function circuitry of the Data Handler front panel.

#### RUN/HALT:

The RN (run) and HT (halt) keyswitches enable us to ultimately control the operation of the Data Handler. These switches either set or reset run latch B9 (1 of 6) which in turn will halt operation of the C.P.U.. The state of this run latch is displayed by L.E.D. M1 (1 of 6) which when lit indicates that the C.P.U. is running. Further more when in the run mode this run latch (B9) disables the debounce circuitry to kill any spurious oscillations which might lead to system noise.

#### INITIALIZE:

The INT (initialize) keyswitch serves to accomplish two functions;

- (1) It acts as an override to reset both the single instruction and single cycle circuitry.

- (2) It pulls the reset line low on the 6502 micro-processor (4 of 6) which initiates the initialization procedure for the Data Handler (see the operating instructions for further information).

#### BUS:

The S-100 bus is a UNI-directional bus which is the bulk work of the Data Handler. It is driven/received with tri-state buffers by both the front panel and the 6502 microprocessor. This bus drives the discreet L.E.D. display and connects the I/O ports, memory, 6502, front panel, and edge connector pads together.

#### SYSTEM CHECKOUT:

#### Smoke, heat, and abnormalities:

O.k., here you are with a problem, so lets be quick. None of the I.C.'s after 15 seconds (with power on), should be too hot to hold your finger on, so touch each one and remember which ones burned your finger. Turn the power off and check the hot (or smokey) I.C. for proper pin registration, alignment, solder blobs, a cut lead resting on the I.C. pins, ect. If I.C. B7 is hot chances are it's installed backwards. If all the I.C.'s are hot check the polarity of the power supply to the P.C.B., the polarity is either backwards (plus 5 volts is connected to ground on the P.C.B.), or the plus 5 volts is not actually plus 5 volts. If your power supply exhibited the smoke or abnormalities, chances are that there is a direct short on the P.C.B., this is easiest found with an ohm meter ( look for solder blobs, lead touching under the P.C.B., ect).

\*Consult the troubleshooting section for further information.

#### SYSTEM CHECKOUT:

#### NORMAL CHECKOUT:

- 1.() With the HT (halt) button pressed, turn on the power supply to the Data Handler. The Data Handler will come up with a random address on the 16 address L.E.D.'s and random data on the 8 data L.E.D.'s. Either the addr or data L.E.D (closest to the keyboard) will be on but not both, and the run L.E.D. (yellow L.E.D.) should not be on. This run L.E.D. indicates that the Data Handler is halted when not lit and running when it is on.

- 2.() Press the AD (address) switch, then the DA (data) switch. Ensure that the associated L.E.D. changes with each particular keystroke.

- 3.() Press CL (clear), the 16 addr and 8 data L.E.D.'s should go off.

- 4.() Press AD, now press the 1 key. The addr 0 L.E.D. should come on and stay on. This should be the only row L.E.D. on. Press the 2 key, the 1 should have shifted left into the next set of four digits and was replaced by the 2 entry. Sequentially enter the rest of the 16 keys. Ensure that the proper key data is entered into the right most set of four L.E.D.'s each time a key is pressed, verify that this keyswitch data is only entered once per keystroke.

- 5.() Press DA and sequentially enter all the 16 individual keys as in the previous step. Ensure that they enter the correct data row L.E.D.'s and shift left with each single keystroke.

- 6.() Enter all F's into both the address and data rows of L.E.D.'s. All the data and address (24 L.E.D.'s) L.E.D.'s should now be on. This test indicates dead or weak L.E.D.'s.

- 7.() With the Data Handler halted (press HT), press clear, press AD, press the 1 key. The address 0 L.E.D.(right most L.E.D. in the row) should come on. Press (deposit). The address row of L.E.D.'s should increment by one (base 16) each and every time DP is pressed.

#### SYSTEM CHECKOUT:

#### NORMAL\_CHECKOUT:

- 8.() Duplicate test 7 (on previous page). However, press the EX (examine) keyswitch in place of the DP keyswitch. The address row of L.E.D.'s should increment by one (base 16) and only one each time EX is pressed.

- 9.() Jump to the operating instructions section (section 6) and become familiar with the correct procedures for operating your Data Handler. The loop program at the end of section 6 will verify proper system operation.

DATA HANDI FR BLOCK DIAGRAM

#### TROUBLESHOOTING:

Before consulting the troubleshooting chart to solve a particular problem, do the following:

- (A) Give your Data Handler a complete visual inspection and ensure that all the I.C.'s are properly orientated and that the ones in the sockets are inserted sufficiently without bent-under, or out of socket pins.

- (B) Check for solder bridges, cut leads laying on or under the P.C.B., and any solder flakes that can possibly cause a short to the Data Handler.

- (C) If steps A & B failed to cure the problem list all visible symptoms and procede to the troubleshooting chart. Remember it is virtually impossible to troubleshoot a problem without proper knowledge of the symptoms.

#### TROUBLESHOOTING CHART

| SYMPTOM/INDICATION         | PROBABLE CAUSE                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (1) No lights (L.E.D.'s).  | <ol> <li>Major short on the P.C.B.</li> <li>Power supply dead.<br/>(check the +5 volts)</li> <li>L.E.D.'s installed back-wards.</li> </ol>                                                                                                                                                                                                      |

| (2) Lights (L.E.D.'s) dim. | <ol> <li>Insufficient voltage from power supply (4.5 volts to 5.5 volts)</li> <li>Insufficient current from power supply (1.8 amps min).</li> <li>Tri-state bus buffers bucking one another. Either the front panel buffers (C3-C6) should be on or the C.P.U. buffers (E3,E4,F5,D9,D10 but not both.</li> <li>S-100 bus is shorted.</li> </ol> |

#### TROUBLESHOOTING CHART

| AIN SECTION AND AND AND AND AND AND AND AND AND AN | SYMPTOM/INDICATION                                  | PROBABLE CAUSE                                                                                                                                                                                                         |

|----------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (3)                                                | Run L.E.D. not on or won't go off.                  | <ol> <li>Microprocessor clock not running.</li> <li>B9 not switching on switch contact.</li> <li>Run L.E.D. is dead.</li> </ol>                                                                                        |

| (4)                                                | Addr and data L.E.D.'s both on or won't switch off. | <ol> <li>One or both L.E.D.'s dead or installed backwards.</li> <li>A1 not switching.</li> <li>B10 not driving the L.E.D.'s</li> </ol>                                                                                 |

| (5)                                                | CL won't clear the addr and data L.E.D.'s.          | <ol> <li>The Data Handler is not in<br/>the halted mode.</li> <li>C11 not functioning properly.</li> </ol>                                                                                                             |

| (6)                                                | Incorrect data entered from front panel.            | <ol> <li>One or more dead L.E.D.'s (do test 6).</li> <li>A8-A11 not decoding properly.</li> <li>Front panel buffers (C3-C6) not providing drive or shorted.</li> <li>B6 is dead (check strobe line 2 of 6).</li> </ol> |

| (7)                                                | A keystroke enters more<br>than one character.      | <ol> <li>A7(A) runs too fast         (increase R53).</li> <li>Sticky keyswitch.</li> <li>Function generator (A2,A3,&amp;B1) functioning improperly.</li> </ol>                                                         |

| (8)                                                | Not able to enter any address or data digits.       | <ol> <li>A6,A7 debounce circuitry is dead.</li> <li>B6 is dead</li> <li>A8-A11-one or all indicate a false key closure.</li> <li>Stuck keyswitch.</li> </ol>                                                           |

\* Part numbers-Refer to I.C. locations (C3 is an I.C. location not capacitor C3 unless stated otherwise).

### TROUBLESHOOTING CHART

| SYMPTOM/INDICATION                         | PROBABLE CAUSE                                                                                                                                                                 |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (9) Unable to enter any data               | 1. Check the orientation of B7 (see preassembly note 7)                                                                                                                        |

| (10) EX or DP increment more than one 16.  | 1. A 7(A) runs too fast (increase R53). 2. Keyswitch sticky.                                                                                                                   |

| (11) Data Handler looses running sequence. | <ol> <li>Clock speed is too fast.</li> <li>Memory I.C. failure.</li> <li>Interrupt line (from input port) continuously held low.</li> <li>Memory I.C. in backwards.</li> </ol> |

| (12) C.P.U. won't run at all.              | <ol> <li>The 6502 (I.C.E7) installed backwards.</li> <li>VR1 broken or not installed.</li> </ol>                                                                               |

### (E15) (E16) ₩ 4 ≥ < 7400 - C 21 -(R56)--(R57)-82 N q -(R44) 8197 E3 83 COMPONENT C3 (7)C2) Œ (E) (R40)-- (R40)-E 4 C4 4 22 C 12 (F.39) 6 A S 05 202 65 8 C 20 TEXT + C 14 - (C 13) 8 66 88 90 ြင္မ ER36 € 7 6502 (R35)-2102 97 A < 67 ₹ P (1) (R321-B7 C5) C8D œD (F33)-68 2102 کی د 80 (R32)--[R66]--[R67]-<u>-(R58)</u>-C4) (S) 63 63 8 \$ 9 89 (R30)-(F) (R 29)ē d 8 © 0 8797 S. 8 (R26)-E c W1 W2 W3 7402 **C9** R64 1 RS 2 RS E12 AD 2 RSI 013 DA SC -[R62]-4 $\infty$ C 20 Z C 2 4 EX 2 0 Ç 9 5 프 R E 16 m 0 Þ N (CO) 1A 2A D16 Ñ 무 æ П W 7 -[R61]--[R60]-

٧R١

B B B B B B B B 2A 2A 3A 6A 8A 2A 1A

### THE DATA HANDLER

# I.C. LOCATION/PARTS LIST

| A1-<br>A2-<br>A3-<br>A4-<br>A5-<br>A6-<br>A7-<br>A8-<br>A9-<br>A10-<br>A11- | 7400<br>7474<br>7474<br>7400<br>8T97<br>7402<br>9602<br>7430<br>7430<br>7430 | D8 -<br>D9 -<br>D10 -<br>D11 -<br>D12 -<br>D13 -<br>D14 -<br>D15 -<br>D16 - | 2102<br>8T97<br>8T97<br>SPARE<br>7402<br>7410<br>7474<br>7474<br>7474                     | 4 -<br>5 -<br>2 -<br>1 -<br>1 -<br>7 -<br>2 -<br>4 -<br>1 -<br>4 -<br>2 - | 7400<br>7402<br>7404<br>7408<br>7410<br>7430<br>7432<br>7474<br>74116 (93116-9308)<br>74193<br>8212 (748412) |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| B1 -<br>B2 -<br>B3 -<br>B4 -<br>B5 -                                        | 7400<br>74193<br>74193<br>74193<br>74193                                     | E2 -<br>F3 -<br>F4 -<br>E5 -<br>E7 -<br>E9 -                                | 8T97<br>8T97<br>8T97<br>8T97<br>6502<br>8T97                                              | 13-<br>1-<br>8-<br>1-                                                     | 8T97 (8097-74367)<br>9602<br>2102<br>6502 MP                                                                 |

| B6-<br>B7-<br>B9-<br>B10-                                                   | 7432<br>74116<br>7400<br>8T97                                                | E10 -<br>E11 -<br>E12 -<br>E14 -<br>E15 -                                   | 7430<br>7430<br>8212<br>7402<br>8212                                                      | 1-10M<br>1-4.7<br>120                                                     |                                                                                                              |

| C1 -<br>C2 -<br>C3 -<br>C4 -<br>C5 -<br>C6 -<br>C7 -<br>C8 -<br>C9 -        | SPARE<br>SPARE<br>8T97<br>8T97<br>8T97<br>7404<br>7432<br>7404               | R25<br>R26-R51<br>R52-R61<br>R53<br>R54-R64<br>R66-R61                      | 4.7K ohm<br>150 ohm<br>1220 ohm<br>510K ohm<br>27K ohm<br>41K ohm<br>73.3K ohm<br>50K ohm | 4-220<br>1-68P<br>1-10P<br>1-27K<br>1-50K<br>2-10K                        | F F RESISTORS ohm ohm TRIMPOT                                                                                |

| C10-<br>C11-<br>D1-<br>D2-<br>D3-<br>D4-<br>D5-<br>D6-                      | 7402<br>7402<br>2102<br>2102<br>2102<br>2102<br>2102<br>2102                 | C1-C12<br>C13<br>C14<br>C15-C18<br>C19                                      | (TRIMPOT)01MF68PF4.7MF 8220PF10PF                                                         | 24-4.<br>2-3.3<br>11-1K<br>26-22<br>1-150                                 | 7K ohm<br>K ohm<br>ohm<br>O ohm                                                                              |

<sup>\*</sup> ALL RESISTORS ARE %W UNLESS OTHERWISE NOTED \*

\*CONSULT THE MOS TECHNOLOGY 65XX PROGRAMING MANUAL FOR USE OF THE FOLLOWING INSTRUCTION LIST AND FURTHER INFORMATION.

INSTRUCTION LIST

ALPHABETIC BY MNEMONIC

WITH OP CODES, EXECUTION CYCLES

AND MEMORY REQUIREMENTS

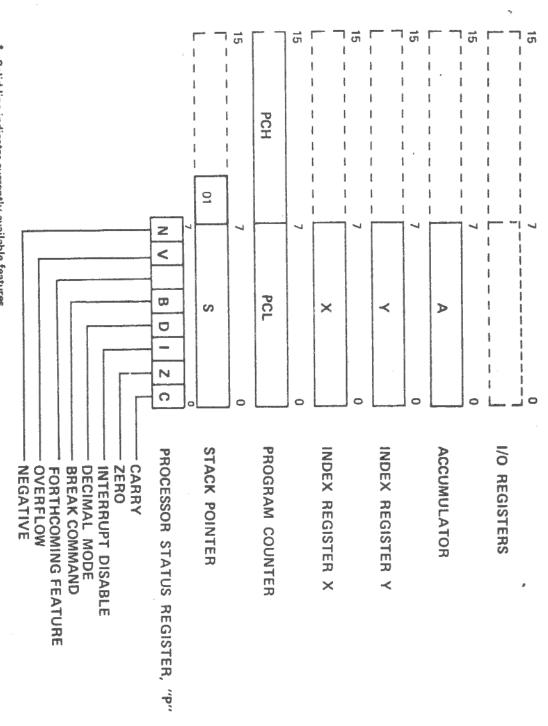

# PROGRAMMING MODEL MCS650X

Solid line indicates currently available features

Dashed line indicates forthcoming members of family

The following notation applies to this summary:

| A        | Accumulator               |

|----------|---------------------------|

| Х, Ү     | Index Registers           |

| М .      | Memory                    |

| P        | Processor Status Register |

| S        | Stack Register            |

| ✓        | Change                    |

|          | No Change                 |

| +        | Add                       |

| $\wedge$ | Logical AND               |

| -        | Subtract                  |

| ₩        | Logical Exclusive Or      |

| <b>†</b> | Transfer from Stack       |

| <b>†</b> | Transfer to Stack         |

| <b>→</b> | Transfer to               |

| <b>←</b> | Transfer to               |

| V        | Logical OR                |

| PC       | Program Counter           |

| PCH      | Program Counter High      |

| PCL      | Program Counter Low       |

| OPER     | OPERAND                   |

| #        | IMMEDIATE ADDRESSING MODE |

Note: At the top of each table is located in parentheses a reference number (Ref: XX) which directs the user to that Section in the MCS6500 Microcomputer Family Programming Manual in which the instruction is defined and discussed.

INSTRUCTION ADDRESSING MODES AND

RELATED

**EXECUTION TIMES**

(in clock cycles)

| * Add                                     | JMP | NY  | X   | Z C | EOR | UEY | ) (X | DEC   | СРУ  | CPX | CMF | CLV | CL  | CLD | CLC | SAB | BVC      | BIX | 97  | BNE        | BMI | BIT | BEQ | BCS | BCC | ASL | AND      | ADC     |

|-------------------------------------------|-----|-----|-----|-----|-----|-----|------|-------|------|-----|-----|-----|-----|-----|-----|-----|----------|-----|-----|------------|-----|-----|-----|-----|-----|-----|----------|---------|

| one                                       |     |     |     |     |     | ٠   |      |       |      |     |     |     |     |     |     | ٠   |          |     |     |            |     |     |     |     |     | 2   | -        |         |

| cycle<br>cycle                            | •   | -   | ٠   | ٠   | N   | *   |      | •     | Ŋ    | 2   | N   | -   | ٠   | •   |     |     | ٠        | 4   |     |            | ٠   | ٠   |     | •   |     |     | Ŋ        | N       |

|                                           |     | •   | •   | G   | L   |     | •    | ທ     | ω    | w   | w   | -   | •   | •   | •   | •   | •        | •   | ٠   | •          | •   | డు  | ٠   | ٠   |     | ហ   | ယ        | ω       |

| ===                                       | •   | •   | •   | 0   | 4   | •   | ٠    | (C)   | -    | ٠   | 4   | *   | •   | •   | •   | ٠   | ۰        | -   | •   | ٠          | •   |     |     | ٠   |     | Ö   | ₽        | 4       |

| indexing<br>branch is                     | •   | •   | ٠   |     | •   | *   | ٠    | •     | •    |     |     | ٠   | ٠   | ٠   |     | •   | ٠        | 4   | •   |            |     | ٠   |     |     |     |     |          |         |

| ching                                     | ω.  |     |     | о   | 4   |     |      | 0     | 4    | 4   | 4   | •   | •   | •   | •   | ٠   | •        | •   | •   | •          | ٠   | 4   | •   | *   | *   | 6   | 4        | 4       |

| en en                                     |     | •   |     | 7   | *   | •   | •    | 7     |      | •   | *   | •   | •   | •   | •   | •   | •        | •   | •   | •          | •   | *   | •   | •   | •   | 7   | 4        | 4       |

| across<br>taken,                          | •   | •   | •   | •   | *   | ٠.  | •    | •     | •    | •   | 4   | •   | •   | *   | •   | •   | ٠        | •   | •   | •          | •   | ٠   | •   | •   | ٠   |     | 4        | 4       |

| 3 %                                       | •   | 2   | 1   |     | •   | N   | N    | -     | •    | •   | •   | 2   | N   | N   | 2   | •   | •        |     | •   | •          |     | ,   | -   |     | -   | ٠   | -        | •       |

| page t                                    |     |     |     |     | D   |     |      |       |      |     |     |     |     |     |     | 2** | N#<br>** |     | 2** | <b>1</b> 2 | **  |     | 2** | 2** | 2*  |     |          |         |

| boundary<br>one add                       |     |     |     |     | ຫ   |     |      |       |      |     | en  |     |     |     |     |     |          |     |     |            | ,   |     |     |     |     |     | o<br>    | 0       |

| ë 5                                       | රා  |     |     |     |     |     |      |       |      | ,   | .*  |     |     |     |     |     |          |     |     |            |     |     |     |     |     |     | ហ្<br>*  | Sī<br>* |

| itional if                                |     | TYA | TXS | AXT | TSX | TAY | TAX  | STY** | *XTS | STA | SEI | SED | SEC | SBC | RTS | RTI | ROL      | PLP | PLA | PHP        | PHA | ORA | NOP | LSR | LDY | LDX | LDA      | R       |

| ran                                       |     |     |     |     |     |     |      |       | •    |     |     |     |     |     |     |     | 2        |     |     |            | ,   |     |     | 2   | 4   |     |          |         |

| in in                                     |     | *   | ٠   |     |     | •   | •    |       | •    |     |     |     |     | N   |     | -   |          |     |     | -          |     | N   | -   |     | Ŋ   | N   | 2        |         |

| Č.                                        |     | •   | •   |     | -   | •   | -    | ω     | ယ    | ယ   |     | •   | •   | ယ   |     |     | Çŋ       |     |     |            |     | ω   |     | ÇT  | w   | u   | w        |         |

| Ďe                                        |     | •   | •   | -   |     | •   | •    | 4     | +    | 4   |     |     |     | 4   |     | -   | G        | *   |     | ٠          | -   | 4   | -   | ග   | 4   |     | 4        |         |

| ati.                                      |     | -   | -   | •   | •   | •   |      | •     | 4    |     |     | •   |     |     |     |     |          |     |     | -          |     | -   | -   |     |     | 4   |          |         |

| 3                                         |     | -   | •   |     |     | •   | •    | 4     | 4    | 4   |     | -   |     | 4   |     | . , | 0        |     |     |            |     | 4   |     | 0   | 4   | 4   | 4        | 6       |

| cros                                      |     | *   | •   | •   | •   | •   | •    | -     | -    | ហ   | •   | •   |     | 4   | •   |     | 7        |     |     |            |     | 4   |     | 7   | 4   |     | 4        |         |

| 29                                        |     | •   | -   | •   |     | •   |      | *     | • (  | (Jī | •   | •   | •   | 4   |     | •   | •        | ,   | ٠   |            |     | 4   | +   | -   | -   | 4   | 4        |         |

| pag                                       |     | 2   | N   | N   | N   | N   | 2    |       |      | ,   | N   | N   | Ŋ   | •   | O   | 6   | •        | 4   | 4   | u          | w.  |     | N   |     | *   |     |          | ٠.      |

| D.                                        |     |     |     |     |     | •   | •    |       |      | _   |     |     |     |     |     | -   | -        |     |     |            |     |     |     |     |     |     |          |         |

| ğ                                         |     |     | •   | •   |     |     | •    | •     | . (  | σ,  |     |     | '   | ဌာ  |     |     |          | ۰   |     |            | . 4 | 9   | •   |     |     |     | 0        | .       |

|                                           |     |     |     |     |     |     |      |       |      | B . |     |     |     |     |     |     |          |     |     |            |     |     |     |     |     |     |          | . 1     |

| branching operation crosses page boundary |     |     |     |     |     |     |      |       |      |     |     |     |     | *   |     |     |          |     |     |            |     | *   |     |     |     |     | <u>ٿ</u> |         |

Accumulator

Immediate

Zero Page

Zero Page, X

Zero Page, Y

Absolute

Absolute, X

Absolute, Y

Implied

Relative

(Indirect, X)

(Indirect), Y

Absolute Indirect

Accumulator

Immediate

Zero Page

Zero Page, X

Zero Page, Y

Absolute

Absolute, X

Absolute, Y

Implied

Relative

(Indirect, X)

(Indirect),Y

Absolute Indirect

AN

Logi Oper

**ADC**

Operation:  $A + M + C \rightarrow A$ , C

NZCIDV

(Ref: 2.2.1)

√ √ √ - - √

| Addressing<br>Mode | Assemb | oly Language · Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|--------|---------------------|------------|--------------|---------------|

| Immediate          | ADC    | # Oper              | 69         | 2            | 2             |

| Zero Page          | ADC    | Oper                | 65         | 2            | 3             |

| Zero Page, X       | ADC    | Oper, X             | 75         | 2            | 4             |

| Absolute           | ADC    | Oper                | 6D         | 3            | 4             |

| Absolute, X        | ADC    | Oper, X             | 70         | 3 .          | 4*            |

| Absolute, Y        | ADC    | Oper, Y             | 79         | 3            | 4*            |

| (Indirect, X)      | ADC    | (Oper, X)           | 61         | 2            | 6             |

| (Indirect), Y      | ADC    | (Oper), Y           | 71         | 2            | 5*            |

<sup>\*</sup> Add 1 if page boundary is crossed.

## AND

"AND" memory with accumulator

AND

Logical AND to the accumulator

Operation:  $A \land M \rightarrow A$

NZCIDV

(Ref: 2.2.3.0)

V V - - - -

| Addressing<br>Mode | Assemb | oly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|--------|----------------------|------------|--------------|---------------|

| Immediate          | AND    | # Oper               | 29         | 2            | 2             |

| Zero Page          | AND    | Oper                 | 25         | 2            | 3             |

| Zero Page, X       | AND    | Oper, X              | 35         | 2            | 4             |

| Absolute           | AND    | Oper                 | 2D         | 3            | 4             |

| Absolute, X        | AND    | Oper, X              | 3D         | 3            | 4*            |

| Absolute, Y        | AÑD    | Oper, Y              | 39         | 3            | 4*            |

| (Indirect, X)      | AND    | (Oper, X)            | 21         | 2            | 6             |

| (Indirect), Y      | AND    | (Oper), Y            | 31         | 2            | 5             |

<sup>\*</sup> Add l if page boundary is crossed.

**ASL**

Operation:  $C \leftarrow \boxed{76543210} \leftarrow \emptyset$

N Z C I D V

(Ref: 10.2)

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Accumulator        | ASL A                     | ØA         | 1            | 2             |

| Zero Page          | ASL Oper                  | Ø6         | 2            | 5             |

| Zero Page, X       | ASL Oper, X               | 16         | 2            | 6             |

| Absolute           | ASL Oper                  | ØE         | 3            | 6             |

| Absolute, X        | ASL Oper, X               | 1E         | 3            | 7             |

BCC

BCC Branch on Carry Clear

BCC

Operation: Branch on  $C = \emptyset$

NZCIDV

(Ref: 4.1.1.3)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Relative   | BCC Oper          | 9Ø   | 2     | 2*     |

<sup>\*</sup> Add 1 if branch occurs to same page.

<sup>\*</sup> Add 2 if branch occurs to different page.

Operation: Branch on C = 1

NZCIDV

NZCIDV

(Ref: 4.1.1.4)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Relative   | BCS Oper          | вø   | 2     | 2*     |

- \* Add 1 if branch occurs to same page.

- \* Add 2 if branch occurs to next page.

BEQ

BEQ Branch on result zero

BEQ

Operation: Branch on Z = 1

(Ref: 4.1.1.5)

Addressing Mode Assembly Language CODE Bytes Cycles

Relative BEQ Oper FØ 2 2\*

- \* Add 1 if branch occurs to same page.

- \* Add 2 if branch occurs to next page.

Operation: A  $\wedge$  M, M<sub>7</sub>  $\rightarrow$  N, M<sub>6</sub>  $\rightarrow$  V

Bit 6 and 7 are transferred to the status register. N  $\pm$  C I D V If the result of A  $\wedge$  M is zero then Z = 1, otherwise  $M_7 \sqrt{---M_6}$

$Z = \emptyset$

(Ref: 4.2.1.1)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Zero Page  | BIT Oper          | 24   | 2     | 3      |

| Absolute   | BIT Oper          | 2C   |       | 4      |

BMI Branch on result minus

BMI

Operation: Branch on N = 1

NZCIDV

(Ref: 4.1.1.1)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Relative   | BMI Oper          | 3Ø   | 2 .   | 2*     |

<sup>\*</sup> Add 1 if branch occurs to same page.

<sup>\*</sup> Add 2 if branch occurs to different page.

BNE

Operation: Branch on Z = 0

NZCIDV

(Ref: 4.1.1.6)

| Addressing | Assembly Language Form | OP   | No.   | No.    |

|------------|------------------------|------|-------|--------|

| Mode       |                        | CODE | Bytes | Cycles |

| Relative   | BNE Oper               | DØ . | 2     | 2*     |

<sup>\*</sup> Add 1 if branch occurs to same page.

BPL

BPL Branch on result plus

BPL

Operation: Branch on N =  $\emptyset$

NZCIDV

(Ref: 4.1.1.2)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Relative   | BPL Oper          | 10   | 2     | 2*     |

<sup>\*</sup> Add 1 if branch occurs to same page.

<sup>\*</sup> Add 2 if branch occurs to different page.

<sup>\*</sup> Add 2 if branch occurs to different page.

BRK

BRK Force Break

BRK

Operation: Forced Interrupt PC + P +

N Z C I D V --- 1 ---

(Ref: 9.11)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | BRK               | ØØ   | 1     | 7      |

1. A BRK command cannot be masked by setting I.

BVC

BVC Branch on overflow clear

BVC

Operation: Branch on V = 0

NZCIDV

(Ref: 4.1.1.8)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Relative   | BVC Oper          | 5Ø   | 2     | 2*     |

$<sup>\</sup>star$  Add 1 if branch occurs to same page.

<sup>\*</sup> Add 2 if branch occurs to different page.

BVS

Operation: Branch on V = 1

NZCIDV

(Ref: 4.1.1.7)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Relative   | BVS Oper          | 7Ø   | 2     | 2*     |

- \* Add 1 if branch occurs to same page.

- \* Add 2 if branch occurs to different page.

CLC

CLC Clear carry flag

CLC

Operation:  $\emptyset \rightarrow C$

NZCIDV

-- Ø ---

(Ref: 3.0.2)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | CLC               | 18   | 1     | 2      |

CLD

CLD Clear decimal mode

CLD

Operation:  $\emptyset \rightarrow D$

$N \neq C I D V$

---- ø -

(Ref: 3.3.2)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | CLD               | D8   | 1     | 2      |

CLI

CLI Clear interrupt disable bit

CLI

Operation:  $\emptyset \rightarrow I$

NZCIDV

(Ref: 3.2.2)

\_ \_ \_ Ø \_ \_ \_

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | CLI               | 58   | 1     | 2      |

CLV

CLV Clear overflow flag

CLA

Operation:  $\emptyset \rightarrow V$

NZCIDV

\_\_\_\_

(Ref: 3.6.1)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | , CLV             | В8   | 1     | 2      |

CMP

CMP Compare memory and accumulator

**CMP**

Operation: A - M

N Z C I D V

(Ref: 4.2.1)

V V V ---

| Addressing<br>Mode | Assembly Language<br>Form | OP   | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------|--------------|---------------|

| Immediate          | CMP #Oper                 | C9   | 2            | 2             |

| Zero Page          | CMP Oper                  | C5   | 2            | 3             |

| Zero Page, X       | CMP Oper, X               | D5   | 2            | 4.            |

| Absolute           | CMP Oper                  | CD   | 3            | 4             |

| Absolute, X        | CMP Oper, X               | DD   | 3            | 4*            |

| Absolute, Y        | CMP Oper, Y               | . D9 | 3            | 4*            |

| (Indirect, X)      | CMP (Oper, X)             | C1   | 2            | 6             |

| (Indirect), Y      | CMP (Oper), Y             | D1   | 2            | 5*            |

$<sup>\</sup>ensuremath{\text{*}}$  Add 1 if page boundary is crossed.

Operation: X - M

N Z C I D V

(Ref: 7.8)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Immediate  | CPX #Oper         | EØ   | 2     | 2      |

| Zero Page  | CPX Oper          | E4   | 2     | 3      |

| Absolute   | CPX Oper          | EC   | 3     | 4      |

CPY

CPY Compare memory and index Y

**CPY**

Operation: Y - M

NZCIDV

√ √ √ ---

(Ref: 7.9)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Immediare  | CPY #Oper         | CØ   | 2 2 3 | 2      |

| Zero Page  | CPY Oper          | C4   |       | 3      |

| Absolute   | CPY Oper          | CC   |       | 4      |

DEC

DEC Decrement memory by one

DEC

Operation:  $M - 1 \rightarrow M$

N Z C I D V

/ / ----

(Ref: 10.7)

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Zero Page          | DEC Oper                  | C6         | 2            | 5             |

| Zero Page, X       | DEC Oper, X               | D6         | 2            | 6             |

| Absolute           | DEC Oper                  | CE         | 3            | 6             |

| Absolute, X        | DEC Oper, X               | DE         | 3            | /             |

DEX

**DEX** Decrement index X by one

DEX

Operation:  $X - 1 \rightarrow X$

NZCIDV

(Ref: 7.6)

/ / - - - -

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | DEX               | CA   | 1     | 2      |

DEY

**DEY** Decrement index Y by one

DEY

Operation:  $Y - 1 \rightarrow Y$

N Z C I D V

(Ref: 7.7)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | DEY               | 88   | 1     | 2      |

**EOR**

EOR "Exclusive—Or" memory with accumulator

EOR

Operation: A ♥ M → A

NZCIDV

(Ref: 2.2.3.2)

/ / - - - -

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Immediate          | EOR #Oper                 | 49         | 2            | 2             |

| Zero Page          | EOR Oper                  | 45         | 2            | 3             |

| Zero Page, X       | EOR Oper, X               | 55         | 2            | 4             |

| Absolute           | EOR Oper                  | 4D         | 3            | 4             |

| Absolute, X        | EOR Oper, X               | 5D         | 3            | 4*            |

| Absolute, Y        | EOR Oper, Y               | . 59       | 3            | 4*            |

| (Indirect, X)      | EOR (Oper, X)             | 41         | 2            | 6             |

| (Indirect),Y       | EOR (Oper), Y             | 51         | 2            | 5*            |

<sup>\*</sup> Add 1 if page boundary is crossed.

IN( Ope INC Increment memory by one

INC

Operation:  $M + 1 \rightarrow M$

$N \neq C I D V$

/ / \_ \_ \_ \_

(Ref: 10.6)

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Zero Page          | INC Oper                  | E6         | 2            | 5             |

| Zero Page, X       | INC Oper, X               | F6         | 2            | 6             |

| Absolute           | INC Oper                  | EE         | , 3          | 6             |

| Absolute, X        | INC Oper, X               | FE         | 3            | 7             |

INX

INX Increment Index X by one

INX

Operation:  $X + 1 \rightarrow X$

NZCIDV

1 1

(Ref: 7.4)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | INX               | E8   | 1     | 2      |

INY

INY Increment Index Y by one

INY

Operation:  $Y + 1 \rightarrow Y$

NZCIDV / / ----

(Ref: 7.5)

| OP   | No.   | No.    |

|------|-------|--------|

| CODE | Bytes | Cycles |

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | INY               | C8   | 1     | 2      |

**JMP**

JMP Jump to new location

Operation: (PC + 1)PCL

(PC + 2)PCH

(Ref: 4.0.2)

NZCIDV

Addressing Assembly Language OP No. No. Mode Form CODE Bytes Cycles Absolute JMP Oper 4C 3 3 Indirect JMP (Oper) 6C 3 5

**JSR**

JSR Jump to new location saving return address

**JSR**

Operation: PC + 2  $\downarrow$ , (PC + 1)  $\rightarrow$  PCL

N  $\mathbf{Z}$  C I D  $\mathbf{V}$

$(PC + 2) \rightarrow PCH$

\_\_\_\_\_

(Ref: 8.1)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Absolute   | JSR Oper          | 20   | 3     | 6      |

LDA

LDA Load accumulator with memory

LDA

Operation: M → A

N Z C I D V

(Ref: 2.1.1)

√ √ - - - **-**

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Immediate          | LDA # Oper                | A9         | 2            | 2             |

| Zero Page          | LDA Oper                  | A5         | 2            | 3             |

| Zero Page, X       | LDA Oper, X               | В5         | 2            | 4             |

| Absolute           | LDA Oper                  | AD         | 3            | 4             |

| Absolute, X        | LDA Oper, X               | BD         | 3            | 4*            |

| Absolute, Y        | LDA Oper, Y               | В9         | 3            | 4*            |

| (Indirect, X)      | LDA (Oper, X)             | A1         | 2            | 6             |

| (Indirect), Y      | LDA (Oper), Y             | B1         | 2            | 5*            |

$<sup>\</sup>ast$  Add 1 if page boundary is crossed.

Operation: M → X

NZCIDV

(Ref: 7.0)

/ / ----

| Addressing                                            | Assembly Language                                        | OP                         | No.       | No.                   |

|-------------------------------------------------------|----------------------------------------------------------|----------------------------|-----------|-----------------------|

| Mode                                                  | Form                                                     | CODE                       | Bytes     | Cycles                |

| Immediate Zero Page Zero Page, Y Absolute Absolute, Y | LDX # Oper  LDX Oper  LDX Oper, Y  LDX Oper  LDX Oper, Y | A2<br>A6<br>B6<br>AE<br>BE | 2 2 2 3 3 | 2<br>3<br>4<br>4<br>4 |

$<sup>\</sup>star$   $\,$  Add 1 when page boundary is crossed.

LDY

LDY Load index Y with memory

LDY

Operation:  $M \rightarrow Y$

N Z C I D V

(Ref: 7.1)

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Immediate          | LDY #Oper                 | AØ         | 2            | 2             |

| Zero Page          | LDY Oper                  | A4         | 2            | 3             |

| Zero Page, X       | LDY Oper, X               | В4         | 2            | 4             |

| Absolute           | LDY Oper                  | AC         | 3            | 4             |

| Absolute, X        | LDY Oper, X               | BC         | 3            | 4*            |

<sup>\*</sup> Add 1 when page boundary is crossed.

LSR

Operation:  $\emptyset \rightarrow 76543210$

N  $\Xi$  C I D V

Ø / / - - -

(Ref: 10.1)

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Accumulator        | LSR A                     | 4A         | 1            | 2             |

| Zero Page          | LSR Oper                  | 46         | 2            | 5             |

| Zero Page, X       | LSR Oper, X               | 56         | 2            | 6             |

| Absolute           | LSR Oper                  | 4E         | 3            | 6             |

| Absolute, X        | LSR Oper, X               | 5E         | 3.           | 7             |

|                    |                           | ,          |              |               |

NOP

NOP No operation

NOP

Operation: No Operation (2 cycles)

NZCIDV

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | NOP               | EA   | 1     | 2      |

ORA

ORA "OR" memory with accumulator

ORA

Operation: A V M  $\rightarrow$  A

NZCIDV

(Ref: 2.2.3.1)

/ / - - - -

| Addressing<br>Mode | Assembly Language<br>Form | OP<br>CODE | No.<br>Bytes | No.<br>Cycles |

|--------------------|---------------------------|------------|--------------|---------------|

| Immediate          | ORA #Oper                 | <b>Ø</b> 9 | 2            | 2             |

| Zero Page          | ORA Oper                  | Ø5         | 2            | 3             |

| Zero Page, X       | ORA Oper, X               | 15         | 2            |               |

| Absolute           | ORA Oper                  | ØD         | 3            | 4             |

| Absolute, X        | ORA Oper, X               |            | _            | 4             |

| Absolute, Y        | ·                         | 1D         | 3            | 4*            |

| 1                  | ORA Oper, Y               | 19         | 3            | 4*            |

| (Indirect, X)      | ORA (Oper, X)             | Ø1         | 2            | 6             |

| (Indirect), Y      | ORA (Oper), Y             | 11         | 2            | 5             |

|                    |                           |            | - 1          |               |

<sup>\*</sup> Add 1 on page crossing

PHA

PHA Push accumulator on stack

PHA

Operation: A +

NZCIDV

(Ref: 8.5)

Addressing Assembly Language OP No. Bytes Cycles

Implied PHA 48 1 3

PHP

PHP Push processor status on stack

PHP

peration: P+

$N \not\equiv C \mid D \mid V$

(Ref: 8.11)

| Addressing | Assembly Language | OP   | No.   | No.    |

|------------|-------------------|------|-------|--------|

| Mode       | Form              | CODE | Bytes | Cycles |

| Implied    | РНР               | Ø8   | 1     | 3      |

PLA

Operation: A 🕈

PLA Pull accumulator from stack

PLA

N Z C I D V

(Ref: 8.6)

| Addressing | Assembly Language | OP   | No.   | No.    |