# MICROCOMPUTER EXPERIMENTATION

WITH THE

Digitized by the Internet Archive in 2016

# MICROCOMPUTER EXPERIMENTATION WITH THE AIM 65

LANCE A. LEVENTHAL

Emulative Systems Company San Diego, California Library of Congress Cataloging-in-Publication Data

LEVENTHAL, LANCE A., 1945-

Microcomputer experimentation with the AIM 65.

Includes index.

1. AIM 65 (Computer)—Programming—Laboratory manuals. 2. Automatic control—Laboratory manuals. 3. 6502 (Microprocessor)—Programming—Laboratory manuals. I. Title.

TK7889.A37L48 1987

629.8'95

86-12277

ISBN 0-13-580283-0

Editorial/production supervision and

interior design: Cheryl Smith/Mary Jo Stanley

Cover design: *Photo Plus Art*Manufacturing buyer: *Rhett Conklin*

This book is dedicated to Stan Rogers, in appreciation of all he taught me about technical writing.

© 1987 by Prentice-Hall, Inc. A Division of Simon & Schuster Englewood Cliffs, New Jersey 07632

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

AIM 65®—Courtesy of Dynatem under license from Rockwell International.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

# ISBN 0-13-580283-0 025

Prentice-Hall International (UK) Limited, London

PRENTICE-HALL OF AUSTRALIA PTY. LIMITED, Sydney

PRENTICE-HALL CANADA INC., Toronto

Prentice-Hall Hispanoamericana, S.A., Mexico

PRENTICE-HALL OF INDIA PRIVATE LIMITED, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

PRENTICE-HALL OF SOUTHEAST ASIA PTE. LTD., Singapore

Editora Prentice-Hall do Brasil, Ltda., Rio de Janeiro

# CONTENTS

| PREFACE                                                                                                                      |                                                                                                        | V  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----|

| LABORATORY O BASIC OPERATIONS                                                                                                |                                                                                                        |    |

| Overview 2 Resetting the Computer 4 Examining Memory 4                                                                       | Changing Memory 7 Running a Program 8 Key Point Summary 9                                              |    |

| LABORATORY 1 WRITING AND RUNNING                                                                                             | SIMPLE PROGRAMS                                                                                        | 10 |

| Data Transfer Program 13 Entering and Running the Data Transfer Program 16 Processing Data 19 Logically ANDing Two Values 21 | Examining Registers 23 Changing Registers 24 Common Operating Errors 24 Key Point Summary 25           |    |

| LABORATORY 2 SIMPLE INPUT                                                                                                    |                                                                                                        | 27 |

| Simple Input 30 Flags and Conditional Branches 32 Waiting for a Switch to Close 33 Special Bit Positions 35                  | Examining Flags 36 Waiting for Two Closures 38 Searching for a Starting Character Key Point Summary 40 |    |

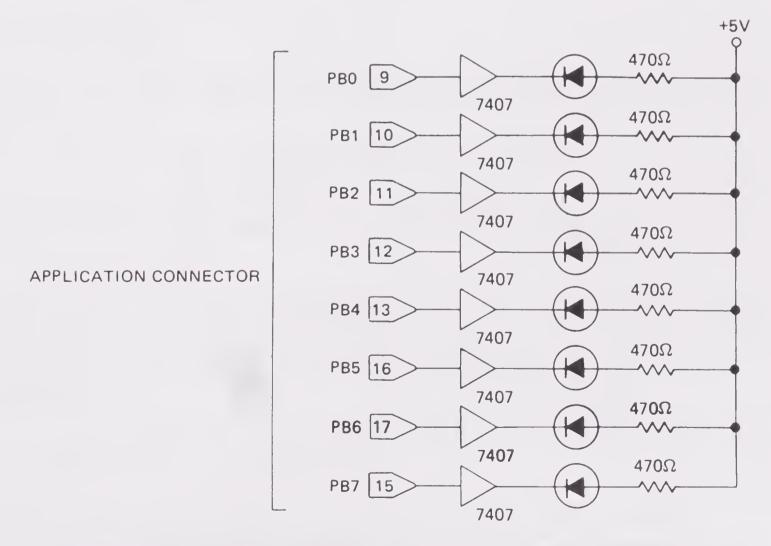

| LABORATORY 3 SIMPLE OUTPUT                                                                                                   |                                                                                                        | 41 |

| LED Connections 43 Assigning Directions to VIA I/O Lines 44                                                                  | Lighting an LED 45 Producing a Time Delay 46 Lengthening the Delay 48                                  |    |

|                                                                                                                              |                                                                                                        |    |

Bit Manipulation 50 Duty Cycle 51

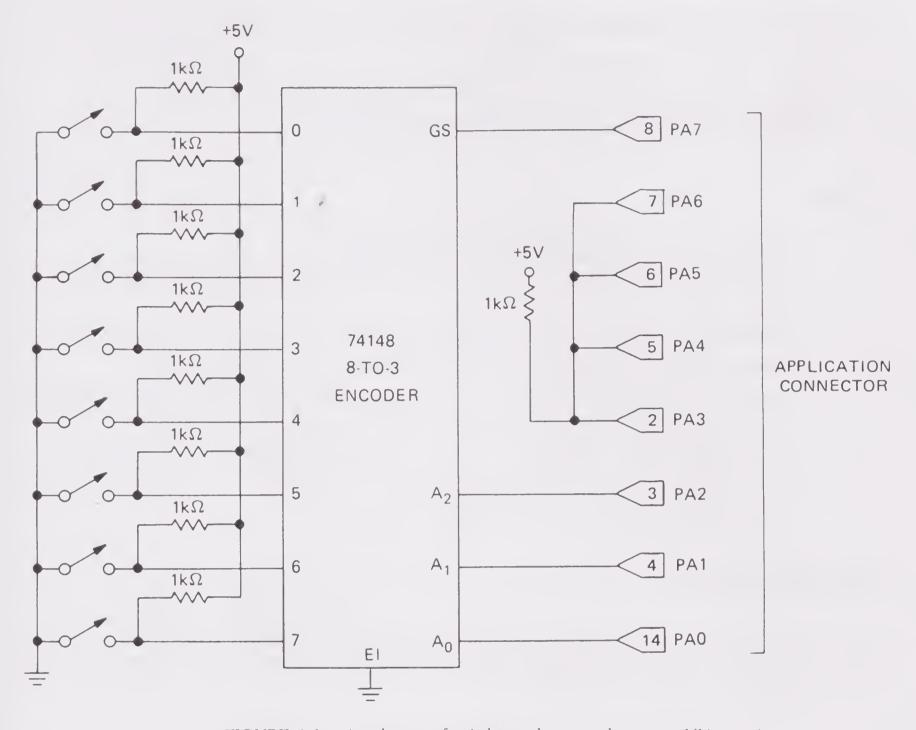

| LABOR | RATORY 4 PROCESSING DATA INPUT                                                                                                                                                                                          | <b>"S</b> "                                                                                                                                                                                               | 54  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

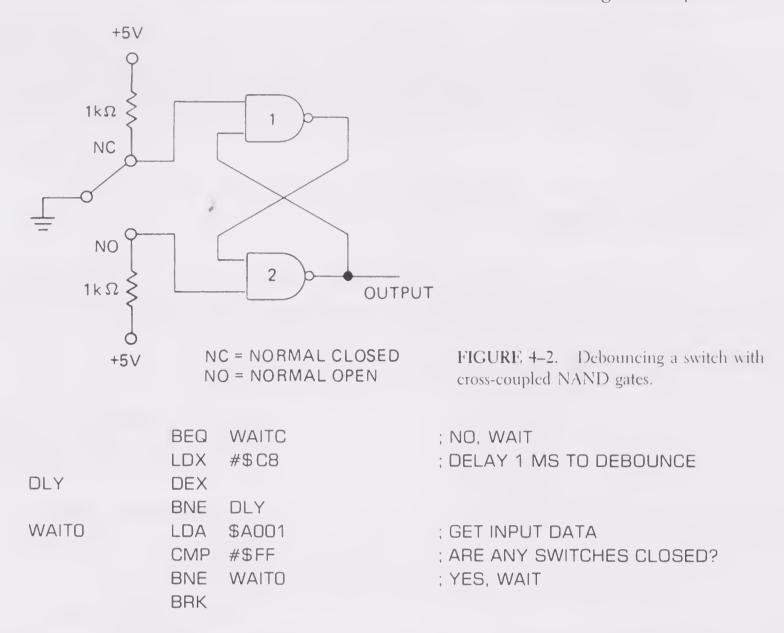

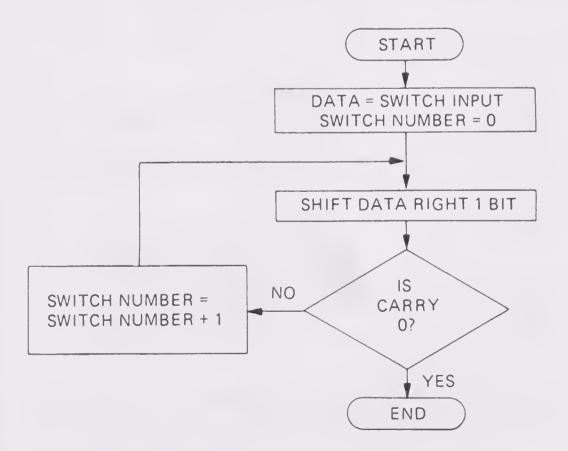

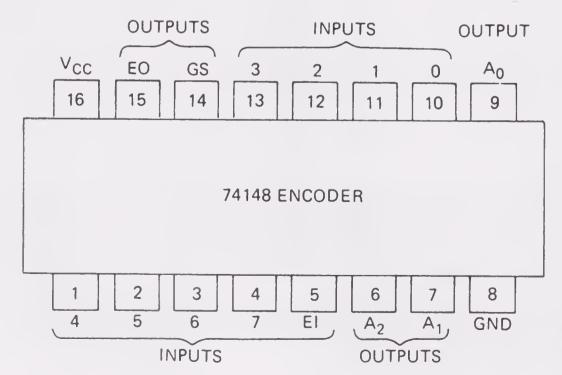

|       | Handling More Complex Inputs 56 Waiting for Any Switch to Close 56 Debouncing a Switch 58 Counting Closures 60                                                                                                          | Identifying the Switch 61 Using a Hardware Encoder 64 Key Point Summary 66                                                                                                                                |     |

| LABOR | RATORY 5 PROCESSING DATA OUTP                                                                                                                                                                                           | UTS                                                                                                                                                                                                       | 68  |

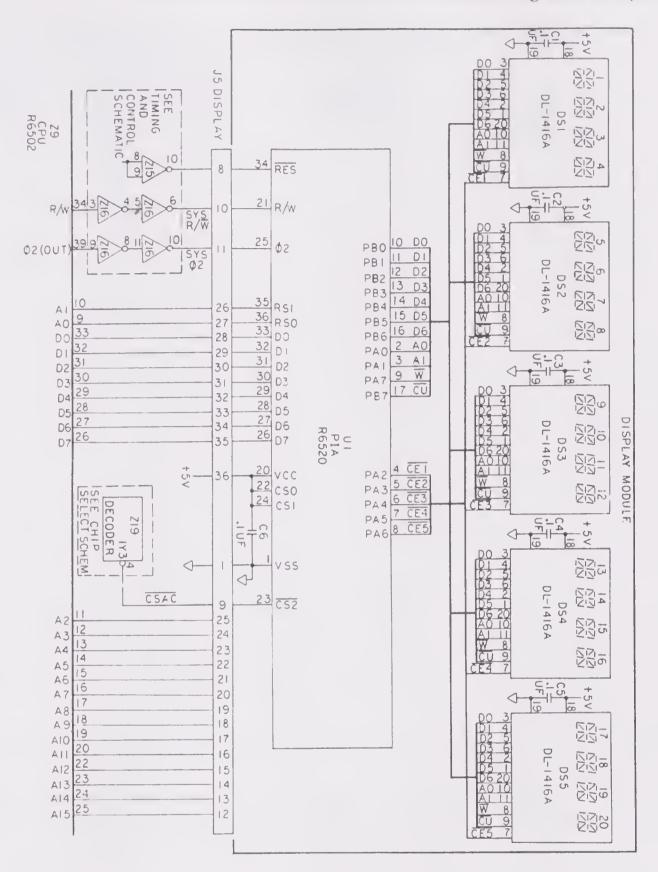

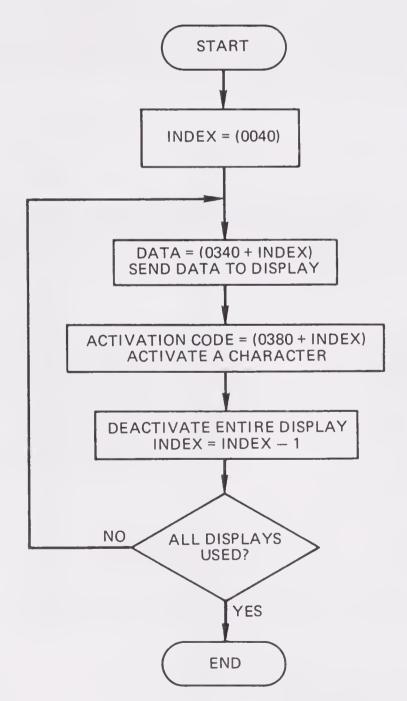

|       | Handling More Complex Outputs 70 Using the On-Board Display 70 Adding a Delay 75 Decimal-to-ASCII Conversion 76 Hexadecimal-to-ASCII Conversion 78                                                                      | Counting on the Displays 80 Character Selection by Lookup Table Moving a Character across the Display 84 Key Point Summary 86                                                                             | 82  |

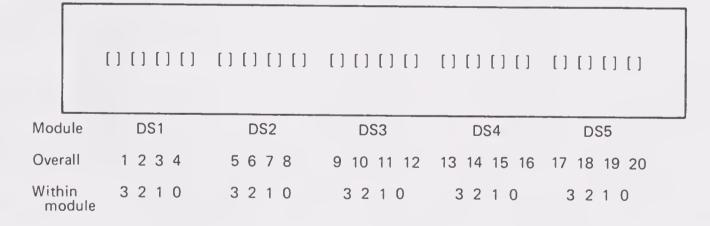

| LABOR | RATORY 6 PROCESSING DATA ARRA                                                                                                                                                                                           | YS                                                                                                                                                                                                        | 88  |

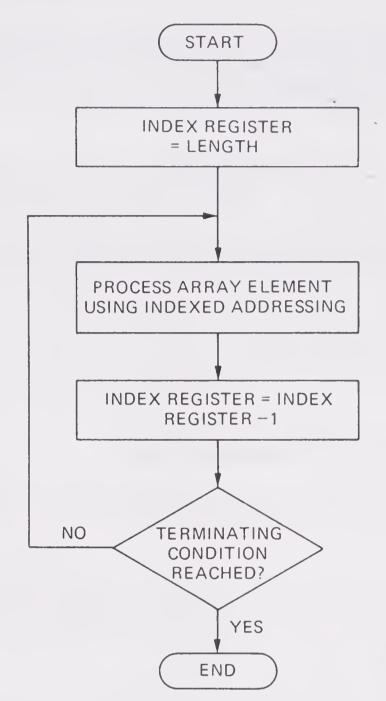

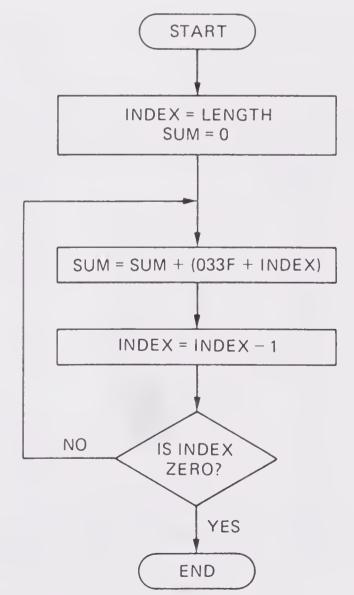

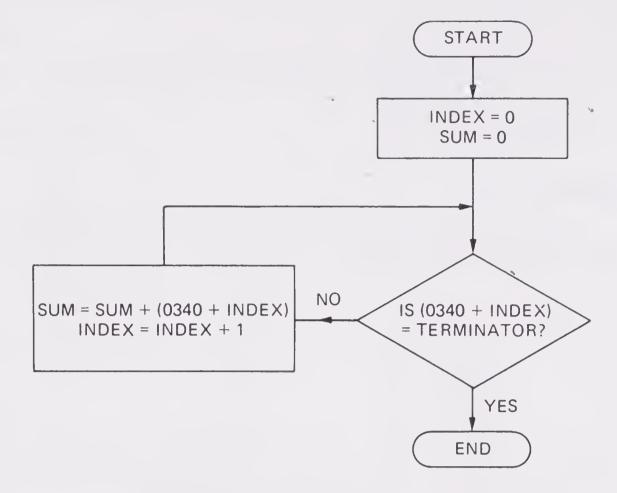

|       | Data Arrays 89 Processing Arrays with the 6502 Microprocessor 91 Sum of Data 92 Using a Terminator 95                                                                                                                   | Limit Checking 97 Displaying a Message 99 Varying the Base Address 102 Key Point Summary 103                                                                                                              |     |

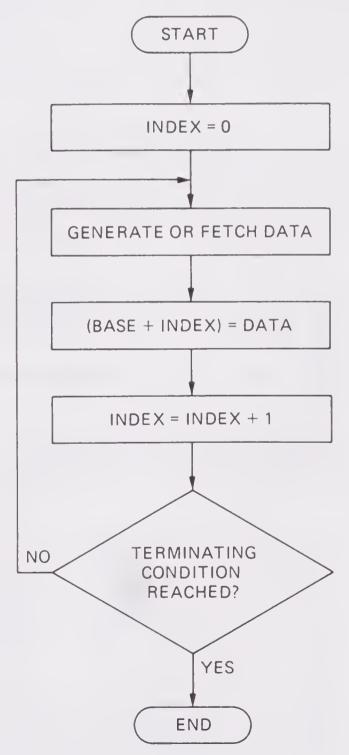

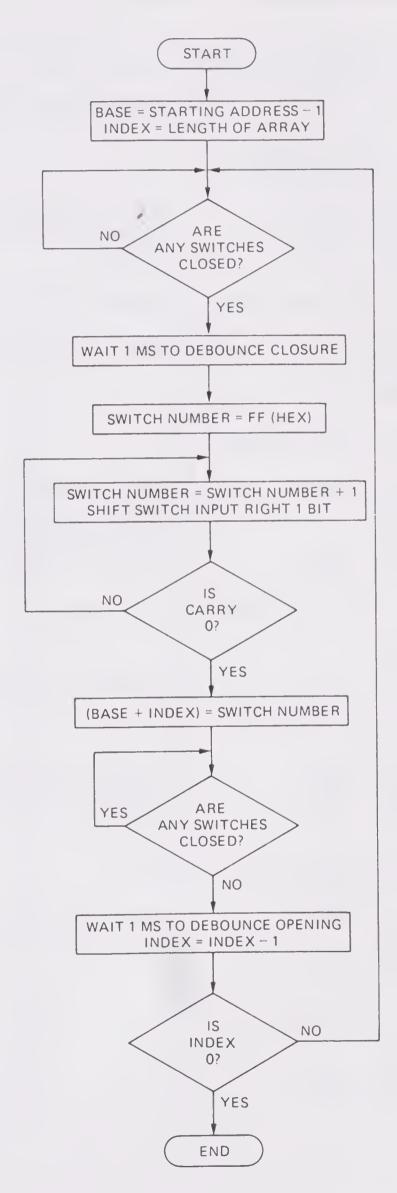

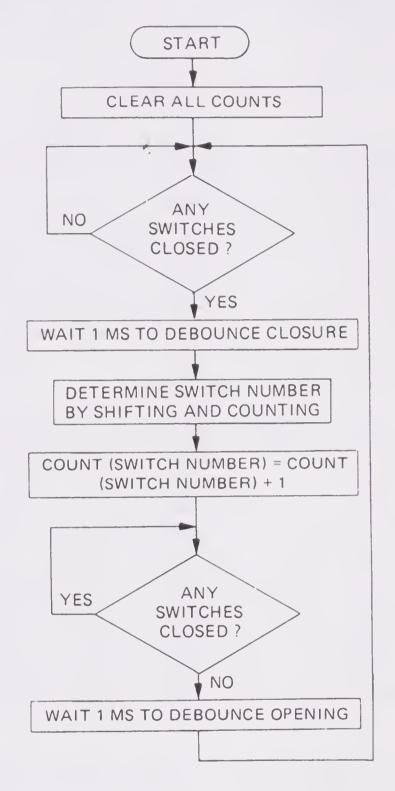

| LABOR | RATORY 7 FORMING DATA ARRAYS                                                                                                                                                                                            |                                                                                                                                                                                                           | 105 |

|       | Standard Procedure for Forming Arrays 107 Clearing an Array 108 Placing Values in an Array 109 Entering Input Data into an Array 112                                                                                    | Accessing Special Elements 116 Counting Switch Closures 118 Arrays of Addresses 119 Long Arrays 122 Key Point Summary 124                                                                                 |     |

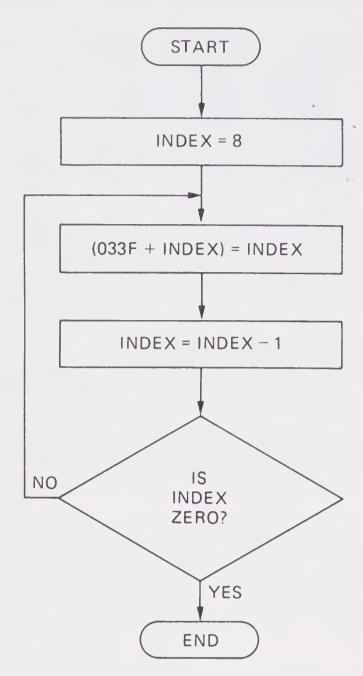

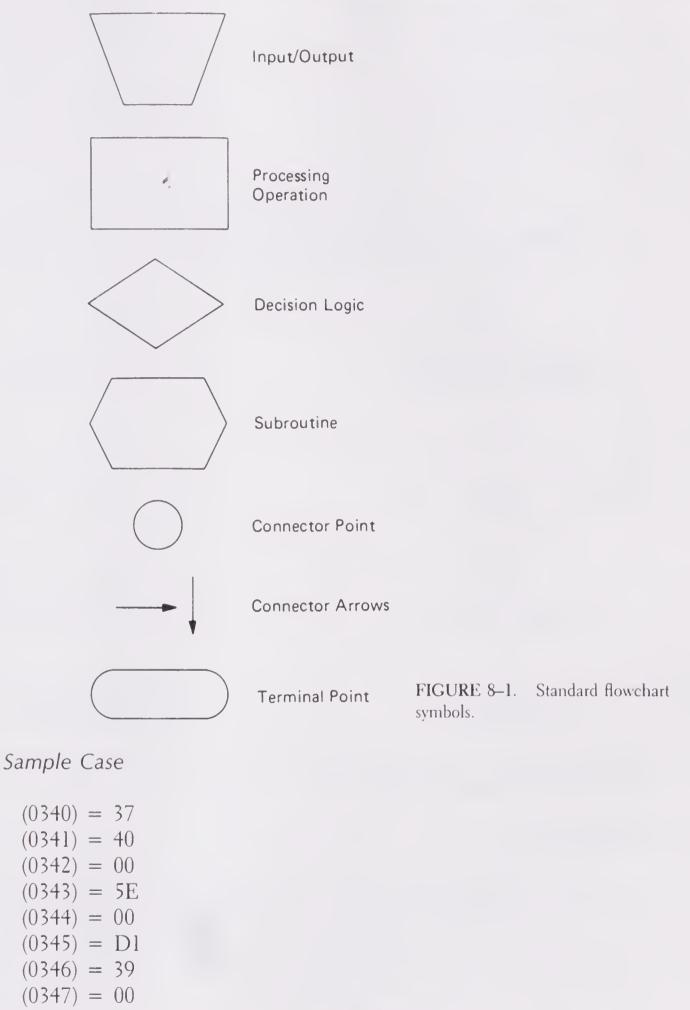

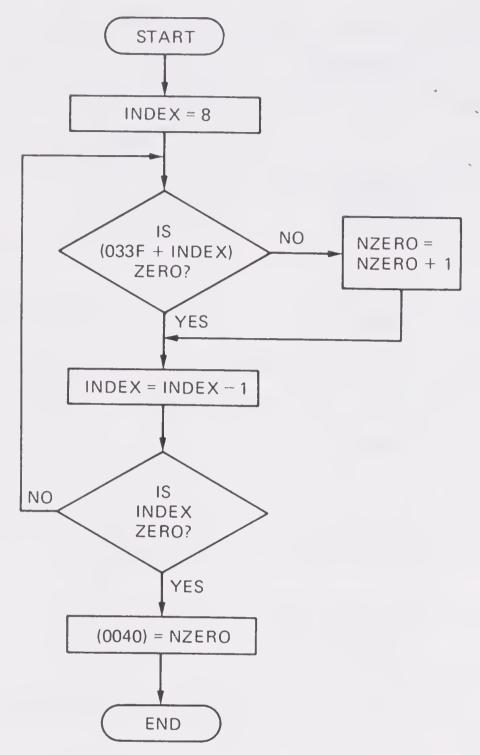

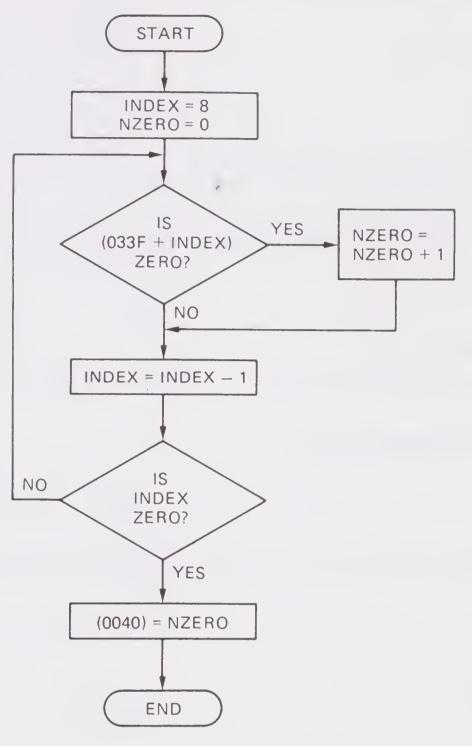

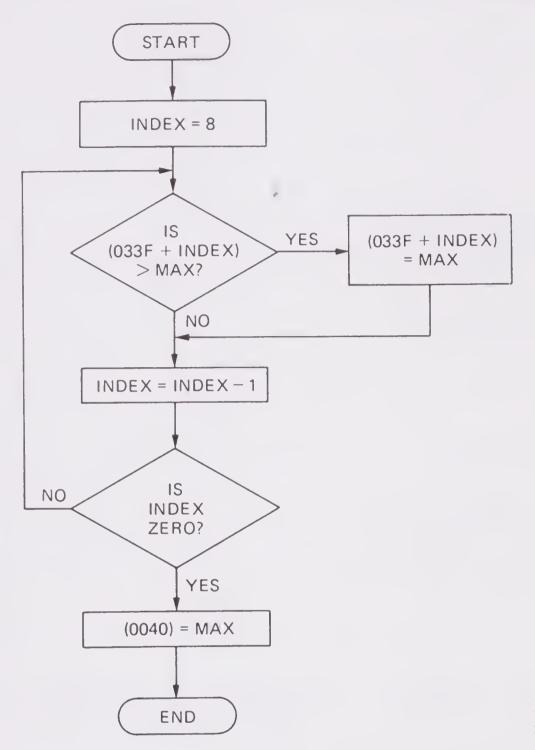

| LABOR | RATORY 8 DESIGNING AND DEBUGG                                                                                                                                                                                           | ING PROGRAMS                                                                                                                                                                                              | 125 |

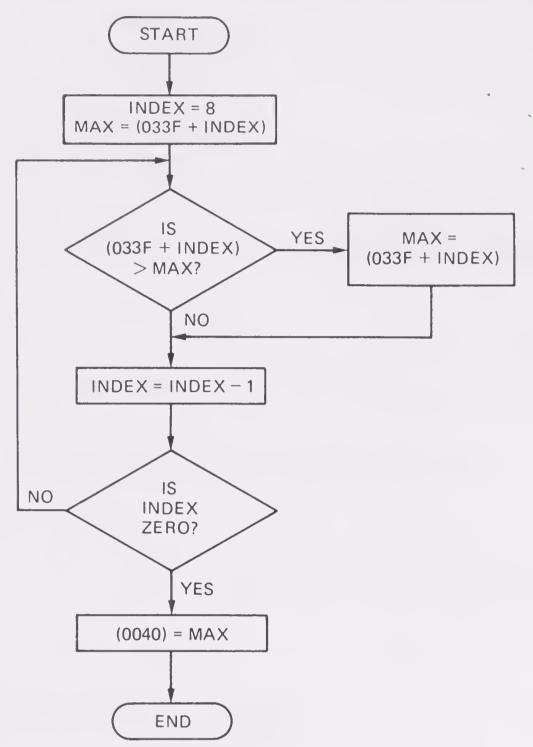

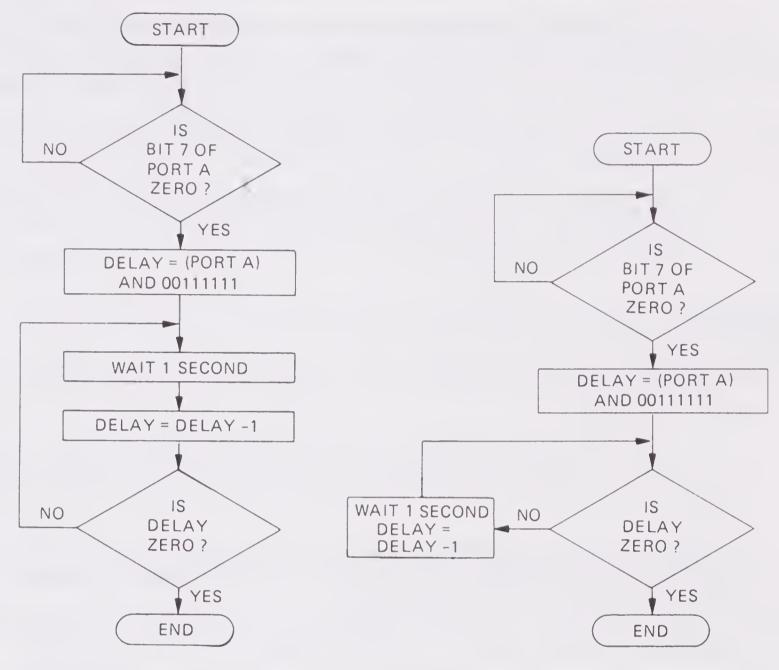

|       | Stages of Software Development 127 Flowcharting 128 Flowcharting Example 1: Counting Zeros 128 Flowcharting Example 2: Maximum Value 132 Flowcharting Example 3: Variable Delay 134 Debugging Tools 135 Breakpoints 136 | STEP Mode 137 Traces 137 Debugging Example: Counting Zeros 138 Using Breakpoints 141 Dump and Disassembler 145 Why the Editor/Assembler Is Useful 146 Common Programming Errors 146 Key Point Summary 148 |     |

Key Point Summary 53

149

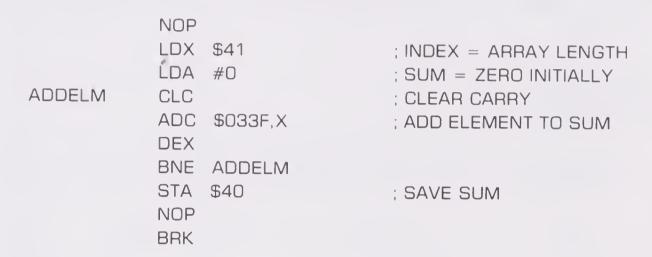

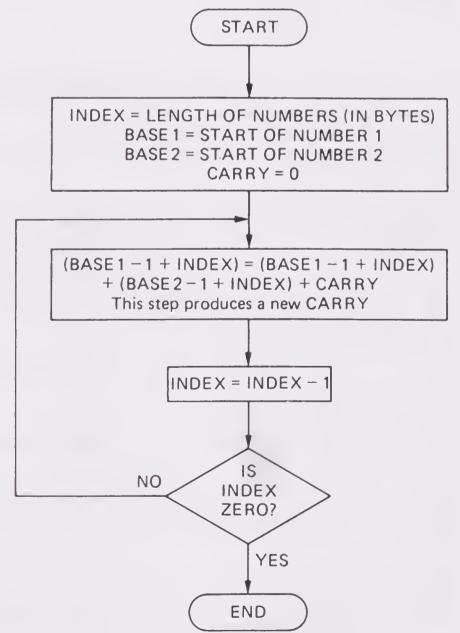

# LABORATORY 9 ARITHMETIC

Applications of Arithmetic 151

8-Bit Binary Sum 151

Binary-Coded-Decimal (BCD)

Representation 153

8-Bit Decimal Sum 155

Decimal Summation 157

16-Bit Arithmetic 158

Multiple-Precision Arithmetic 161

Arithmetic with Lookup Tables 164

Key Point Summary 167

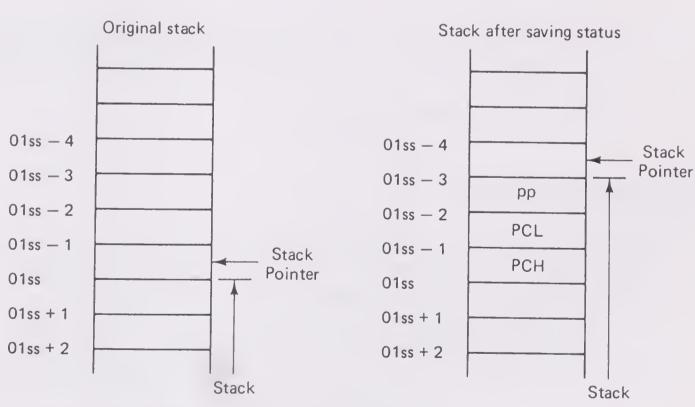

# LABORATORY A SUBROUTINES AND THE STACK

169

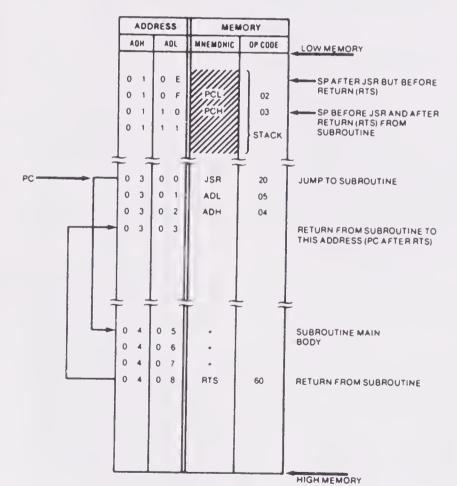

Rationale and Terminology 171

Call and Return Instructions 171

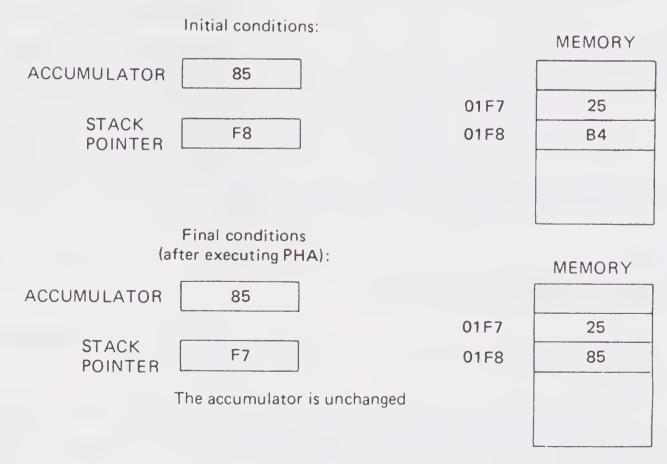

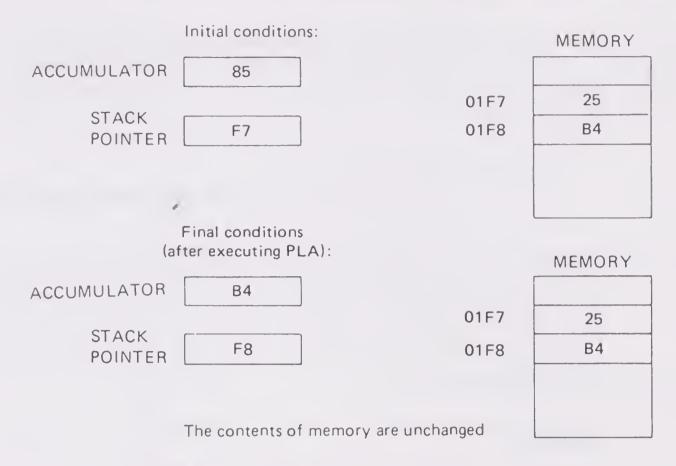

6502 Stack and Stack Pointer 172

Guidelines for Stack Management 174

Subroutine Linkages in the Stack 175

Saving Registers in the Stack 177

Delay Subroutine 177

Input Subroutine 179

Output Subroutine 180

Using Monitor Subroutines 181

Using the Output Subroutines 183

Calling Variable Addresses 187

Key Point Summary 190

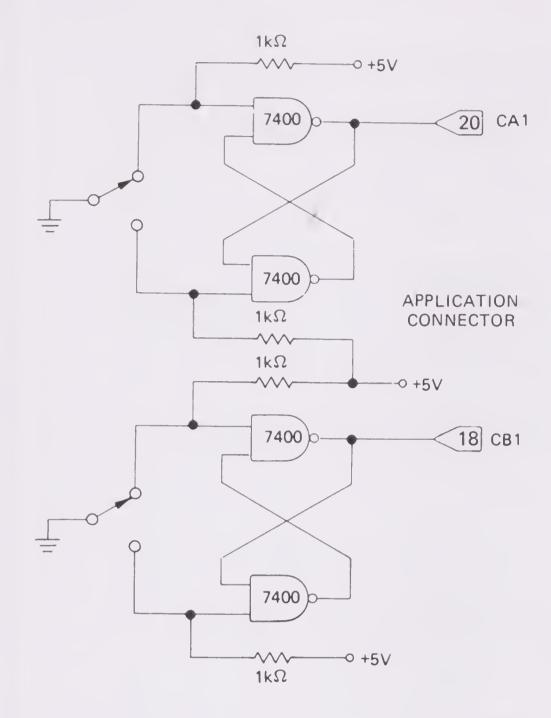

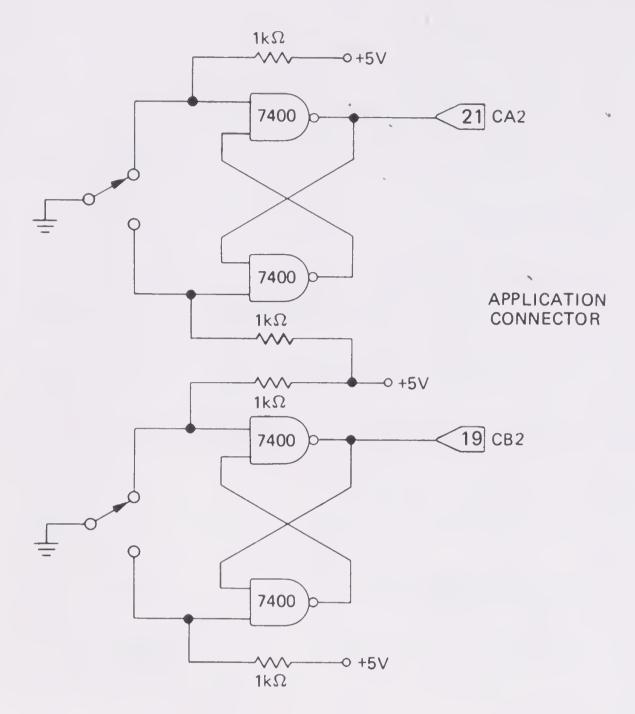

# LABORATORY B INPUT/OUTPUT USING HANDSHAKES

192

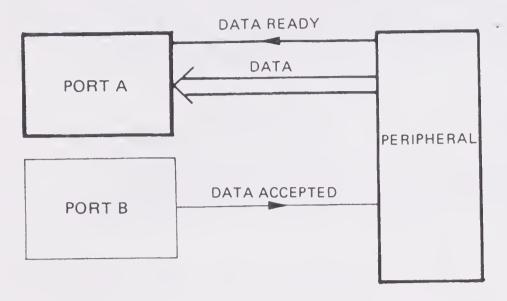

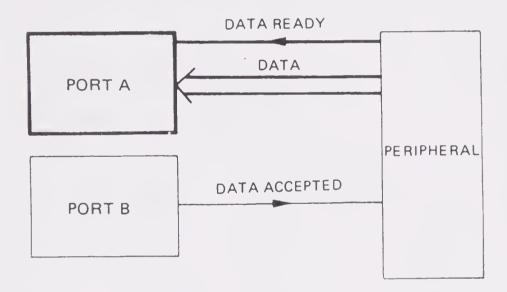

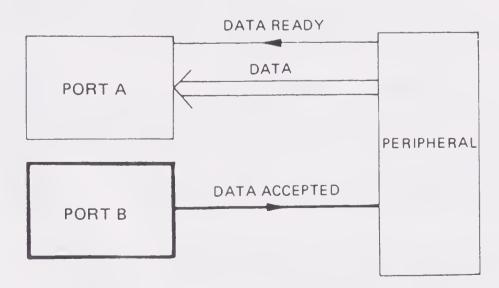

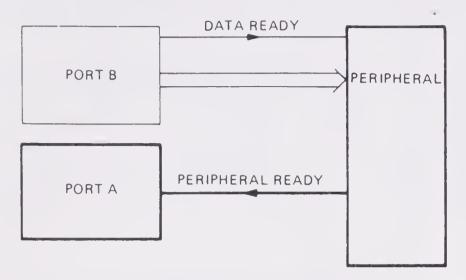

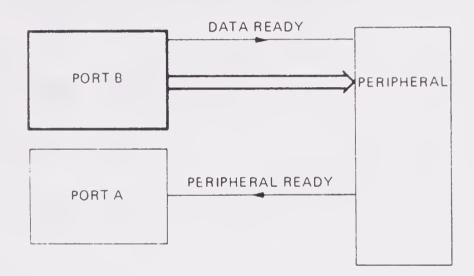

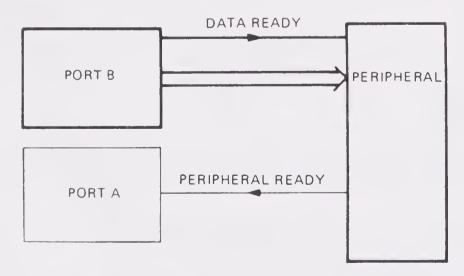

Synchronous and Asynchronous I/O 196

Treating Status and Control Signals as

Data 197

Using Data Lines for Status 198

Using Data Lines for Control 200

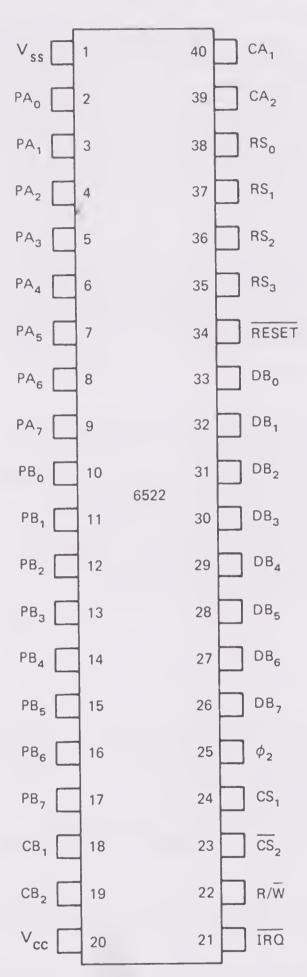

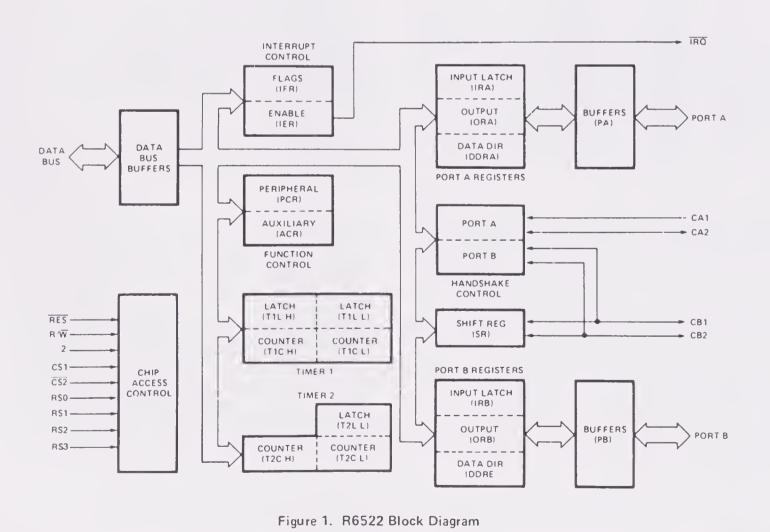

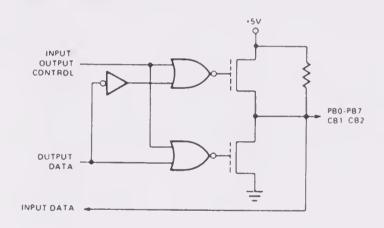

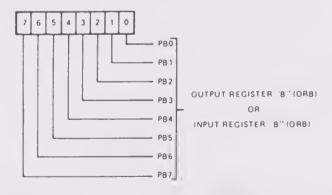

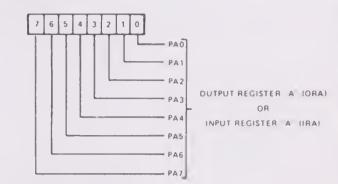

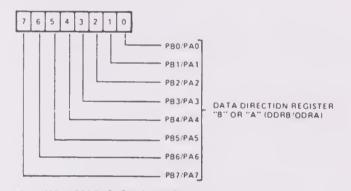

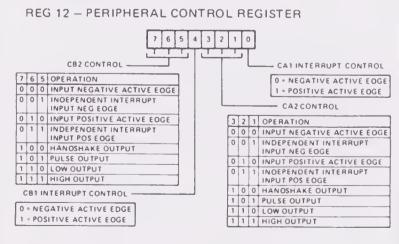

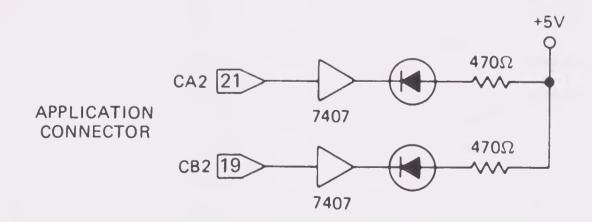

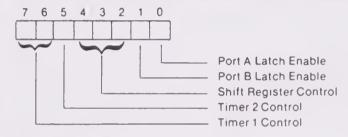

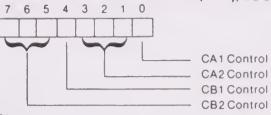

6522 Versatile Interface Adapter 203

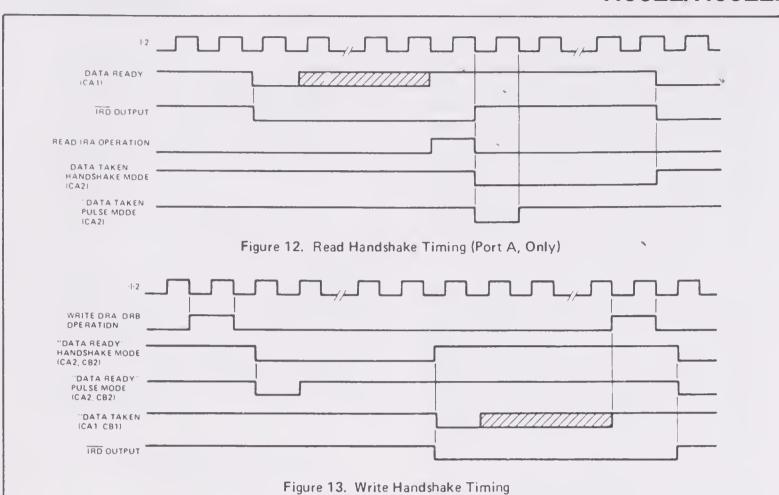

VIA Status Inputs 206

VIA Control Outputs 210

VIA Automatic Control Modes 214

Programmable I/O Devices 216

Key Point Summary 216

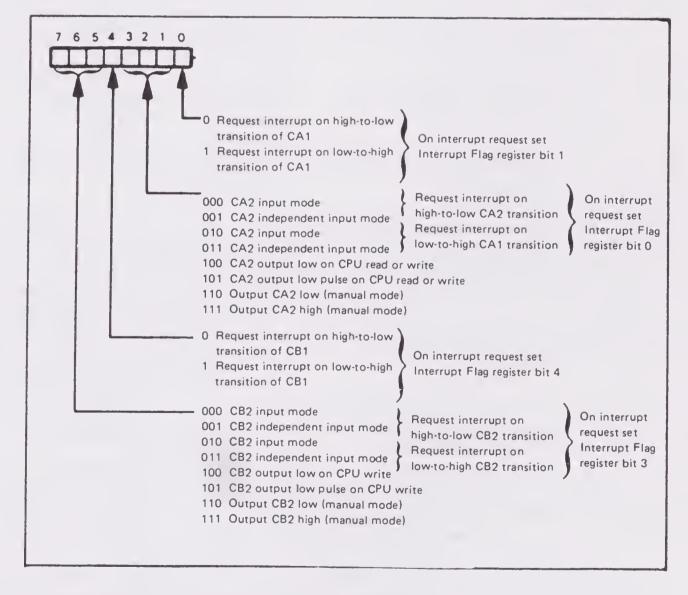

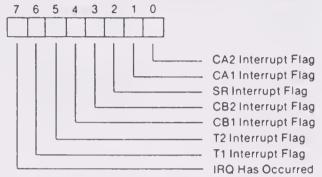

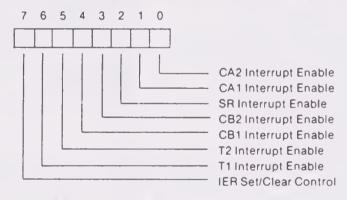

# LABORATORY C INTERRUPTS

218

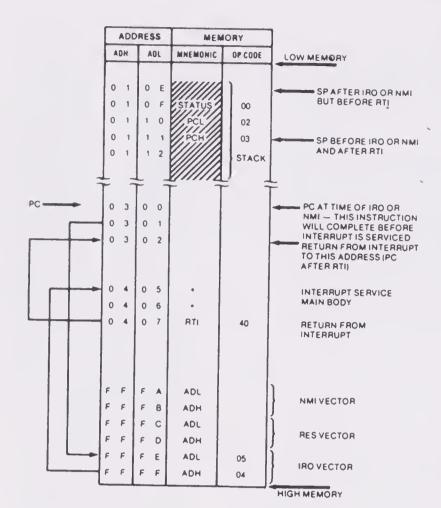

Overview of Interrupts 220

6502 Interrupt System 220

AIM Interrupts 222

Nonmaskable Interrupts 222

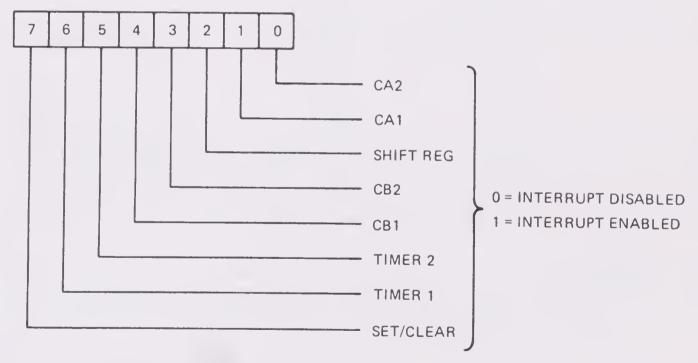

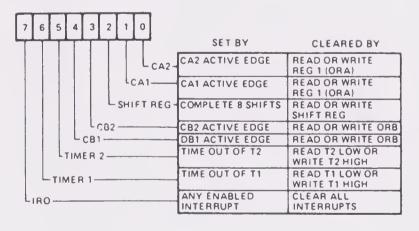

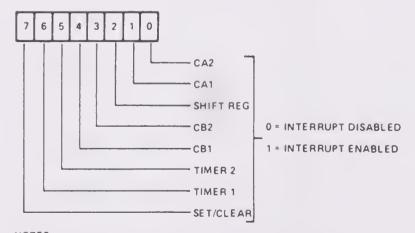

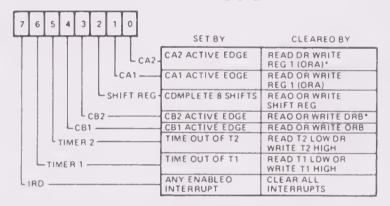

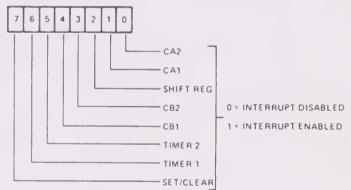

6522 VIA Interrupts 223

Handshaking with Interrupts 226

Communicating with Interrupt Service

Routines 230

Buffering Interrupts 231

Multiple Sources of Interrupts 235

Guidelines for Programming with

Interrupts 239

Key Point Summary 239

# LABORATORY D TIMING METHODS

241

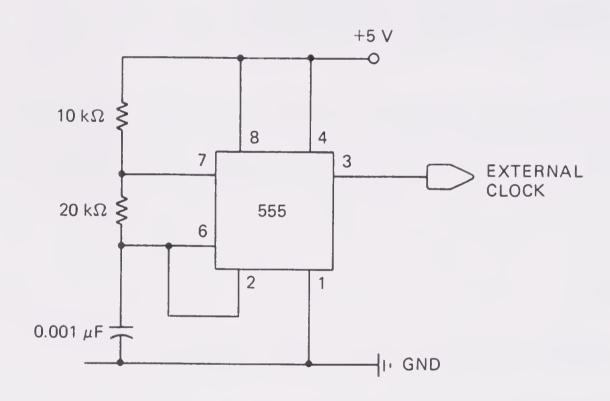

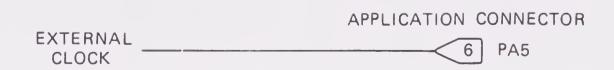

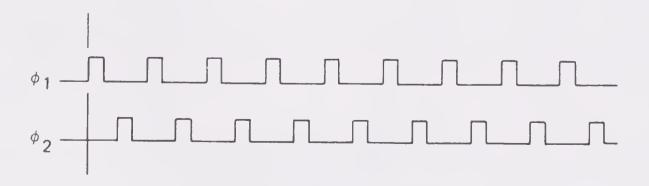

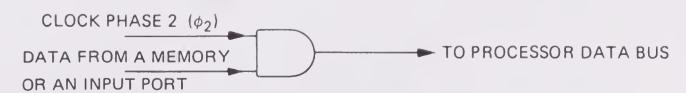

Timing Requirements and Methods 243

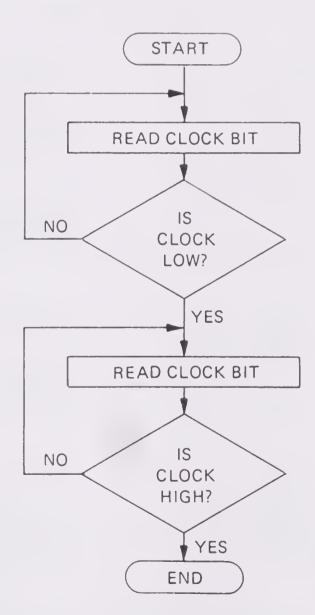

Waiting for a Clock Transition 244

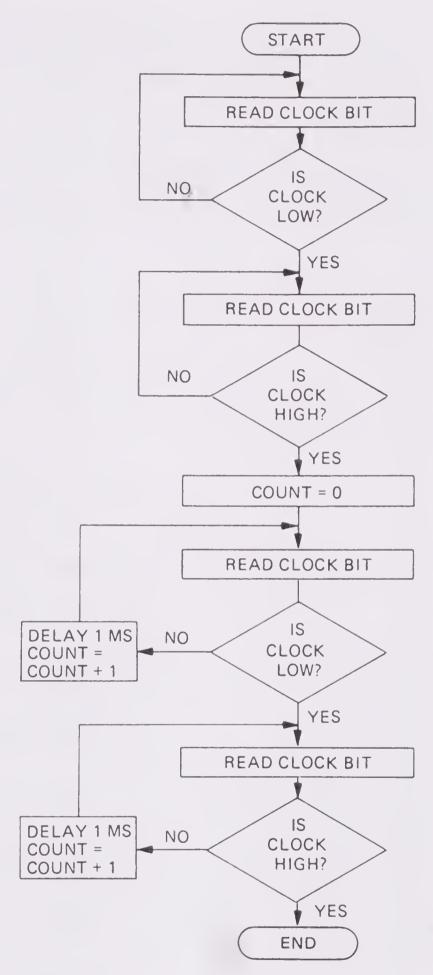

Measuring the Clock Period 246

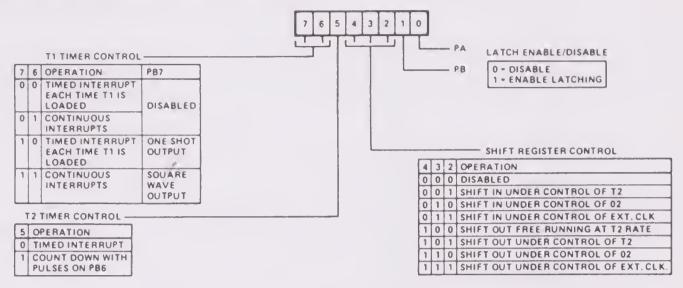

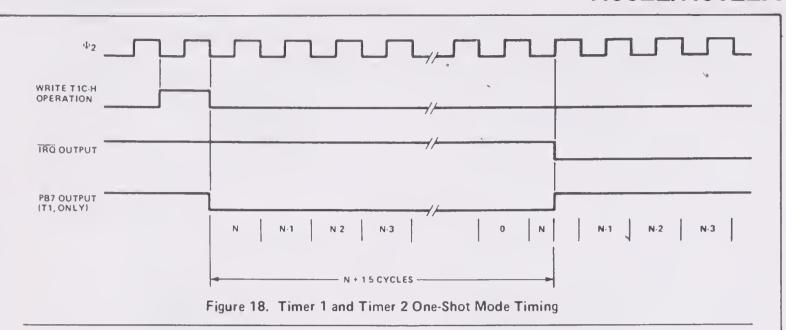

Programmable Timers 249

6522 Interval Timers 249

Elapsed Time Interrupts 253

Real-Time Clock 256 Longer Time Intervals 259 Keeping Time in Standard Units 260 Real-Time Operating Systems 263 Key Point Summary 263

| LABORATORY E SERIAL INPUT/OUTPUT                                                                                                                                            |                                                                                                                         | 265 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|

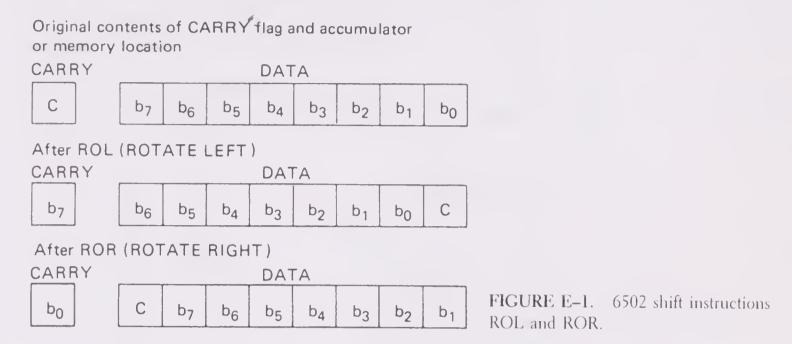

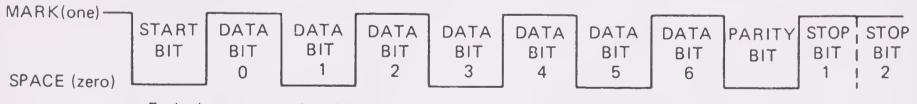

| Serial Interfacing 267 Serial/Parallel Conversion 267 Generating Bit Rates 270 Using the Real-Time Clock 273                                                                | Start and Stop Bits 276 Detecting False Start Bits 279. Generating and Checking Parity 2 Key Point Summary 285          | 282 |

| LABORATORY F MICROCOMPUTER TIMIN                                                                                                                                            | G AND CONTROL                                                                                                           | 286 |

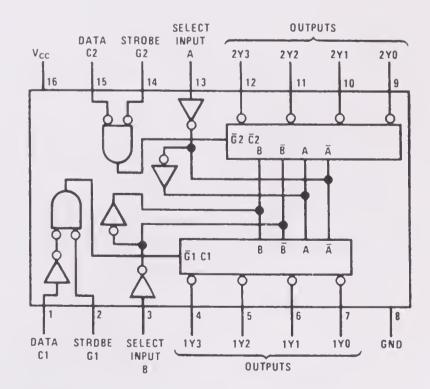

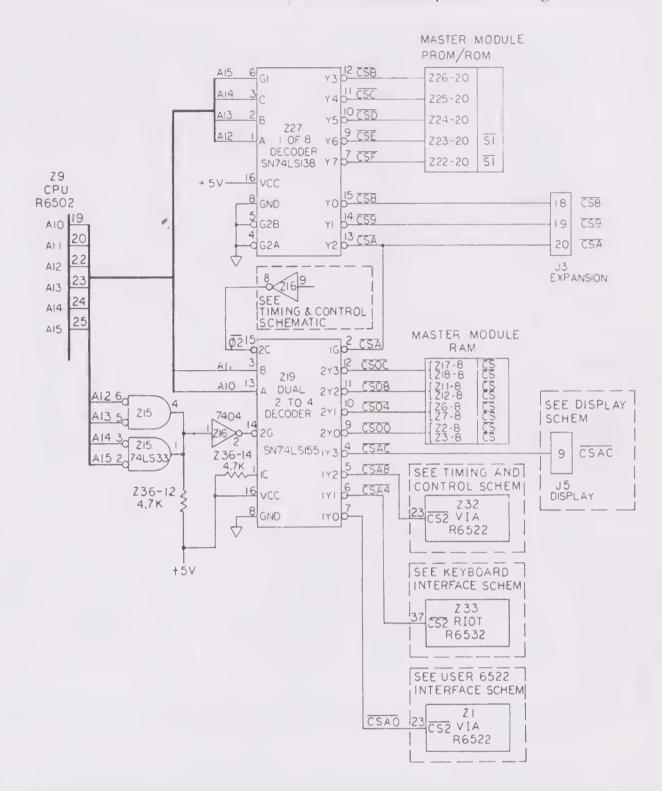

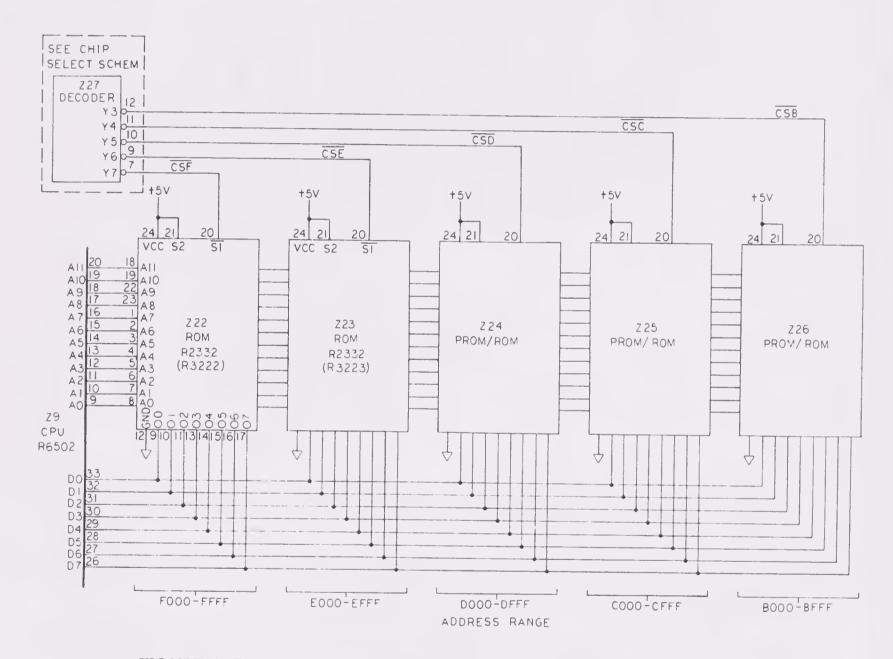

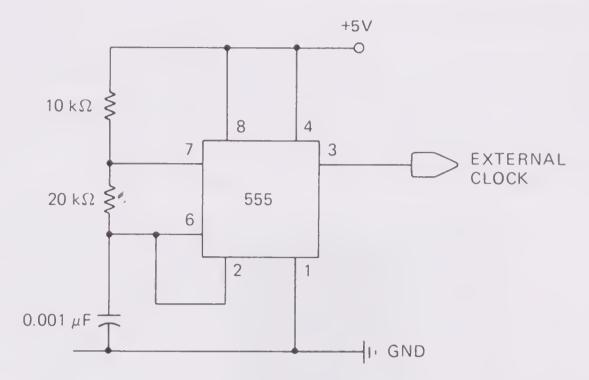

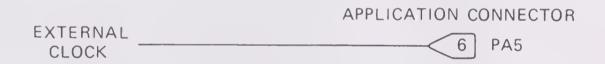

| Special Problems in Microcomputer Hardware Design 288 Timing and Control Functions 288 System Clock 289 Tracing Instruction Execution 292 Execution of Addressing Modes 293 | Decoding Address Lines 295 Multiple Addresses and Memory Expansion 299 Addressing I/O Devices 300 Key Point Summary 302 |     |

| Appendix 1 6502 Microprocessor Instruction                                                                                                                                  | on Set                                                                                                                  | 304 |

| Appendix 2 ASCII Character Table                                                                                                                                            |                                                                                                                         | 309 |

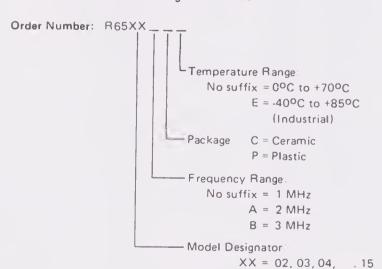

| Appendix 3 Brief Descriptions of 6502 Fam                                                                                                                                   | nily Devices                                                                                                            | 310 |

| Appendix 4 Laboratory Interfaces and Part                                                                                                                                   | s Lists                                                                                                                 | 324 |

| Appendix 5 Summary of the AIM 65 Monit                                                                                                                                      | tor                                                                                                                     | 332 |

| INDEX                                                                                                                                                                       |                                                                                                                         | 337 |

|                                                                                                                                                                             |                                                                                                                         |     |

# **PREFACE**

The purpose of this manual is to provide experimental training on microcomputers for people in the fields of engineering, engineering technology, computer science, the physical sciences, electronics, and related fields. The emphasis is on the design of controllers for industrial and laboratory use. The experiments, examples, and problems were adapted from applications in instrumentation, test equipment, communications, computers and peripherals, industrial control, process control, business equipment, aerospace and military systems, and consumer products. The manual illustrates the use of microcomputers in tasks that are essential to all these applications, responding to switches, controlling displays, encoding and decoding data, collecting and processing data, executing arithmetic functions, interfacing simple handshaking peripherals (such as terminals and printers), timing and scheduling operations, and implementing serial communications.

First, the manual describes how to operate the microcomputer. It then introduces assembly language programming, shows how to perform simple controller functions, discusses hardware-software trade-offs, describes how to design and develop programs, illustrates alternative approaches to input/output and timing, presents the advantages and uses of programmable LSI devices, and describes serial communications. The final experiment provides a brief introduction to hardware design and development. The manual includes numerous examples drawn from actual applications, but simplified to avoid requiring extensive background, special equipment (beyond the microcomputer itself), or long setup times. Because the manual is self-contained, it can be used by people with a variety of interests and backgrounds.

The manual is based on the popular AIM 65 microcomputer (formerly manufactured by Rockwell International and now licensed to Dynatem of Irvine, California) because of its low cost, wide availability, completeness, and ease of use. The AIM does not require

expensive peripherals (such as a terminal), has excellent documentation, requires no assembly, has expansion capabilities, and contains all the components of typical microcomputers. The AIM's ROM-based monitor makes it easy to explain and use, and it has enough memory and input/output lines for many interesting and relevant examples.

This manual emphasizes the control of systems with software. This control is illustrated with simple examples using switches, single displays, and the on-board peripherals. The intent here is to provide realistic examples that require little additional hardware and can be performed in short time periods. Numerous programs are included as starting points for students and as references for examination and comparison.

The standard format used in this book conforms with other textbooks, manuals, and reference materials. I have used the notation from the 6502 assembler provided by MOS Technology (now a division of Commodore Business Machines). I have tried to make all programs clear, simple, well structured, and well documented. I have avoided programming tricks, even when they would make programs somewhat shorter and faster. Good programming practices are essential to microcomputer users, so I have tried to provide sound, fully tested examples for readers to follow. Besides, few things give readers more pleasure than writing a program that is shorter, faster, and more ingenious than the one in the book.

This manual does not describe the 6502 microprocessor in detail. Nor does it offer a complete discussion of 6502 assembly language programming. I therefore provide extensive references to appropriate textbooks, 6502 manuals, and programming books. Because the manual is self-contained, it can be used independently of the reference materials. I have also compiled an extensive index so that casual users can find programs of specific interest to them and students can readily find material for review, reference, or further information.

Each experiment in the manual is itself self-contained. Each includes a list of goals, definition of new terms, references (with page numbers), descriptions of instructions that are being introduced, a list of required equipment (with diagrams), and a key point summary. Each laboratory exercise contains numerous problems that are linked closely to the discussion. The problems illustrate key points, relate current material to previous experiments, and provide examples from actual applications; there are no "make-work" problems or rote tasks. I have tested all the problems and provide sample data, hints, and discussions.

Many people contributed to the writing of this manual. Irvin Stafford of Burroughs Corporation constructed the hardware, checked the examples and problems, and suggested many improvements and corrections. Carter Stafford provided the photographs of the AIM and the other laboratory apparatus. Ralph Reccia of Rockwell International was most helpful in answering questions and providing materials and encouragement. Dennis Starbuck of Dynatem also provided current material describing his company's product line. Professor Wilson Turner of California State University, San Bernardino, used a preliminary version of the manual in his classes and offered many criticisms and suggestions. Cheryl Smith and Mary Jo Stanley of Prentice-Hall, along with copy editor Bruce Emmer, did an outstanding production job. All remaining errors are, of course, my fault. Cheers!

# BASIC OPERATIONS

# **PURPOSE**

To learn how to operate the microcomputer.

# REFERENCE MATERIALS

R. J. TOCCI and L. P. LASKOWSKI, *Microprocessors and Microcomputers: Hardware and Software*, 2nd ed., Prentice-Hall, Englewood Cliffs, NJ, 1982, pp. 11–12 (hexadecimal number system), 70–72 (types of semiconductor memories), 92–94 (basic computer system organization).

AIM 65 User's Guide, Dynatem, Irvine, CA, 1979, Chapters 1 and 2.

# WHAT YOU SHOULD LEARN

- 1. How to reset the computer.

- 2. How to examine a memory location.

- 3. How to change a memory location.

- 4. How to enter and run a program.

# **TERMS**

Byte a unit of 8 bits, may be described as consisting of two hexadecimal digits (the four most significant bits and the four least significant bits).

Central processing unit (CPU) the part of the computer that controls its operations and processes data.

Cursor a movable indicator of position on a display.

Hexadecimal (hex) number system with base 16. The digits are the numbers 0 through 9, followed by the letters A through F (see Table 0–1).

Microcomputer a computer with a microprocessor as its CPU.

Microprocessor a single-chip CPU.

Monitor a program that allows the computer user to enter programs and data, run programs, examine memory and registers, and use peripherals.

Nonvolatile memory a memory that retains its contents when power is lost.

Read-only memory (ROM) a memory that can be read but not changed in normal operation.

Read/write (random-access) memory (RAM) a memory that can be both read and changed (written) in normal operation.

Reset a signal that puts the computer in a known initial state.

Scratchpad a memory area that is especially convenient to use for temporary storage.

Word the basic grouping of bits that a computer can process at one time. The 6502 microprocessor has an 8-bit word.

### 6502 INSTRUCTIONS

BRK (00 hex) force break; on the AIM 65, BRK transfers control to the monitor.

### **OVERVIEW**

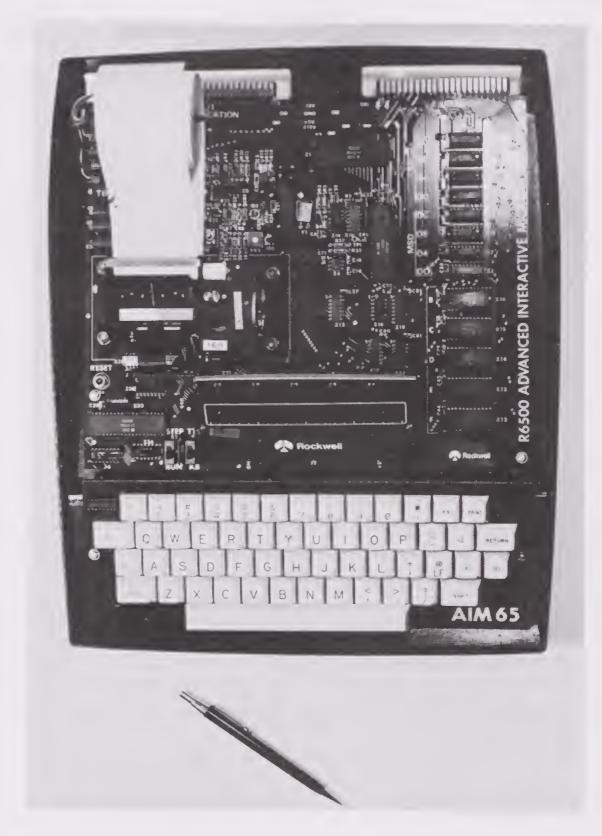

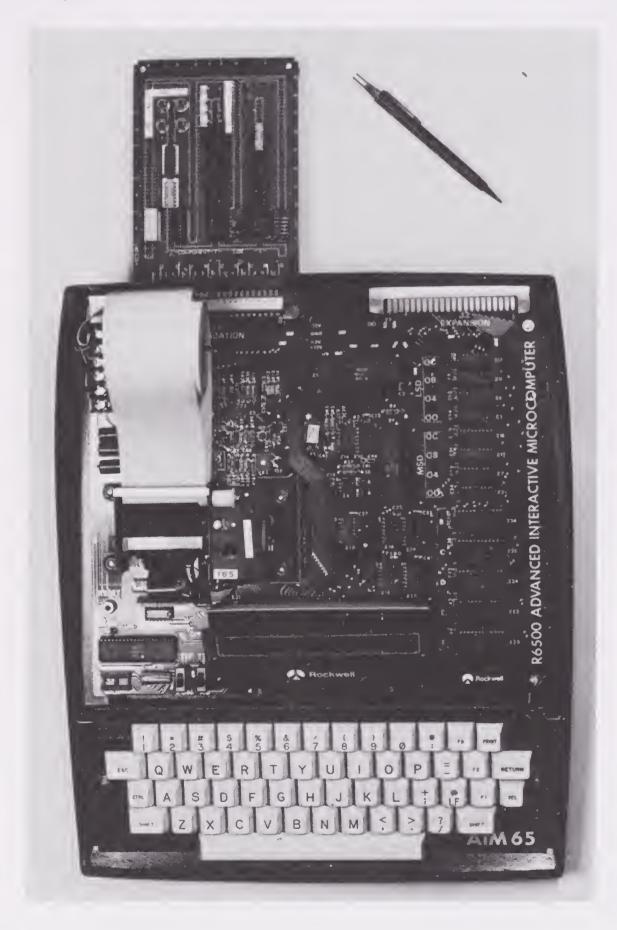

The AIM 65 (Figure 0-1) is an inexpensive microcomputer. Sections 1.6 through 1.8 of

FIGURE 0-1. The AIM 65 microcomputer. (Courtesy of Carter Stafford.)

the AIM 65 User's Guide describe how to set it up and attach a power supply. It has the following components:

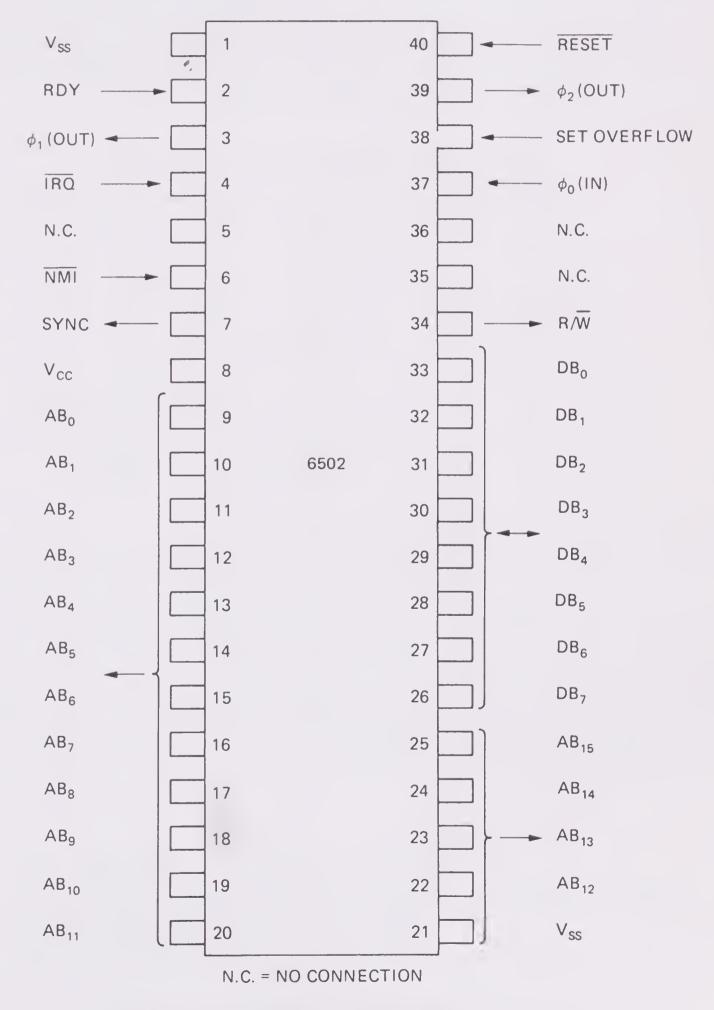

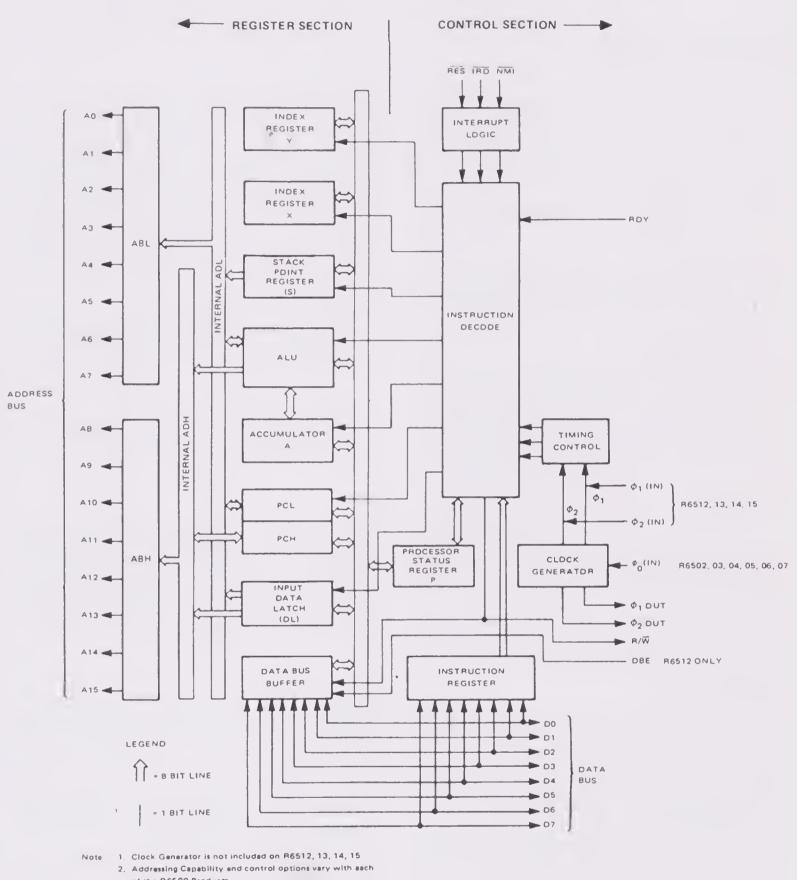

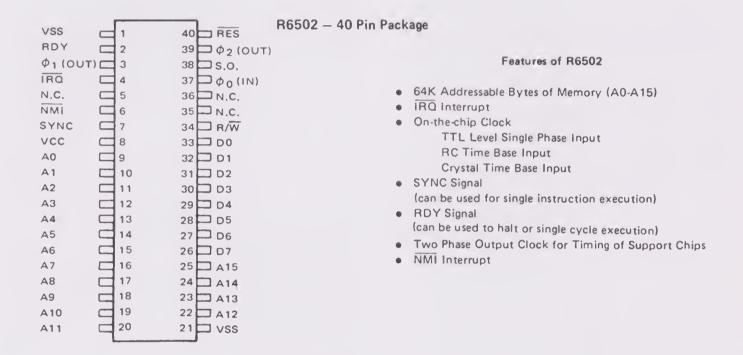

- A 6502 microprocessor, the central processing unit or "brain."

- Read-only memory, or ROM (two 2332 devices that contain a monitor). Each 2332 ROM consists of 4K 8-bit units (*bytes*).  $1K = 2^{10} = 1,024$ .

- Read/write memory, or RAM (two 2114 devices into which the user can enter data and programs). Each 2114 RAM consists of 1K 4-bit units. The two 2114s connected in parallel provide 1K bytes of memory. There are sockets for six more 2114s, thus expanding RAM to 4K bytes.

- 4 Microcomputer Experimentation with the AIM 65

- Two 6522 Versatile Interface Adapters (VIAs). Each VIA contains two 8-bit input/output (I/O) ports.

- A 54-key keyboard. Most keys are located just as on a standard typewriter; note, however, that there are no lowerease letters.

- A 20-character alphanumeric display.

- A 20-column thermal printer.

- A cassette interface that lets you transfer programs and data to and from audio eassettes (see Sections 2.9 and 2.10 of the AIM 65 User's Guide). We will not discuss eassettes again; you can use them to save programs and thus avoid repetitive keyboard input.

Appendix 3 contains descriptions of the 6502 and 6522 devices. For those unfamiliar with the hexadecimal (base 16) number system, there is a brief explanation in the textbook by Toeci and Laskowski, as well as in many other books. Hexadecimal notation is merely a convenience to avoid references to long binary numbers.

# RESETTING THE COMPUTER

Before you start working with the AIM, you should reset it. The RESET button is located near the left edge of the computer just below the printer. Press and release it. The AIM should flash a message (ROCKWELL AIM 65) on its display and then leave a prompt ( $\angle$ ) at the far left.

The AIM is now executing the monitor stored in the 2332 ROMs. This program allows you to control the AIM from its keyboard. You can place programs and data in read/write memory, run programs, examine and change memory and registers, and do other simple operations. For more details, see the booklet entitled AIM 65 Monitor Program Listing.

# **EXAMINING MEMORY**

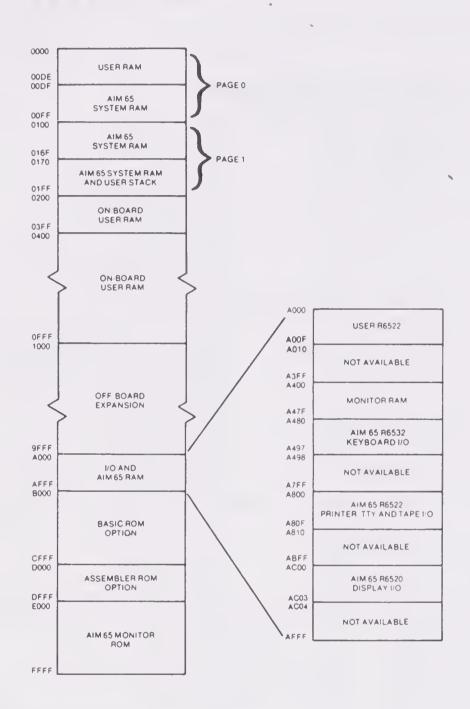

The basic AIM 65 has 1K bytes of read/write memory (RAM) in addresses 0000 through 03FF hexadecimal. Some of these addresses are special (see Appendix 5 for a complete map of AIM 65 memory). In particular, note the following:

- The monitor uses 00DF through 00FF for its own purposes. We will therefore not use those locations.

- The 6502 microprocessor uses 0100 through 01FF for its stack. We will discuss the stack in Laboratory A, but for now we will simply not use those locations either.

- Addresses 0000 through 00FF (the monitor uses some of these) serve as a scratchpad. We will see why in Laboratory I. We will use 0000 through 00DE for data only; we will not put any programs there.

Overall, we will use the following addresses:

- 0000 through 00DE for data.

- 0100 through 01FF for the stack.

- 0200 through 03FF for programs and data.

Note that each location has a 16-bit address (four hexadecimal digits) and contains 8 bits of data (two hexadecimal digits). Table 0-1 is a list of the hexadecimal digits and their binary and decimal equivalents. Use this table if you need help converting numbers from one base to another.

| Hexadecimal Digit | Decimal Value | Binary Value |

|-------------------|---------------|--------------|

| 0                 | 0             | 0000         |

| 1                 | 1             | 0001         |

| 2                 | 2             | 0010         |

| 3                 | 3             | 0011         |

| +                 | +             | 0100         |

| 5                 | 5             | 0101         |

| 6                 | 6             | 0110         |

| 7                 | 7             | 0111         |

| 8                 | 8             | 1000         |

| 9                 | 9             | 1001         |

| A                 | 10            | 1010         |

| В                 | 11            | 1011         |

| С                 | 12            | 1100         |

| 1)                | 13            | 1101         |

| E                 | 14            | 1110         |

| F                 | 15            | 1111         |

TABLE 0-1 HEXADECIMAL-TO-DECIMAL CONVERSION TABLE

Before you continue, be sure the AIM is in the following state:

- 1. Printer off. You can toggle the printer (that is, turn it off if it is on and vice versa) by pressing CTRL (leftmost key in the middle row) and PRINT (rightmost key in the top row) together. The display indicates whether the printer is on or off. You should turn it off initially to avoid wasting paper.

- 2. RUN/STEP and KB/TTY switches both forward (toward the keyboard). These switches are located just left of the display. Moving them forward puts RUN/STEP in the RUN position and KB/TTY in the KB position.

To examine memory, first press the M key. The display will show

The ^ acts as a cursor; it indicates where you are working on the line. You must now enter the address you want to examine, starting with the most significant digit. You can omit leading zeros. Remember that the digits are hexadecimal (see Table 0–1). If you get lost, start over by pressing RESET or the ESC (escape) key (leftmost key in the next-to-top row).

For example, enter the four-digit address 0200. New digits appear at the right as you would expect. Now press RETURN (rightmost key in the next-to-top row). Remember that the display is hexadecimal and that memory addresses are four digits long, whereas data entries are two digits long.

If you have done everything correctly, the AIM will display the address at the left and the contents of that address and the next three higher addresses at the right. A typical example is

# $\angle M \triangle = 0200$ 1F 2F BE 9D

# This means

- 1. Address 0200 contains 1F.

- 2. Address 0201 eontains 2F.

- 3. Address 0202 contains BE.

- 4. Address 0203 contains 9D.

Use Table 0-1 if you need help with hexadecimal digits.

Since 0200 through 0203 are in RAM, their values are arbitrary. RAM loses its contents when power is removed and could start in any state whatsoever. Such a memory is said to be *volatile*. Anything you put in RAM will be lost when you turn the AIM off.

Thus you can examine a memory location as follows:

- 1. Press ESC or RESET to obtain the prompt (∠).

- 2. Press M.

- 3. Enter its address as four hexadecimal digits starting with the most significant digit. You may omit leading zeros.

- 4. Press RETURN.

The contents of the location and the next three higher addresses will appear on the display. If you enter the address incorrectly, simply press ESC to start over. If you get totally confused, press RESET.

# PROBLEM 0-1

Examine address 0038 (hex).

# PROBLEM 0-2

Examine address ECA2 (hex). Its contents should be BF. We know what it contains, since it is in the nonvolatile read-only memory. You can look up the contents of ROM addresses in the AIM 65 Monitor Program Listing.

Note the following special features of the AIM display:

- 1. B and D have tails at the top and bottom, so you can tell them from 8 and 0, respectively.

- 2. 6 has a bar at the top and 9 has one at the bottom to make them easier to read.

- 3. Letters are generally wider than digits. In particular, the letters O and S are twice as wide as the digits 0 and 5, respectively. Thus you can tell them apart without much trouble.

- 4. I is a eapital letter, so you can easily distinguish it from 1 (one).

- 5. Many letters (particularly B, C, D, K, P, Q, R, S, and V) look strange. There are no eurved lines, and letters vary in size and spacing. The overall effect is primitive but eonsistent, as if someone were using a machine to imitate a child's printing.

As with ealculator displays, the AIM's odd-looking letters and numbers will become familiar with practice.

Once you have examined a set of four memory addresses, you can move on to the next four higher addresses by pressing the space bar. Try this and see what happens. The M disappears, but everything else looks the same, except that the address is 4 larger. Examine memory locations 0200 through 0220. You can move up through memory but not down. To stop examining memory, press ESC.

### CHANGING MEMORY

You can also change the locations you are examining. First, press the / key (next-to-last key in the row just above the space bar). For example, assume that you have just examined locations 0200 through 0203. You can change 0200 to 75 by pressing

```

/ (the display shows \angle/\Delta 0200^)

7 (the display shows \angle/\Delta 0200 7^)

5 (the display shows \angle/\Delta 0200 75^)

RETURN

```

The display goes blank except for the prompt. To verify the change, reexamine 0200. Note that you can change all four locations just by entering more data as the cursor moves right. To leave a location unchanged, press the space bar, and the cursor will skip over it. When you have changed or skipped the fourth location, the display will go blank.

However, you can continue at the next higher address by simply pressing the / key again. So you can change a memory location (after examining it) as follows:

- 6. Press /.

- 7. Enter the data as two hexadeeimal digits, starting with the more significant digit.

If you enter the data incorrectly, press ESC and / to start over. The address at the left will be the same as before.

Note that the monitor does not actually change memory until you enter the second digit. Cheek this by entering F2 into location 0200; verifying that it is there; pressing 0, ESC; and then examining 0200 again. It should still contain F2; the 0 was never actually stored in memory.

# PROBLEM 0-3

Enter the following data into 0200 through 0202:

| Memory Address (hex) | Memory Contents (hex) |

|----------------------|-----------------------|

| 0200                 | A9                    |

| 0201                 | 6A                    |

| 0202                 | 00                    |

Verify the values after you enter them.

# PROBLEM 0-4

Try changing address ECA2 to A4. What do you find when you examine it again? Remember that ECA2 is in read-only memory, not in read/write memory.

# **RUNNING A PROGRAM**

To run a program, press ESC or RESET to restore the prompt. You must first tell the AIM where the program begins by pressing \* (seeond key from the right in the top row). Note that \* is an upperease character, so you must press SHIFT to type it, just as if you wanted a capital letter on a typewriter. Enter the starting address as four hexadecimal digits, omitting leading zeros, and press RETURN. If you now press G and RETURN, the AIM will run your program.

A simple example is the single instruction BRK (FORCE BREAK), which makes the AIM return control to the monitor. We can enter and run this program as follows.

- 1. Press ESC or RESET to get the prompt.

- 2. Press M to examine memory.

- 3. Press 2,0,0, RETURN to examine address 0200. We will start (and finish) our program there. Note that we have omitted the leading zero.

- 4. Press /, 0, 0, RETURN to put 00 in 0200. 00 is the hexadecimal version of BRK; you can look it up on your programming card or in Table AI-1 of this book.

- 5. Press \*,2,0,0, RETURN to make the starting address 0200.

- 6. Press G, RETURN to run the program.

What happens? All the computer does is display 0201 and some other information that we will discuss later. We do not know whether anything happened, except that the AIM did not wander off (aimlessly!). We will present more impressive programs with actual results in Laboratory 1.

# PROBLEM 0-5

Enter and run BRK in 022A. What does the display show after you run it?

# PROBLEM 0-6

Enter and run BRK in ECA2. What happens and why? Was BRK ever stored in memory?

# **KEY POINT SUMMARY**

- 1. The AIM 65 has a monitor program stored in read-only memory (ROM). This memory is nonvolatile, and you cannot change it.

- 2. You can initialize the AIM and transfer control to its monitor by pressing the RESET button.

- 3. The AIM has read/write memory (RAM) in addresses 0000 through 03FF. This memory is volatile (its contents change when power is lost), and you can change it.

- 4. Some read/write memory is reserved, either by the monitor or by the microprocessor. We will use addresses 0200 through 03FF for programs and data and 0000 through 00DE for data only.

- 5. Each memory location has a 16-bit address (four hexadecimal digits); its contents are an 8-bit number (two hexadecimal digits).

- 6. You can examine four successive memory addresses by pressing the M key, entering the lowest address, and pressing the RETURN key. The contents of the four locations appear on the display from left to right. You can then change them by pressing / and entering new data (or spaces if you want to leave locations unchanged). You can continue examining successively higher addresses by pressing the space bar, and you can continue changing memory by pressing /. These procedures let you examine memory and put programs and data in it.

- 7. You can make the AIM run a program by entering its starting address (pressing \*, address, RETURN) and then pressing G and RETURN.

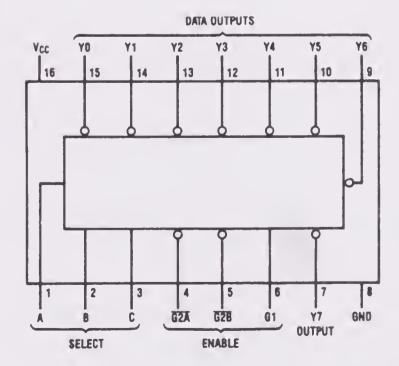

# WRITING AND RUNNING SIMPLE PROGRAMS

# **PURPOSE**

To learn how to write, load, and run simple programs.

# REFERENCE MATERIALS

- L. A. LEVENTHAL, Introduction to Microprocessors: Software, Hardware, Programming, Prentice-Hall, Englewood Cliffs, NJ, 1978, pp. 40–63, 72–104.

- L. A. LEVENTHAL, 6502 Assembly Language Programming, Osborne/McGraw-Hill, Berkeley, CA, 1979, Chapter 4.

- R. J. TOCCI and L. P. LASKOWSKI, *Microprocessors and Microcomputers: Hardware and Software*, 2nd ed., Prentice-Hall, Englewood Cliffs, NJ, 1982, pp. 95–99 (computer words), 99–101 (instruction words), 112–119 (hardware and software), 163–164 (program counter), 165–166 (accumulator), 310–311 (microprocessor instruction sets),

311–316 (6502 registers), 317–322 (6502 instruction set and addressing modes), 341 (memory-register transfers).

W. J. WELLER, *Practical Microcomputer Programming: The* 6502, Northern Technology Books, Evanston, IL, 1980, Chapters 2–5.

AIM 65 User's Guide, Dynatem, Irvine, CA, 1979, Chapter 2.

# WHAT YOU SHOULD LEARN

- 1. How to load programs into memory.

- 2. How to determine the length of instructions.

- 3. Flow to place addresses in instructions.

- 4. How to examine the results of programs.

- 5. How to make the 6502 do simple arithmetic and logic.

- 6. How to examine registers.

- 7. How to change registers.

# **TERMS**

Absolute addressing an addressing mode in which the instruction contains the actual address required to execute it. In 6502 terminology, absolute addressing refers to direct addressing with 16-bit addresses.

Accumulator a register that holds one operand and, subsequently, the result in most arithmetic and logical operations.

Addressing modes the methods for specifying the addresses used to execute an instruction. Common modes include direct, immediate, indexed, and relative.

Assembler a program that converts assembly language programs into a form (machine language) that a computer can execute directly. The assembler translates mnemonic operation codes and names into their numerical equivalents and assigns locations in memory to data and instructions.

Assembly language a computer language that allows the programmer to use mnemonie operation codes, labels, and names to refer to their numerical equivalents.

Comment part of a program that has no purpose other than documentation. Comments are neither translated nor executed; they are simply eopied into the program listing.

**Direct addressing** an addressing mode in which the instruction contains the actual address required to execute it. The 6502 has two types of direct addressing: zero-page (requiring only an 8-bit address on page 0) and absolute (requiring a full 16-bit address).

Logical shift a shift that fills vacated bits with zeros.

Machine language the programming language that the computer can execute directly with no translation other than numerical conversions.

Mnemonic name that suggests something's purpose or function.

Operation code (op code) part of an instruction that tells what operation it performs.

Page a subdivision of memory. In 6502 terminology, a page consists of 256 bytes with the same 8 most significant address bits; for example, page C6 consists of addresses C600 through C6FF.

Page number the identifier for a memory page; in 6502 terminology, the 8 most significant bits of a memory address.

**Program counter** a register that contains the address of the next instruction to be fetched from memory.

Register a storage location inside the CPU.

**Zero-page addressing** a type of direct addressing in which the instruction contains only an 8-bit address on page 0. That is, page 0 is implied.

# 6502 INSTRUCTIONS

AND logically AND the accumulator with a memory location.

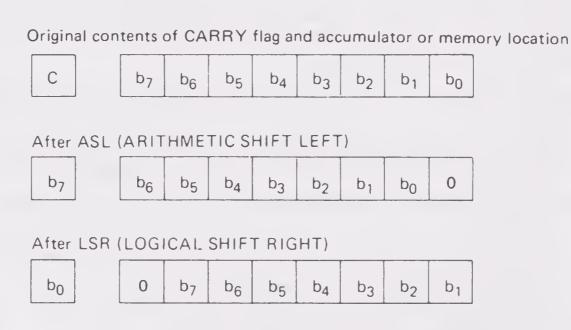

ASL arithmetic shift left; shift the accumulator or a memory location left 1 bit and clear the least significant bit (see Figure 1-1).

EOR logically EXCLUSIVE OR the accumulator with a memory location.

LDA load accumulator from a memory location.

LDX(Y) load index register X(Y) from a memory location.

LSR logical shift right; shift the accumulator or a memory location right 1 bit and clear the most significant bit (see Figure 1–1).

ORA logically (INCLUSIVE) OR the accumulator with a memory location.

STA store accumulator in a memory location.

STX(Y) store index register X(Y) in a memory location.

FIGURE 1-1. 6502 shift instructions ASL and LSR.

### DATA TRANSFER PROGRAM

Our first program simply moves the contents of memory location 0040 (hex) to 0041. The computer here provides the equivalent of an electrical connection between the two locations.

The program is

LDA \$40 ;GET DATA

STA \$41 ;MOVE DATA

BRK :RETURN TO MONITOR

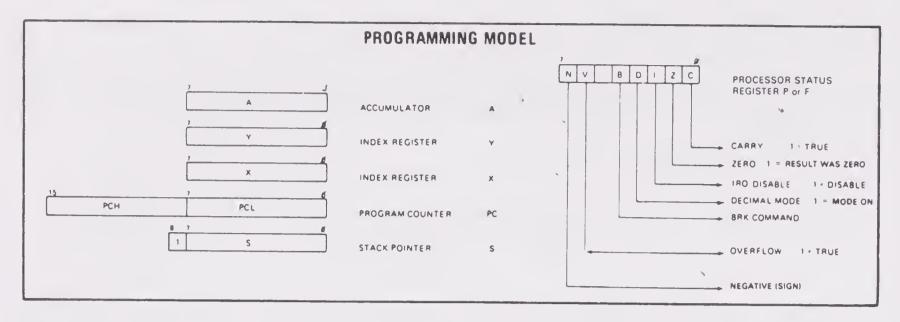

We are using the format of the AIM 65 assembler (see Figure 1–2); \$ in front of a number means "hexadecimal." The comments (preceded by semicolons) act only as documentation and do not affect the program. Figure 1–3 is a programming model of the 6502 microprocessor.

### Before a number:

\$ - hexadecimal

% - binary

@ - octal

The default case (i.e., unmarked) is decimal.

# Other symbols:

# - immediate addressing

between a base address and the designation of an index register (X or Y)

' - before an ASCII character

; - before a comment

A space is required after a label and after an operation code. Parentheses around an address indicate that it is to be used indirectly (i.e., it contains an address rather than the actual data). The default addressing mode is absolute (direct).

FIGURE 1–2. Format for the AIM 65 assembler.

Let us now look at each instruction in detail:

- 1. LDA \$40 loads the accumulator with the contents of memory location 0040. The \$ means "hexadecimal," and the leading zeros can be omitted as in common practice. Remember, the address is four hexadecimal digits (16 bits) long, but the data stored there is two digits (8 bits) long.

- 2. STA \$41 stores the accumulator in location 0041. Here again, the address is four digits long, whereas the data is two digits long.

- 3. BRK returns control to the AIM's monitor. You should put it at the end of every program.

FIGURE 1-3. Programming model of the 6502 microprocessor.

One way to load a program into memory is to look up the hexadecimal operation codes on the Programming Reference Card (see Table A1–1). We could then enter the program in hexadecimal as we did in Laboratory 0. Note that most instructions have different operation (op) codes for different addressing modes. Each operation code is followed by two numbers: the one under n indicates how many clock cycles the instruction takes to execute, while the one under # indicates how many bytes of memory it occupies. We will explain the addressing modes as we use them.

A handy feature of the AIM is that it will translate mnemonic operation codes into hexadecimal numbers. The monitor's Instruction Mnemonic Entry (I) command lets us enter programs in assembly language (i.e., referring to the instructions by name) rather than in machine language (i.e., numbers only). Assembly language is obviously much easier to read and remember than machine language, since it is based on meaningful names (*mnemonics*) rather than on arbitrary numbers.

You can enter programs using mnemonics as follows:

- 1. Press I. The AIM will respond with the current starting address. To change it, type \* (uppercase) followed by the address you want and RETURN.

- 2. Once you have the correct starting address, enter the three-letter operation code for the first instruction. If an operand is needed, enter it in hexadecimal according to a format from Table 1–1. When you complete the instruction and press the space bar, the AIM will first display the program counter, hexadecimal operation code, and instruction. It will then display the program counter again, this time along with the machine language version of the instruction. Finally, it will display the next available address, and you may continue entering instructions or exit by pressing ESC.

Mnemonic entry works well only if you turn the printer on (by pressing CTRL and PRINT simultaneously). With the printer off, the output appears only briefly on the display; this is difficult to follow unless you have quick reactions and a photographic memory. Remember to turn the printer off when you no longer need it.

If an instruction (such as BRK) does not require an operand, the AIM will take control as soon as you enter the third letter. It will automatically display the program counter, hexadecimal operation code, and instruction. You may then proceed as usual.

The AIM indicates undefined operation codes or improper operands with a simple ERROR message. This usually means that you made a typing mistake or one of the common errors we will describe later. If you make a mistake before completing an operation code or address, you can correct it immediately. Pressing DEL (rightmost key in the middle row) erases the last character and moves the cursor left. Note that DEL works only if you have not completed an entry; it will not, for example, move the cursor back if you have finished a three-letter operation code (say, typed LDX instead of LDY). Section 3.5.1 of the AIM 65 User's Guide describes several ways to correct mistakes.

TABLE 1–1 MNEMONIC ENTRY FORMATS FOR ADDRESSING MODES

| Addressing Mode       | Operand Format    |

|-----------------------|-------------------|

| Immediate             | #HII <sup>1</sup> |

| Zero-page             | iHI               |

| Zero-page, X          | нн, х             |

| Zero-page, Y          | HH, Y             |

| Accumulator           | Λ                 |

| Absolute              | HHHH              |

| Absolute, X           | нин, х            |

| Absolute, Y           | нини, Ү           |

| Relative <sup>2</sup> | HH or HIHH        |

| Indexed indirect      | (HH, X)           |

| Indirect indexed      | (HH), Y           |

| Absolute indirect     | (ПННН)            |

<sup>&</sup>lt;sup>1</sup>H represents a hexadecimal digit; a leading zero may not be omitted.

Program 1–1 contains both hexadecimal (machine language) and mnemonic-entry versions of the data transfer program. Mnemonic entry differs from AIM 65 assembly language as follows:

- 1. You need not indicate that a number is hexadecimal. In fact, no other number systems are allowed. Thus, for example, you must enter address 0040 as 40, not \$40. Entering \$40 will result in an error message.

- 2. You cannot omit leading zeros except when the result is a valid format. Thus you must enter 0 as 00 and 200 as 0200. You can, however, omit the page number from 0040 and enter it as 40. Entries such as #0 and 20F will cause error messages.

<sup>&</sup>lt;sup>2</sup>For conditional branches, you may enter the displacement from the program counter as a two-digit relative offset or as a four-digit absolute address. In the second alternative, the monitor computes the relative offset automatically.

PROGRAM 1-1

| Memory<br>Address<br>(Hex) | Memory<br>Contents<br>(Hex) | Instruction<br>(Mnemonic) |

|----------------------------|-----------------------------|---------------------------|

| 0200                       | A5                          | LDA 40                    |

| 0201                       | 40                          |                           |

| 0202                       | 85                          | STA 41                    |

| 0203                       | 41                          |                           |

| 0204                       | 00                          | BRK                       |

Note the following in Program 1–1:

- 1. We have used zero-page (direct) addressing for both LDA and STA; the byte of memory following the operation code contains the address. This address is actually 16 bits long, but if its 8 most significant bits are all zeros, we can omit them and use zero-page addressing. This is like the common practice of referring to an interval of less than a minute as, for example, "20 seconds" rather than as "zero minutes and 20 seconds." If the 8 most significant bits of the address are not all zeros, we cannot omit them and must use absolute (direct) addressing.

- 2. In zero-page addressing, the second byte of the instruction contains an address. Note the LDA \$40 means "load the accumulator from address 0040." That location could contain any 8-bit number; it need not contain 40.

- 3. The instructions vary in length. LDA \$40 and STA \$41 require two bytes of memory, whereas BRK requires only one.

Let us now run Program 1–1 with 6C in 0040. The answer should be 6C in 0041. You should elear 0041 before running the program to prove that the computer is actually doing something.

# ENTERING AND RUNNING THE DATA TRANSFER PROGRAM

To enter Program 1-1 and the test data, and then run the program, proceed as follows:

Enter Program

- 1. Press RESET or ESC if the prompt is not showing. If the printer is off, turn it on by pressing CTRL and PRINT simultaneously.

- 2. Start mnemonie entry at address 0200 with the key sequenee

3. Enter the program in mnemonic form with the key sequence

L D A 4 O SPACE S T A 4 1 SPACE B R K ESC

You can verify the entries by comparing the printed machine language instructions with the memory contents in Program 1–1.

Enter Data

1. Examine 0040 with the key sequence

M 4 0 RETURN

2. Enter the data (6C) and clear 0041 with the key sequence

/ 6 C 0 0 ESC Note that you must enter the test data into memory in addition to the program.

Run Program

You can now execute the program as follows:

1. Establish the starting address with the key sequence

\*

2

0

0

RETURN

2. Make the computer run the program by pressing

G RETURN

Remember, the program starts in 0200. The final RETURN transfers control to it; control returns to the monitor when the computer executes BRK.

**Examine Results**

Finally, you can examine the data and the result (after running the program) with the key sequence

M 4 0 RETURN

Remember, the program stores the result in 0041. The computer does not tell you the answer (regardless of what some fiction writers think). All the computer does is execute the program (which takes about 6 microseconds) and return control to the monitor (since you put BRK at the end).

# PROBLEM 1-1

Run Program 1–1 with the following data:

a. F0

b. 28

# PROBLEM 1-2

Revise Program 1–1 to do the following:

- a. Store the result in 0042.

- b. Move the contents of 0041 to 0040.

# PROBLEM 1-3

Revise Program 1–1 to use index register X instead of the accumulator. How would you make it use register Y?

# PROBLEM 1-4

Revise Program 1–1 to transfer data from 0380 (hex) to 0381 (hex). Now you must use absolute addressing instead of zero-page addressing. Note in the machine language output that 2-byte absolute addresses are loaded upside down; the order in a 3-byte instruction is operation code, less significant address byte, and more significant address byte. LDA \$0380, for example, is translated into AD (LDA with absolute addressing), 80 (less significant address byte), and 03 (more significant address byte).

# PROBLEM 1-5

Write and run a program that moves the contents of location 0040 to 0042 and the contents of 0041 to 0043.

# Sample Problem

Data:

$$(0040) = C6$$

$(0041) = 5E$

Result:  $(0042) = C6$

$(0043) = 5E$

How much longer is the program if the addresses are 0380 through 0383 instead of 0040 through 0043?

# PROCESSING DATA

Of course, we usually want to process the data rather than just move it around in memory. For example, the following program shifts each data bit left one position and clears the

least significant bit before storing the result in 0041. The computer here mimies an 8-bit shift register. The program is

> LDA \$40 ;GET DATA ASL A SHIFT DATA LEFT STA \$41 STORE RESULT BRK RETURN TO MONITOR

The only new instruction is ASL A, which shifts the accumulator left 1 bit and elears the least significant bit. Note that ASL A is a 1-byte instruction; it does not require an address, since the data is in the accumulator.

Run this program (Program 1-2 contains hexadeeimal and mnemonie-entry versions) with the data 01 (00000001 binary) in 0040. The result should be 02 (00000010 binary) in 0041. Why? Use Table 0-1 to convert hexadecimal numbers to binary, and vice versa. For example, 01 hex is 00000001 binary since 0 hex is 0000 binary and 1 hex is 0001 binary. Going the other way, 00000010 binary is 02 hex since 0000 binary is 0 hex and 0010 binary is 2 hex. You must split the byte down the middle to form two hexadeeimal digits.

| PROGRAM 1-                 | 2                           |                           |

|----------------------------|-----------------------------|---------------------------|

| Memory<br>Address<br>(Hex) | Memory<br>Contents<br>(Hex) | Instruction<br>(Mnemonic) |

| 0200                       | A5                          | LDA 40                    |

| 0201                       | 40                          |                           |

| 0202                       | OA                          | ASL A                     |

| 0203                       | 85                          | STA 41                    |

| 0204                       | 41                          |                           |

| 0205                       | 00                          | BRK                       |

# PROBLEM 1-6

Run Program 1–2 with the following data:

- a. 40. The result should be 80.

- b. C7. The result should be 8E. What happens to the 1 that is originally at the far left?

# PROBLEM 1-7

Can you revise Program 1-2 to use an index register? Are there instructions that shift the index registers? The accumulator is the only register we can use for data processing.

# PROBLEM 1-8

Make Program 1–2 shift the data right instead of left. (*Hint*: Replace ASL A with LSR A.)

# Sample Problems

The parentheses around a memory address indicate "contents of."

What happens to the 1 that is originally at the far right?

# PROBLEM 1-9

Revise Program 1–2 to shift the contents of two successive locations and store the results in the next two locations. That is, the new program should store the shifted version of 0040 in 0042 and the shifted version of 0041 in 0043.

# Sample Problem

Data:

$$(0040) = 01$$

$(0041) = 08$

Result:  $(0042) = 02$

$(0043) = 10$

# LOGICALLY ANDING TWO VALUES

We can easily convert the left-shift program into a logical AND program. The task now is to logically AND the contents of 0040 and 0041 and place the result in 0042. Here the computer mimics two 7408 quadruple two-input TTL AND gates. Note, however, that a 6502 can perform many different arithmetic and logical functions. The logical AND program is

| LDA | \$40 | GET FIRST OPERAND             |

|-----|------|-------------------------------|

| AND | \$41 | ;LOGICALLY AND SECOND OPERAND |

| STA | \$42 | STORE RESULT                  |

| BRK |      |                               |

Program 1–3 is the mnemonic-entry version. We have started it in 0210, so we can leave Program 1–2 in memory for later use. Remember that AND works as follows on each bit:

| Input 1 | Input 2 | Input 1 AND Input 2 |

|---------|---------|---------------------|

| 0       | 0       | 0                   |

| 0       | 1       | 0                   |

| 1       | 0       | 0                   |

| 1       | l       | 1                   |

| PROGRAM 1-3                | }                           |                           |

|----------------------------|-----------------------------|---------------------------|

| Memory<br>Address<br>(Hex) | Memory<br>Contents<br>(Hex) | Instruction<br>(Mnemonic) |

| 0210                       | A5                          | LDA 40                    |

| 0211                       | 40                          |                           |

| 0212                       | 25                          | AND 41                    |

| 0213                       | 41                          |                           |

STA 42

BRK

85

42

00

Enter Program 1–3 into memory and run it for the following sample eases. Remember to start at 0210, *not* at 0200. Use Table 0–1 to convert hexadecimal values into binary to check your results.

0214

0215

0216

# PROBLEM 1-10

Make Program 1–3 logically OR two locations and store the result. How would you get a logical EXCLUSIVE OR? Refer to Table 3–3 if you cannot remember how logical functions work.

# Sample Problem

Data: (0040) = 23

(0041) = 34

Result: (0042) = 37 for logical OR

(0042) = 17 for logical EXCLUSIVE OR

-

# **EXAMINING REGISTERS**

One way to determine what a program is doing is to examine the processor's registers. On the AIM, you can examine registers by pressing the R key. With the printer on, you will see the following line of identification eodes:

You will then see the current register values in the following order from left to right:

PC is the program counter (a 16-bit register), P is the processor status register, and S is the stack pointer.

If the printer is off, the identification line disappears and you must use Table 1–2 to figure out what the values mean. The program counter is obvious, since it is the only four-digit register. Taping a copy of the identification line to the AIM will help you identify the other registers. You can exit from the register display by pressing ESC.

We have not yet discussed some registers. We will describe the status register in Laboratory 2 and the stack pointer in Laboratory A. The program counter contains the address of the next instruction that the CPU will fetch from memory. Each time the CPU uses the program counter, it adds 1 to its contents. Thus the computer will execute instructions sequentially unless it is specifically told to do otherwise. Since the program counter is 16 bits long, it can hold a complete memory address.

TABLE 1—2 ORDER IN REGISTER DISPLAY (LEFT TO RIGHT)

| Designation | Meaning                       |

|-------------|-------------------------------|

| * * * *     | Program counter (four digits) |

| PS          | Status (P) register (flags)   |

| AA          | Accumulator                   |

| XX          | Index register X              |

| YY          | Index register Y              |

| SS          | Stack pointer                 |

# **CHANGING REGISTERS**

You can change a register by entering either two or four (program counter only) hexadecimal digits after pressing one of the following keys:

- 1. \* for program counter (remember, \* is upperease). You must type RETURN after completing the entry.

- 2. A for accumulator.

- 3. X for index register X.

- 4. Y for index register Y.

- 5. S for stack pointer.

- 6. P for processor status register.

For example, say we want to put 4C in index register Y. All that we must do is press Y, 4, C. The AIM will load 4C into Y; we can verify this by pressing R.

There are two things to watch here. First, note that you cannot change the register display directly (that is, by pressing /), nor can you change more than one register with a single command. Second, the program counter is special. It can accept a four-digit entry, and you can omit leading zeros. However, you must press RETURN after changing it. With the other registers, you cannot omit a leading zero, but you need not press RETURN. The AIM takes control as soon as you enter the second digit.

Run Program 1-2 with (0040) = C7. What are the final contents of the accumulator and program counter? Does it matter if you clear the accumulator initially (i.e., load it with 00)?

# PROBLEM 1-11

Run Program 1-3 with (0040) = 23 and (0041) = 34. What are the final contents of the accumulator and program counter? Does it matter if you clear the accumulator initially? What happens to values you load into the index registers before running Program 1-3? Try different values (e.g., 00, FF, AA, 55) and see if the results vary. What happens if you reset the computer after loading the index registers? What happens if you enter 6F into the stack pointer (S register) and then press RESET?

# **COMMON OPERATING ERRORS**

By now you have undoubtedly discovered the following common errors that plague the AIM user:

1. Forgetting to enter operands properly in mnemonic entry. You must enter operands as two or four hexadecimal digits with no leading \$; you cannot omit leading zeros. Typical problem cases are LDA #0 (you must enter 00, not just 0) and LDA \$206 (you must enter 0206, not 206 or \$206).

- 2. Forgetting to press M before examining memory or / before changing it. If you begin with the address or data, you will confuse the AIM completely and start a whole series of problems. The AIM will think the first digit is a command.

- 3. Trying to change the register display. You must press a command key to change a register, and you can change only one at a time.

- 4. Entering a new command before completing the current one. The AIM is remarkably tolerant of this and will often proceed correctly with the new command. Sometimes, however, the AIM cannot figure out what you want. If, for example, you try to examine the registers during mnemonic entry, the AIM will probably think R is the first letter of an operation code. To avoid this problem, always press ESC and restore the AIM's prompt before entering a command.

- 5. Misinterpreting data as instructions. For example, you may set the starting address to 0040 instead of 0200. This mistake eauses the AIM to execute the data as if it consisted of instructions. The way to avoid this is to keep programs and data clearly separated in your mind and in all your work.

- 6. Forgetting to enter a starting address. You must enter a starting address before running a program or loading one using mnemonic entry.

- 7. Forgetting to run the program—that is, entering the program and the data and waiting for something to happen. This is like entering data into a calculator and waiting for it to produce a result. Neither a computer nor a calculator will do anything until directed to run a program.

- 8. Starting program execution at the wrong address. The computer will execute whatever it finds at the address you specify. This is a common error if you have several programs in memory or if you vary the starting address. The way to ensure that you have the correct address is to mark it on each program listing.

Errors will often make the AIM lose its way and never return to the monitor. If this happens, press RESET. Always eheek your program and data before proceeding; the computer will probably have changed them (unless you are much luckier than I am).

# **KEY POINT SUMMARY**

- 1. Most simple 6502 programs use the accumulator as the center of operations. They begin by loading the accumulator from memory and end by storing the result (from the accumulator) in memory.

- 2. The most straightforward addressing mode is direct addressing, in which the instruction contains the address it needs. This address follows the operation code in memory.

- 3. If the 8 most significant bits of a direct address are all zeros, we can omit them and use zero-page addressing. This makes page 0 special, since instructions that use it occupy less memory and execute faster than instructions that use other pages.

- 4. If the 8 most significant bits of a direct address are not all zeros, we eannot omit them and must use absolute addressing. An absolute address occupies 2 bytes of memory, with the 8 most significant bits in the second byte. That is, the address is stored upside down.

- 5. To make the computer do something useful, you must enter the program and data into memory, run the program, and examine the results. The I (mnemonie entry) command lets you enter programs in simplified assembly language rather than as hexadeeimal numbers (maehine language).

- 6. The 6502's accumulator is special, because it is the only register that can be used in most arithmetic and logical operations.

- 7. You can examine the 6502's registers by pressing the R key. The AIM displays identification codes and register values in the following order from left to right: program counter (four digits), status (P) register, accumulator, index register X, index register Y, stack pointer.

- 8. You can change a register by pressing one of the following keys: \* for the program counter, A for the accumulator, X for index register X, Y for index register Y, S for the stack pointer, and P for the processor status register. The program counter requires an address (four digits, but leading zeros can be omitted), followed by RETURN. The other registers require two-digit entries; a leading zero cannot be omitted, but no RETURN is necessary.

- 9. Common errors in operating the AIM include using mnemonic entry incorrectly, forgetting to press M or / before examining or changing memory, attempting to change the register display, starting one command in the middle of another, failing to enter a starting address, misinterpreting data as instructions, forgetting to run the program, and starting program execution at the wrong address.

# SIMPLE INPUT

## **PURPOSE**

To learn how to use the computer's input ports.

# PARTS REQUIRED

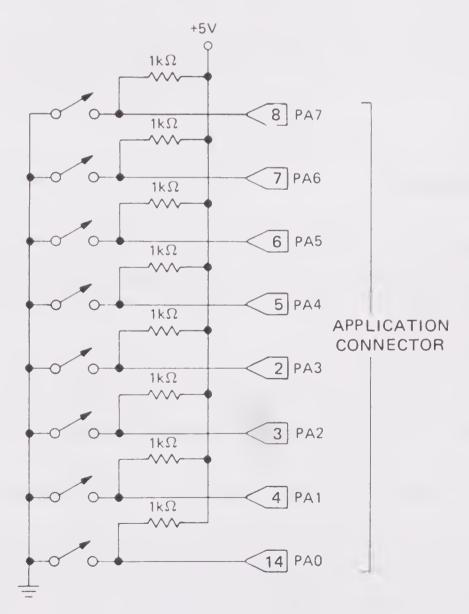

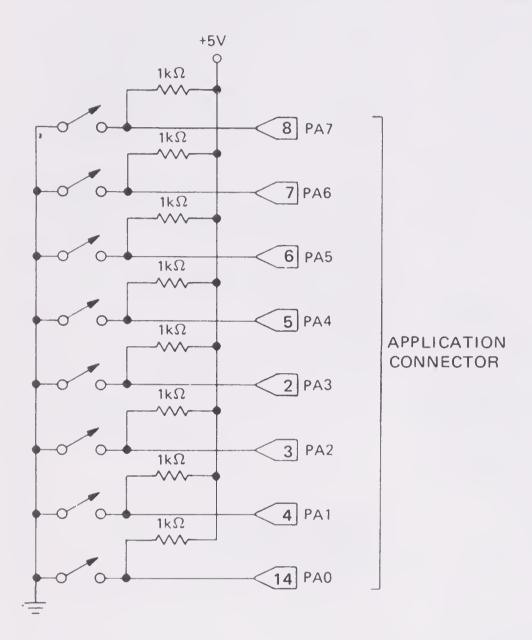

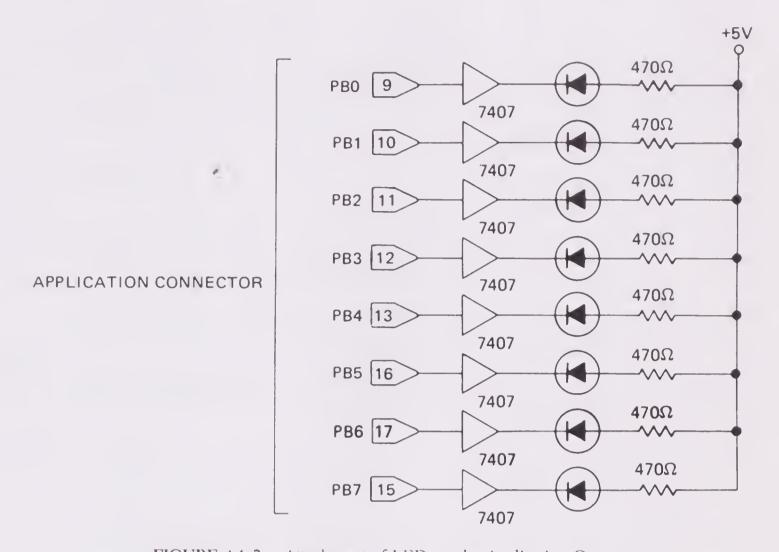

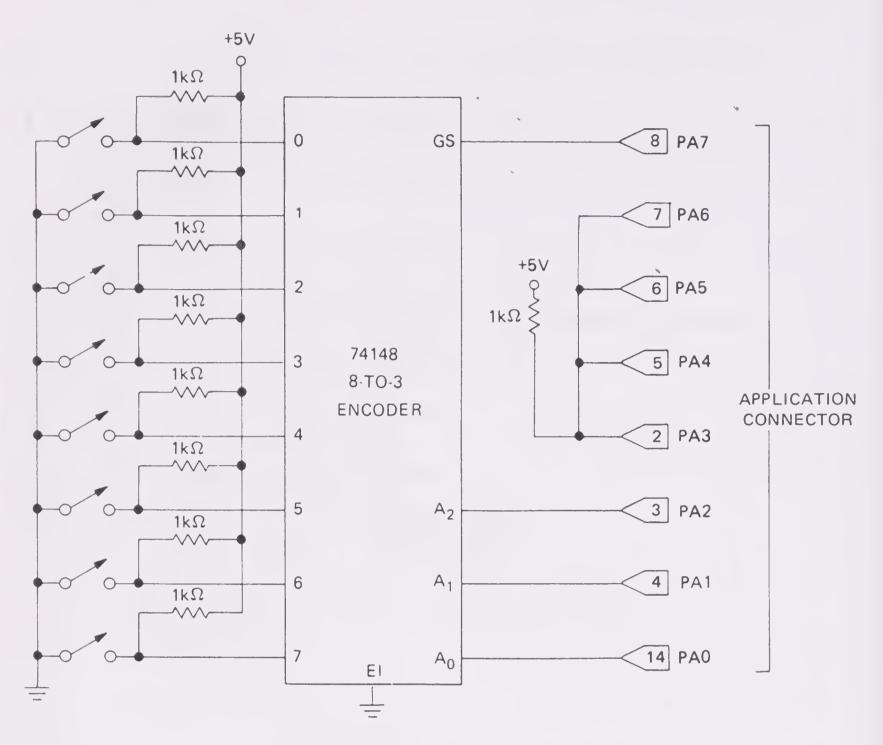

Eight switches attached to the Application Connector as shown in Figure 2–1. Table 2–1 contains the pin assignments.

# REFERENCE MATERIALS

L. A. LEVENTHAL, *Introduction to Microprocessors: Software, Hardware, Programming*, Prentice-Hall, Englewood Cliffs, NJ, 1978, pp. 72–104, 369–370.

- L. A. LEVENTHAL, 6502 Assembly Language Programming, Osborne/McGraw-Hill, Berkeley, CA, 1979, pp. 11–1 to 11–12, 11–39 to 11–49.

- R. J. TOCCI and L. P. LASKOWSKI, *Microprocessors and Microcomputers: Hardware and Software*, 2nd ed., Prentice-Hall, Englewood Cliffs, NJ, 1982, pp. 26 (hexadecimal arithmetic), 31–32 (AND function), 62–63 (arithmetic circuits), 169–171 (status register), 174–180 (arithmetic-logic unit), 203–206 (simple input port), 312–316 (6502 flags), 319 (immediate addressing), 338–340 (compare and bit test instructions), 346–355 (conditional branch instructions).

AIM 65 User's Guide, Dynatem, Irvine, CA, 1979, pp. 6-1 to 6-19.

R6500 Microcomputer System Programming Manual, Rockwell International, Semiconductor Products Division, Newport Beach, CA, 1979, Chapters 2–5.

# WHAT YOU SHOULD LEARN

- 1. How the 6502 identifies I/O ports and which instructions are commonly used for I/O.

- 2. How to determine whether a switch is open or closed.

- 3. Which bit positions can be accessed most easily.

- 4. How to examine the flags.

- 5. How to handle a series of switch closures.

- 6. How to recognize a starting (synchronization) character.

TABLE 2–1 APPLICATION CONNECTOR PIN ASSIGNMENTS FOR PORT A OF THE USER VIA

| Assignment  | Pin |

|-------------|-----|

| Bit 0 (PA0) | 14  |

| Bit 1 (PA1) | 4   |

| Bit 2 (PA2) | 3   |

| Bit 3 (PA3) | 2   |

| Bit 4 (PA4) | 5   |

| Bit 5 (PA5) | 6   |

| Bit 6 (PA6) | 7   |

| Bit 7 (PA7) | 8   |

#### **TERMS**

Branch instruction see Jump instruction.

Carry flag a flag that is 1 if the last operation generated a carry from the most significant bit and 0 if it did not.

Flag a bit that indicates a condition within the computer, often used to choose between alternative instruction sequences.

Immediate addressing an addressing method in which the instruction contains the data it requires, usually immediately following the operation code in memory.

Jump instruction (or branch instruction) an instruction that places a new value in the program counter, thus departing from the normal instruction sequence. A conditional jump instruction places the new value in the program counter only if a condition is true.

**Label** a name attached to an instruction or statement in a program. The name takes on the value of the starting address in memory of the resulting machine language or assignment.

Masking singling out 1 or more bits from a group of bits.

Memory-mapped input/output assigning I/O ports to memory addresses rather than giving them their own set of addresses.

Negative flag (or sign flag) a flag that contains the most significant bit of the result of the previous operation.

Port the basic addressable unit of the computer's input/output section.

Relative addressing an addressing method in which the instruction contains the offset from a base address.

Relative offset the difference between the address to be used in an instruction and the current program counter.

Relocatable able to be placed anywhere in memory without changes; that is, capable of occupying any set of consecutive memory addresses.

Sign flag see Negative flag.

Status register a register that contains bits (flags) describing the current state of the computer.

Synchronization (sync) character—a character that is used only to synchronize the transmitter and the receiver. The character does not contain any actual information.

Zero flag a flag that is 1 if the last operation produced a zero result and 0 if it did not.

### 6502 INSTRUCTIONS

The following branch instructions all jump over the specified number of memory locations if the specified condition is true; otherwise, they proceed to the next instruction in sequence.

BCC branch if earry clear.

BCS branch if earry set.

BEQ branch if equal to zero (ZERO flag = 1).

**BMI** branch if minus (NEGATIVE flag = 1).

BNE branch if not equal to zero (ZERO flag = 0).

BPL branch if plus (NEGATIVE flag = 0).

BVC branch if overflow elear.

BVS branch if overflow set.

BIT bit test; logically AND the accumulator with a memory location but leave the accumulator unchanged. This instruction affects only the flags. BIT sets the NEGATIVE flag from bit 7 of the memory location and the OVERFLOW flag from bit 6 without considering the accumulator. The only flag that depends on the logical AND is the ZERO flag. BIT allows only zero-page and absolute (direct) addressing.

CMP compare memory and accumulator; subtract a memory location from the accumulator but leave the accumulator unchanged. This instruction affects only the flags.

# 6502 INPUT/OUTPUT INSTRUCTIONS

The 6502 has no specific input/output (I/O) instructions. Instead, it treats I/O ports as memory locations. In this approach, called *memory-mapped input/output*, any instruction that transfers data to or from memory can perform I/O. The 6502 instructions most often used for I/O are:

- LDA loads the accumulator from an input port.

- STA stores the accumulator in an output port.

- BIT (BIT TEST) sets the flags as if the data from an input port had been logically ANDed with the accumulator. The accumulator does not change.

- CMP (COMPARE MEMORY AND ACCUMULATOR) sets the flags as if the data from an input port had been subtracted from the accumulator. The accumulator does not change.

#### SIMPLE INPUT

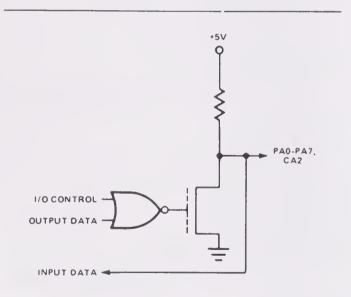

The AIM 65 has I/O ports in its on-board 6522 Versatile Interface Adapters (VIAs). Throughout this book, we will employ user VIA port A (address A001) for input and port B (address A000) for output. Starting from reset, the following program loads the accumulator from port A:

LDA \$A001 BRK

The mnemonic-entry version is Program 2–1. Open all the switches attached to port A, reset the AIM, and execute Program 2–1. What does the accumulator contain afterward?

Close the switch attached to bit 5 and execute Program 2–1 again. Now what is in the accumulator?

| Memory<br>Address<br>(Hex) | Memory<br>Contents<br>(Hex) | Instruction<br>(Mnemonic) |

|----------------------------|-----------------------------|---------------------------|

| 0200                       | AD                          | LDA A001                  |

| 0201                       | 01                          |                           |

| 0202                       | AO                          |                           |

| 0203                       | 00                          | BRK                       |

# PROBLEM 2-1

The computer interprets an open switch as \_\_\_\_ and a closed switch as \_\_\_\_ if the connections are as shown in Figure 2–1.

FIGURE 2–1. Attachment of switches to the Application Connector. The user VIA is device Z1 in the AIM schematics.

#### PROBLEM 2-2

Determine what value Program 2-1 places in the accumulator if:

- a. The switch attached to bit 2 of port A is closed.

- b. Switches attached to bits 2 and 5 are closed.

- c. Switches attached to bits 0,6, and 7 are closed.

Assume that all other switches are open.

#### PROBLEM 2-3

What happens if you replace LDA \$A001 with LDA \$A000? Does opening or closing switches affect the input? Explain the result.

Remember the following:

- 1. The standard in the computer industry is to number bit positions starting with 0 at the far right. Thus the bits in a byte are numbered 0 through 7 from right to left; bit 0 is least significant and bit 7 most significant. Figure 2–2 (shown later in this chapter) is an example of the standard numbering. Be careful—switches and other I/O devices often use other conventions (e.g., 1 to 8 or left to right).

- 2. Since A001 is not on page 0, we must use absolute addressing to refer to it. As you can see in Program 2–1, the 16-bit address occupies 2 bytes of memory, with its less significant bits first.

#### FLAGS AND CONDITIONAL BRANCHES

To have the computer determine if a switch is open or closed, we must use the flags and conditional branch instructions. Instructions that move or process data also affect the flags. A conditional branch instruction lets the computer use a flag to choose between alternative paths through a program.

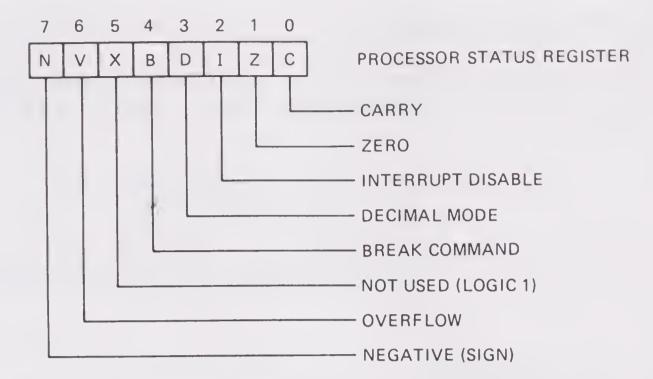

The major 6502 flags are:

C (CARRY) 1 if the last arithmetic or shift instruction produced a carry, 0 if it did not. N (NEGATIVE or SIGN) 1 if the result of the last instruction had a 1 in its most significant bit, 0 if it did not.

**Z** (**ZERO**) l if the result of the last instruction was zero, 0 if it was not zero.

Conditional branch instructions place a new value in the program counter if the specified flag has the specified value. Otherwise, they leave the program counter unchanged and the processor simply continues its normal sequence. Conditional branches make a computer "smart," that is, capable of making decisions based on current

information. The computer thus becomes an intelligent controller. Table 2–2 lists the 6502's conditional branch instructions.

| Instruction | Flag Used       | Value<br>on Which Branch<br>Occurs |

|-------------|-----------------|------------------------------------|

| BCC         | CARRY           | 0                                  |

| BCS         | CARRY           | 1                                  |

| BNE         | ZERO            | 0                                  |

| BEQ         | ZERO            | 1                                  |

| BPL         | NEGATIVE (SIGN) | 0                                  |

| BMI         | NEGATIVE (SIGN) | 1                                  |

| BVC         | OVERFLOW        | 0                                  |

| BVS         | OVERFLOW        | 1                                  |

TABLE 2-2 6502 CONDITIONAL BRANCH INSTRUCTIONS

#### WAITING FOR A SWITCH TO CLOSE

Let us now concentrate on the switch attached to bit 5 of port A (switch 5, for short). The following program waits for you to close that switch; it then returns control to the monitor. Remember that an open switch is a 1 and a closed switch is a 0 (see Figure 2–1). Program 2–2 is the mnemonic-entry version.

| WAITC | LDA | \$A001     | ; GET INPUT DATA      |

|-------|-----|------------|-----------------------|

|       | AND | #%00100000 | ; IS SWITCH 5 CLOSED? |

|       | BNE | WAITC      | ; NO, WAIT            |

|       | BRK |            |                       |

Let us now look at each instruction:

- 1. LDA \$A001 loads the accumulator from port A. WAITC is our name for the memory address in which LDA \$A001 begins. Such a name is ealled a *label*; its sole purpose is to make the program easier for a reader to follow. However, since the mnemonic-entry mode does not allow labels, we must replace them with the actual addresses to which they refer. For example, if Program 2–2 starts at 0200, WAITC is 0200, and BNE WAITC must produce a conditional branch to 0200. The name WAITC is arbitrary; we chose it because it suggests *wait*ing for a *c*losure.

- 2. AND #%00100000 logically ANDs the accumulator with the binary number 00100000. % means "binary" and # means "immediate" (i.e., the data is in the next byte of memory). The result is 0 if the switch is elosed and 00100000 if the switch is open. (Verify this!) Singling out part of a group of bits is ealled *masking*.

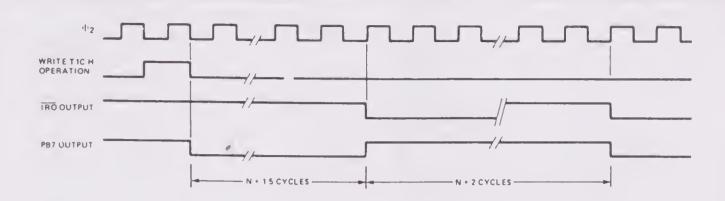

- 3. BNE WAITC makes the processor execute the instruction in address WAITC next if the ZERO flag is 0. Otherwise, the processor continues sequentially (to BRK in this ease). Note that the ZERO flag is 1 if the last result was zero.