# 6502 User's Manual

# Joseph J. Carr 6502 User's Manual

A Reston Computer Group Book Reston Publishing Company, Inc. A Prentice-Hall Company Reston, Virginia Library of Congress Cataloging in Publication Data

Carr, Joseph J. 6502 user's manual.

"A Reston Computer Group book." 1. 6502 (Microprocessor) I. Title. II. Title: Six thousand five hundred two user's manual. QA76.8.S63C37 1984 001.64 83-26887 ISBN 0-8359-7004-6 ISBN 0-8359-7002-7 (pbk.)

IBM<sup>®</sup> is a registered trademark of International Business Machines Corp. Apple<sup>®</sup> is a registered trademark of Apple Computer, Inc. AIM<sup>®</sup> is a registered trademark of Data Processing Consulting, Inc., Boulder, Colorado Touch-Tone<sup>™</sup> is a trademark of American Telephone & Telegraph DEC<sup>®</sup> is a registered trademark of Digital Equipment Corporation PDP-11<sup>™</sup> is a trademark of Digital Equipment Corporation Z-80<sup>™</sup> is a trademark of Zilog, Corp. TRS-80<sup>®</sup> is a registered trademark of Radio Shack, a division of the Tandy Corporation,

Fort Worth, Texas

© 1984 by Reston Publishing Company, Inc. A Prentice-Hall Company Reston, Virginia 22090

All rights reserved. No part of this book may be reproduced in any way, or by any means, without permission in writing from the publisher.

10 9 8 7 6 5 4 3 2 1

PRINTED IN THE UNITED STATES OF AMERICA

# Contents

### Introduction ix

| 1. | Introduction to Microprocessors and Microcomput | ers 1 |

|----|-------------------------------------------------|-------|

|----|-------------------------------------------------|-------|

**Microprocessors** 2 2 Microcomputers **Single-chip Computers** 2 **Single-board Computers** 3 Minicomputers 3 **Mainframe Computers** 4 Advantages of Microcomputers 4 Microcomputer Interfacing 5 Microcomputers in Instrument and System Design 6 6502-based Machines 7 Synertek SYM-1 8 **Ohio Scientific Superboard II** 9 Apple II and Apple III 10 **Microprocessor Fundamentals** 10 Mythical Analytic Device (MAD) 11 Central Processing Unit (CPU) 14 **Operation of MAD** 16

2. 6502 Architecture 19

6502 Internal Structure 21

Memory Allocation Restraints 26

#### 3. 6502 Pinouts 29

4. Timing and Control Signals 35 Data and Address Buses 35 **B**/W line 37 Data Bus Enable (DBE) 37 Ready  $(\overline{RDY})$ 37 Interrupt Requests ( $\overline{IRO}$  and  $\overline{NMI}$ ) 38 Reset ( $\overline{RES}$ ) 39 Synchronization (SYNC) 39 Set Overflow ( $\overline{SO}$ ) 39 6502 Clock Timing 39 **Read/Write Cycle Timing** 42 5. 6502 Addressing Modes 45 Accumulator Mode Addressing 45 **Relative Addressing Mode** 45 Immediate Addressing Mode 47 Absolute Addressing Mode 49 Implied Addressing 50 Zero Page Addressing Mode 51 Indirect Absolute Addressing Mode 52 Absolute Indexed X and Y Addressing Mode 55 Zero Page Indexed (X and Y) Addressing Mode 60 Indirect Indexed Addressing Mode 60 Indexed Indirect Addressing Mode 62 6. 6502 Status Flags 63 Flags 63 Manipulating PSR 66

#### 7. General Instruction Set 67

Instructions 67 6502 Instructions 68 Group-I Instructions 69 Load and Store Instructions (LDA and STA) 69

|     | Arithmetic Instructions (ADC and SBC) 78<br>Logical Instructions (AND, ORA, and EOR) 81<br>Compare Instructions (CMP) 83<br>Group-II Instructions 83<br>Group-III Instructions 86                   |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

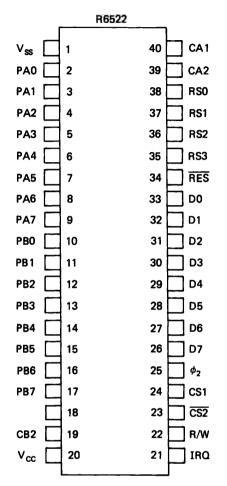

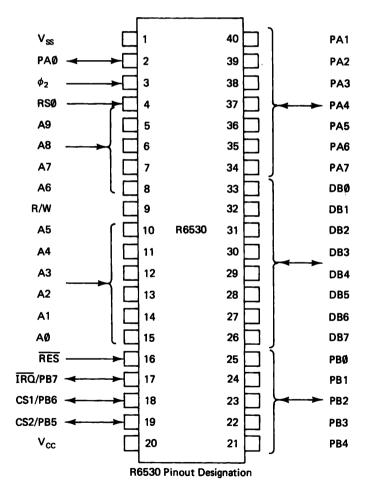

| 8.  | 65xx-Family Support Chips 101                                                                                                                                                                       |  |  |

|     | 65221026530105                                                                                                                                                                                      |  |  |

| 9.  | Device Selection and Address Decoding 109                                                                                                                                                           |  |  |

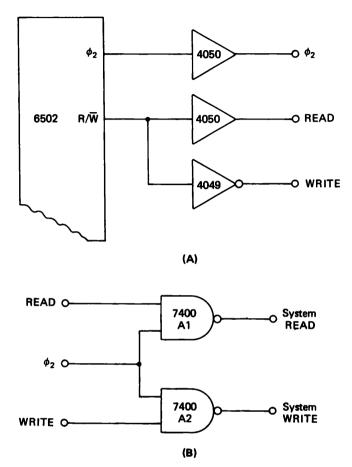

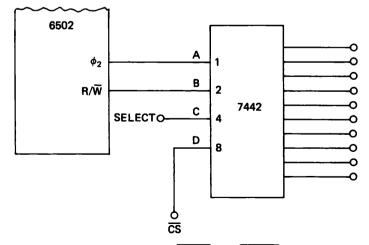

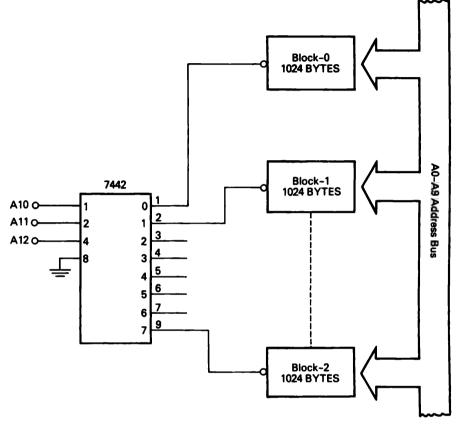

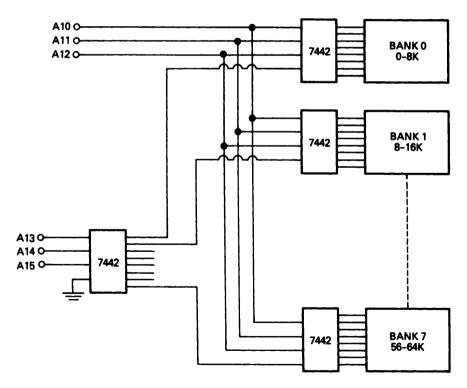

|     | Address Decoding 109<br>Generating Read/Write Signals 116                                                                                                                                           |  |  |

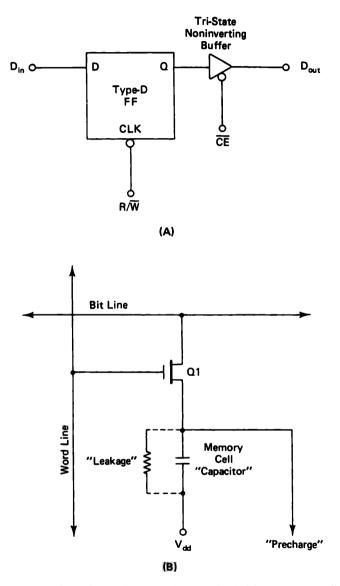

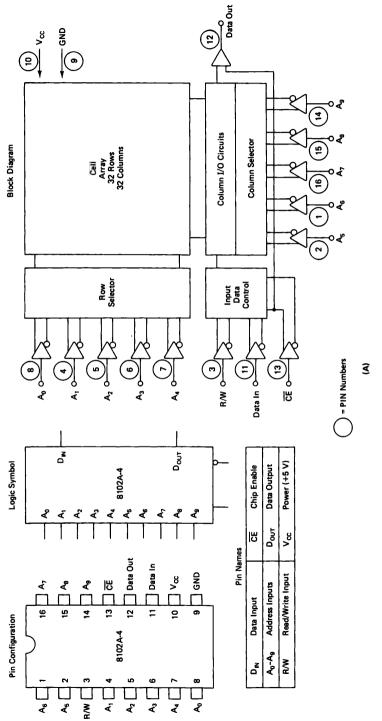

| 10. | Interfacing Memory to the 6502 121                                                                                                                                                                  |  |  |

|     | Memory Hierarchy122Types of Memory Devices1224116 16K x 1-bit Dynamic RAM125Read-only Memory (ROM) Devices131Address Block Decoding131                                                              |  |  |

| 11. | Interfacing I/O Devices to the 6502 139                                                                                                                                                             |  |  |

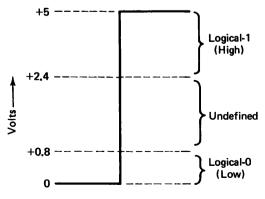

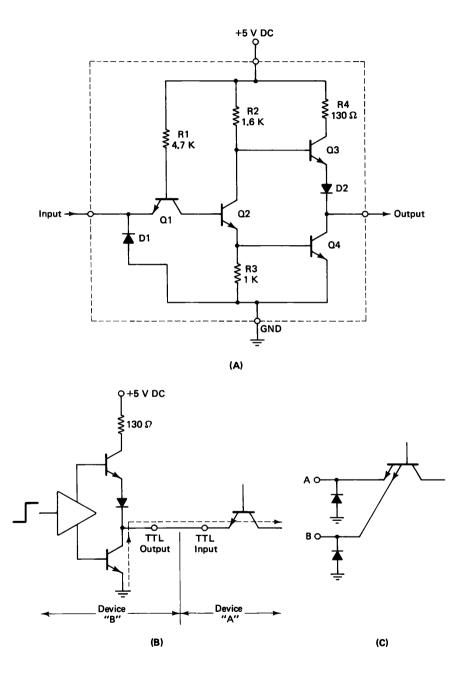

|     | Logic Families 140<br>TTL (Transistor-transistor Logic) 140<br>CMOS (Complementary Metal Oxide Semiconduc-<br>tors) 146<br>Tristate Devices 148<br>Interfacing Logic Families 149<br>Flip-flops 150 |  |  |

|     | I/O Ports: Devices and Components 155<br>Interfacing Keyboards to the Microcomputer 163                                                                                                             |  |  |

|     | Custom Keyboards, Switches, and LED Displays 169                                                                                                                                                    |  |  |

| 12. | Interfacing Peripherals to the 6502 185                                                                                                                                                             |  |  |

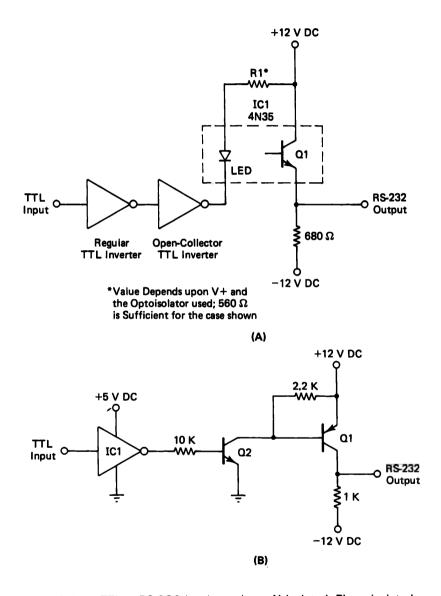

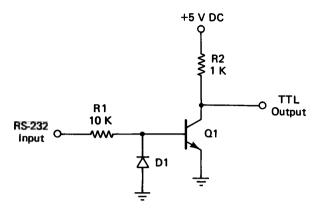

|     | Parallel Port Methods185Serial Digital Data Communications185RS-232 Interfacing201                                                                                                                  |  |  |

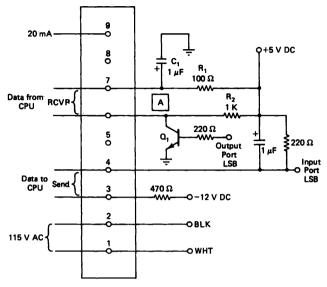

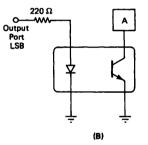

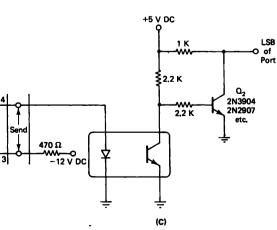

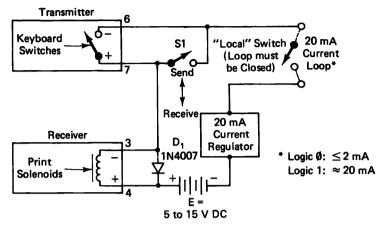

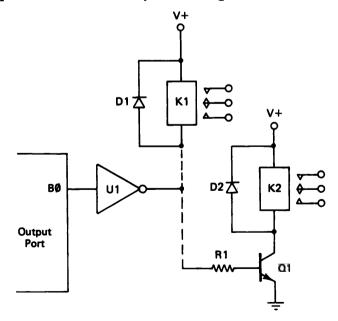

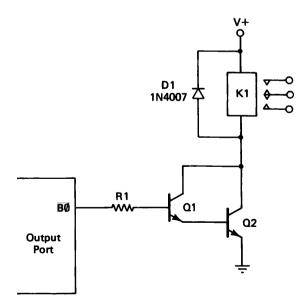

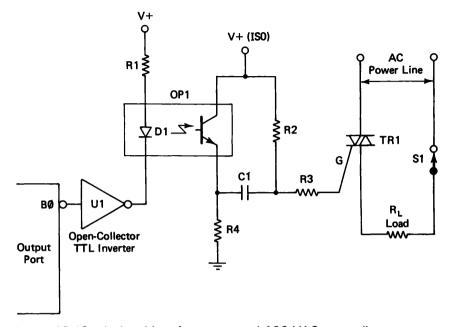

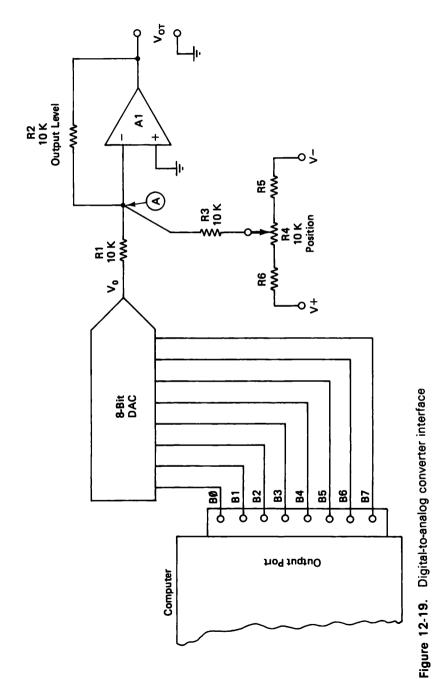

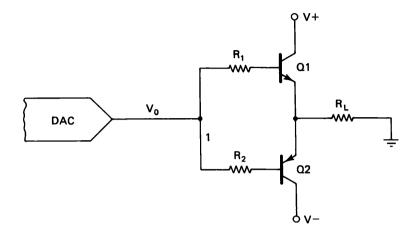

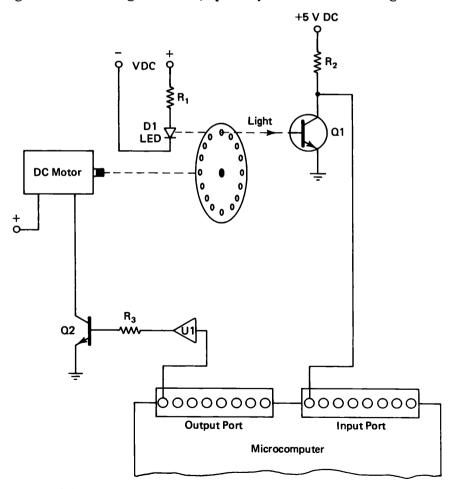

Current Loop Ports202Serial Interfacing205Controlling External Circuits213

#### 13. Interrupts 227

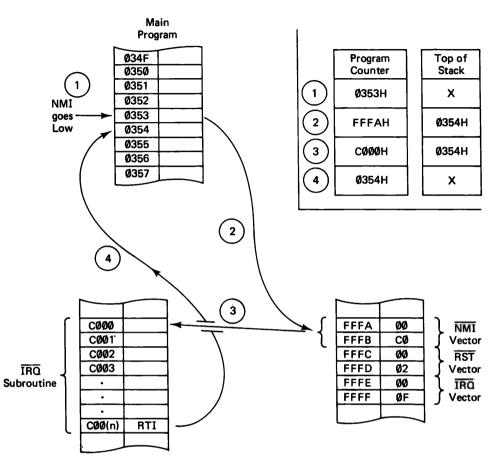

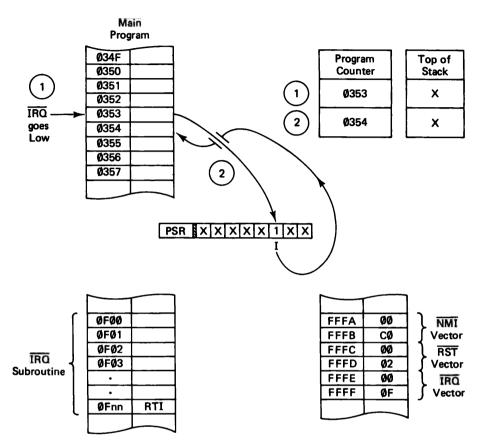

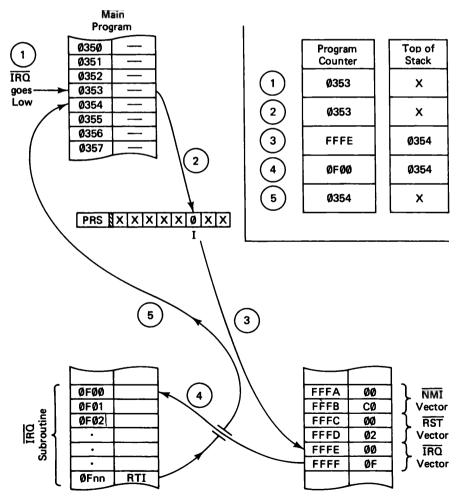

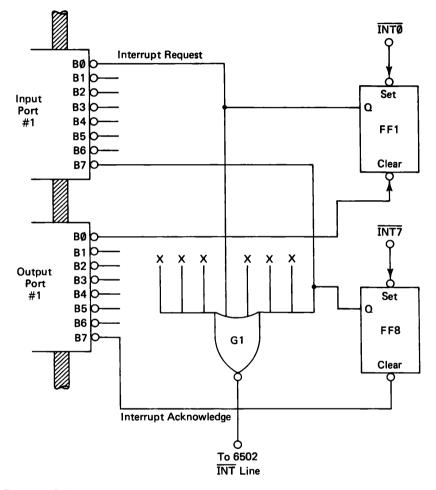

Interrupt Vectors228Nonmaskable Interrupts229Maskable Interrupt Requests230Reset Line as Interrupt232Multiple Interrupts on 6502234

- 14. Interfacing with the Apple II Bus 237

- 15. Interfacing with the KIM-1, AIM-65, and SYM-1 241

- 16. 6502 Detailed Instruction Set 245

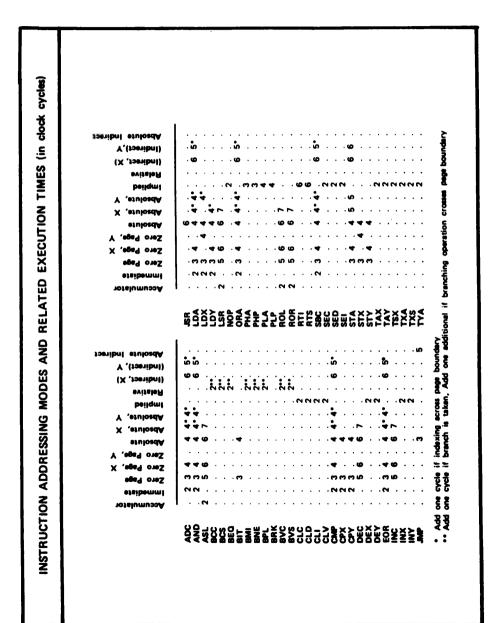

APPENDIX A. Instruction Addressing Modes and Related Execution Times 279

APPENDIX B. 6502 Instructions Sorted by Op-codes (Hexadecimal) 281

# Introduction

This book is intended to be both an instruction guide and a tool ... but mostly a utilitarian tool for the programmer/interfacer of 6502-based microcomputers. It is intended that this book become dog-eared and worn from heavy use on a programmer's table or a hacker's workbench . . . use it and abuse it, that's why I wrote it. There is no attempt in this book to show you how much the author knows about computers-you don't have time for trash like that. The information in this book was selected for its usefulness to a wide variety of readers. Like its earlier companion volume, The Z80 User's Manual (Ioseph I. Carr, Reston Publishing Company), the book is intended to collect into one place most, perhaps all, the information you need for assembly and machine language programming and for performing hardware interfacing chores. Of course, with all of the different kinds of 6502based machines on the market today, it was impossible to provide details of all machines, so I stuck pretty much to generic details applicable to any 6502-based system.

New features in this book that are not in my earlier Z80 book include a discussion of the different types of computers. My earlier assumption (which was then almost true!) was that the reader already possessed a basic knowledge of computers and at least BASIC programming. But today, the microcomputer biz has doubled, tripled, fourpled, and fippled in just a little while and there are now many thousands in the market who do not necessarily possess the semiadvanced background of the former readership. Back when the *Altair* S-100 was king, and the "Great Woz" was taking his first byte out of the *Apple*, anybody who wanted in on these microcomputer widgets was, by definition, a genuine hacker. The market was self-defining to an extent, because only those who would become hackers dared (that's right, dared!) buy a computer kit (shudder ... the complexity of it all). But today, with prices down and mass marketing technique up, everybody can own a computer and do more with it than we late-sixties engineering students could do with three-and-a-quarter tons of junk! Being a semi-irreverent sort, I aim to tear off the robes of the modern sacerdotal priests of "HIGH TECHNOLOGY" so that one and all can enjoy and benefit from the marvelous little microcomputer. Toward this end. Chapter One of this book contains several features. One is a discussion of microcomputers as opposed to minicomputers, "mainframe" computers, and so forth. Those descriptions will make you conversant with the language of the technology even if you are scared to death to "hit RETURN" on your new toy! We will also look at some applications categories for microcomputers, and some of the more popular 6502-based machines.

One feature most asked for by readers of my other books is a discussion on the basic operation of any programmable digital computer. It seems that most authors (myself included) have, in the past, launched right into the discussion of chips and bytes and other such wonders without ever stopping to ask the poor confused beginner whether or not he or she actually knows how a programmable digital computer functions. What does go on inside that box? Toward that end, I have created a hypothetical computer that is not based on any microprocessor chip (that way I can use it in several more books!), but it is based on the generic form of the computer. I call this device the Mythical Analytical Device, or MAD (which acronym, by the way, accurately describes the typical user after the umpteenth "bomb" and the apparent state of us elderly hackers—as seen by computer newcomers).

The book also contains a lot of material on interfacing to the 6502 microprocessor, and to computers that are based on the 6502. I have also covered some of this material in my book *Elements of Microcomputer Interfacing*, also a Reston book. The material in that book is more general in nature, but goes a lot deeper than was possible within the length/cost constraints placed on the present work.

The 1980 companion volume to this book is Z80 User's Manual. That book was rejected by two other publishers before Reston took a chance and published the work. That risk was apparently well taken, however, because the Z80 User's Manual turned out to be a popular best-seller and was even recommended in the Timex/Sinclair T/S-1000 User's Manual. The success of that book startled me (and at least one of the editors who rejected it), and I could never figure out why anyone would buy it. Most of the material given in that book, and in large sections of this book, is available elsewhere for free. So why, I wondered, would anyone pay me good money for the information that is in so many other sources? One reader of mine (who is also a friend and fellow hacker) gave me the answer: that book (and this one) sums up, explains, interprets, and collects into one volume instead of ten what everyone needs to know about their machines. Rather than a stack of books, you only need two: this book and the operating manual for your computer! (well, you could buy a few more of my books if you insist!)

Speaking of buying books. If you are just browsing right now, go ahead and buy the book (please don't shoplift it . . . that's naughty!), I need the money!

Joe Carr

# 1

# Introduction to Microprocessors and Microcomputers

One of the most frequent questions the microcomputer owner asks is, "What will it do?" This question is exasperating because it has too many answers. Indeed, what is the role of a microcomputer? For that matter, what is a microcomputer?

At one time, definitions were simpler. As a freshman engineering student, I was allowed to use an IBM<sup>®</sup> 1601-1620 machine; *that* was a computer! There was no doubt in anyone's mind about that machine's identity; it took up an entire room on the second floor of the engineering school's building. But, today, an engineering student can sit at a small desk with an Apple<sup>®</sup> II (complete with video CRT display, printer, and two disc drives) that has more computing power than that old 1601! In fact, many engineering students find the cost of the typical small system so affordable that they can own their own computer. Now the student can have more computing power in a dorm room than we had in the school of engineering. The cost of the modern microcomputer is less than one-tenth of what one of the lesser machines cost only a decade ago—not counting the fact that 1971 dollars were bigger than today's dollars.

Before attempting to define the role of the microcomputer, let's first try to define what the microcomputer is. Terminology in the computer field is often "O.B.E."—overcome by events. For example, consider the terms *microcomputer* and *minicomputer*. Some of us use these terms interchangeably, because modern single-chip computers (e.g., the Intel 8048) tend to make such usage seem reasonable. But, for our purposes, we require sharply focused meanings for these two

terms and others: minicomputer, microcomputer, single-chip computer, single-board computer, and mainframe computer.

## MICROPROCESSORS

The microprocessor is a large scale integration (LSI) integrated circuit (IC) that contains the central processing unit (CPU) of a programmable digital computer. The CPU of a computer contains the arithmetic logic unit (ALU) that performs the basic computational and logical operations of the computer. The CPU also houses the control logic section, which performs housekeeping functions, and may or may not have several registers for the temporary storage of data. All CPUs have at least one temporary storage register called the accumulator, or A-register. The principal attribute of a microprocessor is that it will execute instructions sequentially. These instructions are stored in coded binary form in an external memory.

# MICROCOMPUTERS

A microcomputer is a full-fledged programmable digital computer that it built around a microprocessor "chip," i.e., integrated circuit; the microprocessor acts as the CPU for the computer. In addition to the microprocessor chip, the microcomputer typically will have additional chips; the number may vary from two to hundreds depending upon the design and the application. These external chips may provide such functions as memory (both temporary and permanent), input/output (I/O), and other functions. The microcomputer may be as simple as a KIM-1, or as complex as a 30-board professional machine with all the electronic data processing "goodies."

# SINGLE-CHIP COMPUTERS

For several years we had no excuse for interchanging the terms *microprocessor* and *microcomputer*; a  $\mu$ P was an LSI chip and  $\mu$ C was a computing machine. But with the advent of the 8048 and similar devices, previously well-defined boundaries dissolved because these devices were both an LSI IC *and* a computer. A typical single-chip computer may have a CPU section, two types of internal memory (temporary and long-term permanent storage), and at least two I/O ports. Some machines are even more complex.

The single-chip computer does, however, require some external components before it can do work. By definition, the microcomputer

already has at least a minimum of components needed to perform a job.

# SINGLE-BOARD COMPUTERS

The single-board computer is a programmable digital computer, complete with input and output peripherals, on a single printed circuit board. Popular 6502-based examples are the KIM-1, SYM-1, and AIM<sup>®</sup>-65 machines. The single-board computer might have either a microprocessor or a single-chip computer at its heart.

The peripherals on a single-board computer are usually of the most primitive kind (e.g., AIM-65), consisting of 7-segment LED numerical displays and hexadecimal keypads reminiscent of those on a handheld calculator or *Touch-Tone*<sup>TM</sup> telephone. The typical display is capable of displaying only hexadecimal numeral characters because of the form constraints of using 7-segment LED display devices. The Rockwell International AIM-65 uses a regular ASCII keyboard and a 20-character display made of  $5 \times 7$  dot matrix LEDs. In addition, the AIM-65 has a built-in 20-column dot matrix thermal printer that uses printing calculator paper.

Most single-board computers have at least one interface connector that allows either expansion of the computer or interfacing into a system or instrument design.

The manufacturers of SBCs, such as the KIM-1 and others, probably did not envision their wide application as a small-scale development system. These computers were primarily touted as trainers for use in teaching microcomputer technology. But for simple projects such computers also work well as a mini-development system! More than a few SBC trainers have been used to develop a microcomputerbased product, only to wind up being specified as a "component" in the production version. In still other cases, the commercially available SBC has been used as a component in prototype systems, and then, in the production version, a special SBC (lower cost) was either bought or built.

### MINICOMPUTERS

The minicomputer predates the microcomputer and was originally little more than a scaled-down version of larger data processing machines. The Digital Equipment Corporation (DEC<sup>®</sup>) PDP-8 and PDP- $11^{TM}$  machines are examples of "minis." The minicomputer will use a variety of small-scale (SSI), medium-scale (MSI), and large-scale integration (LSI) chips.

Minicomputers have traditionally been more powerful than microcomputers. They had, for example, longer length binary data words (12 to 32 bits instead of 4 or 8 bits found in micros), and operated at faster speeds (6 to 12 mHz instead of 1 to 3 mHz). But in this area, distinctions are fading. Digital Equipment Corporation, for example, offers the LSI-11 microcomputer that acts like a mini. Similarly, 16bit microcomputers are available, as are 6 mHz devices. It is sometimes difficult to draw the line when a microcomputer is in the same size cabinet as a minicomputer, and minicomputers can be bought in desktop configurations!

#### MAINFRAME COMPUTERS

The large computer that comes to mind when most people think of computers is the mainframe computer. These machines are the computers used in large-scale data processing departments. Microcomputerists who have an elitist mentality sometimes call mainframe computers "dinosaurs." But, unlike their reptilian namesakes, these dinosaurs show no signs of extinction and are, in fact, an evolving species. The IBM 370 is an example of a mainframe computer.

#### ADVANTAGES OF MICROCOMPUTERS

Microcomputers have certain advantages, as attested to by the fact that so many are sold! But what are these advantages?

The most obvious advantage of the microcomputer is reduced size; compared with dinosaurs, microcomputers are mere lizards! An 8 bit microcomputer with 64K bytes of memory can easily fit inside a table-top cabinet. For example, Apple® III (Figure 1-1) fits the complete computer (plus one optional disc drive) into the space inside a small table-top cabinet! Another company packs a computer with 16K of random access memory (RAM) inside a keyboard housing!

The LSI microcomputer chip is generally more complex than a discrete components circuit that does the same job. However, the interconnections between circuit elements are much shorter (micrometers instead of millimeters). Input capacitances are thereby made lower. The MOS technology used in most of these ICs produces very low current drain, hence the overall reduced heating. While a mini-computer may require a pair of 100 cfm blowers to keep the temperature within specifications, a microcomputer may be able to use a single 40 cfm muffin fan or no fan at all!

Figure 1-1. Apple III microcomputer

Another advantage of the LSI circuit is reduced component count, which reduces size. In addition it also affects reliability. If the LSI IC is just as reliable as any other IC (and so it seems), then the overall reliability of the circuit is increased dramatically. Even if the chip reliability is lower than in lesser ICs, we would still achieve superior reliability due to fewer interconnections on the printed circuit board, especially if IC sockets are used. Some of the most invidious troubleshooting problems result from defective IC sockets!

### **MICROCOMPUTER INTERFACING**

The design of any device or system in which a microcomputer or microprocessor is used is the art of *defining* the operation of the system or device, *selecting the components* for the device or system, *matching*

and *integrating* those components (if necessary), and *constructing* the device or system. These activities are known collectively as *interfacing*.

But let's get down to a more basic level. Most readers of this book are technical people with some knowledge of electronics and computer technology. For most readers, therefore, interfacing consists of selecting and matching components, and then connecting them into a circuit that does a specific job. These matters are addressed in later chapters.

#### MICROCOMPUTERS IN INSTRUMENT AND SYSTEM DESIGN

In the past designers had to use analog electronic circuits, electromechanical relays (which sometimes leads to a maintenance nightmare), and other devices to design instruments, process controllers, etc. These circuit techniques had their limitations and produced some irritating results: factors like thermal drift loomed large in some of these circuits. In addition, the design was cast in cement once the final circuit was worked out. Frequently, relatively subtle changes in a specification or requirement produced astonishing changes in the configuration of the instrument; analog circuits are not easily adaptable to new situations in many cases. But with the advent of the microcomputer, we gain the advantage of flexibility and solve some of the more vexing problems encountered in analog circuit design. The memory of the computer tells it what to do, and that can be changed relatively easily. We can, for example, store program code in a read only memory. or ROM, which is an integrated circuit memory. If a change is needed, then the software can be modified and a new ROM installed. If the microcomputer was configured well, then it is possible to redesign only certain interface cards (or none at all) to make a new system configuration! For example, an engineer built an anode heat computer for medical X-ray machines. A microprocessor would compute the heating of the anode as the X-ray tube operated, and would sound a warning if the limit of safety was exceeded-thus saving the hospital the cost of a \$10,000 X-ray tube! But different X-ray machines require different interfacing techniques, a problem that previously had meant a new circuit design for each machine. But by intelligent engineering, the anode heat computer could be built with a single interface card that married the "universal" portion of the instrument with each brand of X-ray machine. Thus, the company could configure the instrument uniquely for all customers at a minimal cost.

Another instrument that demonstrates the universality of the microcomputer is a certain cardiac output computer. This medical device is used by intensive care physicians to determine the blood pumping capability of the heart in liters per minute. A "bolus" of iced or room tempterature saline solution is injected into the patient at the "input" end of the right side of the heart (the heart contains two pumps, right side and left side, with the right-side output feeding the left-side input via the lungs). The temperature at the output end of the right side is monitored, and the time integral of temperature determined. This integral, together with some constants, is massaged by the computer to calculate the cardiac output.

These machines come in two versions, research and clinical. The researcher will take time to enter certain constants that depend upon the catheter used to inject saline, temperature, and other factors. and will be more vigorous in following the correct procedure. But in the clinical setting, technique suffers as the patient is cared for, resulting in "machine error," which is actually operator error. To combat this problem, the manufacturer offers two machines. One is a research instrument and is equipped with front panel controls that allow the operator to select a wide range of options. The other, a clinical model, allows no options to the operator and is a "plug and chug" model. The interesting thing about these instruments is that they are *identical* on the inside! The only difference is the front panel and the position of an on-board switch! The manufacturer's program initially interrogates a switch to see if it is open or closed. If it is open, then it "reads" the keyboard to obtain the constants. On the other hand, if it is closed, then the program branches to a subprogram that assumes certain predetermined constants that are loaded on the buyer's prescription when the instrument is delivered. The cost savings of using a single design for both instruments are substantial!

# 6502-BASED MACHINES

We are going to examine some of the different 6502-based machines found on the market. Inclusion in here does not connote endorsement of the product, nor that another manufacturer's product isn't as good.

# SYNERTEK SYM-1

Several years ago, the original manufacturer of the 6502 microprocessor, MOS Technology, Inc., produced a small, single-board computer that contained a hexadecimal keyboard and LED readouts. Originally conceived as a trainer, the KIM-1 microcomputer became something of a standard among single-board computers, and its "bus" is now sometimes referred to as the "KIM-bus." The KIM inspired a large

collection of magazine articles, books, and accessory products. For many advanced computer scientists, the little KIM-1 was their first introduction into the world of microcomputer technology.

Although the SYM-1 microcomputer shown in Figure 1-2 is based on the original KIM-1 machine of another manufacturer, it extended the machine's capabilities and provides more features than the original design. Synertek Systems Corporation of Santa Clara, CA is the manufacturer of the SYM-1 machine.

Although the principal application for the SYM-1 is to train engineers and students in microcomputer interfacing and programming technology, applications have expanded into engineering laboratory work, prototyping of devices based on the 6502 microprocessor, instrumentation, and conducting both experimenting and testing in engineering and scientific laboratories. As the SYM-1 uses the same identical hardware interface bus as the earlier KIM-1 device, it may be "plugged into" applications previously reserved to the KIM-1 machine.

The SYM-1 device has a 4K byte on-board monitor program, 1K byte of on-board RAM (expandable to 4K bytes), and provision for up to 28K bytes of on-board ROM or PROM. The applications port has 15 bidirectional, TTL-compatible I/O lines, which, again, is expandable. The machine also offers data storage and program storage on

Figure 1-2. SYM-1 microcomputer

Figure 1-3. Ohio Scientific Superboard II

audio cassettes (an ordinary cassette tape player that has both "MIC" and "EAR" jacks can be used), and will accommodate a full duplex teletypewriter (TTY) 20 milliampere loop. This last feature makes the SYM-1 compatible, not just with TTY machines, but also with a wide variety of hard-copy printers now on the market. The machine includes one other I/O port, the common RS-232 serial interface port. The RS-232 port makes the SYM-1 compatible with a variety of video terminals and other peripherals. An on-board video terminal capability allows you to use either a TV monitor or, if an R.F. modulator is provided, a home TV receiver to receive output data (32 character line of video).

### **OHIO SCIENTIFIC SUPERBOARD II**

The microcomputer in Figure 1-3 solves some of the problems inherent in other single-board designs such as inconvenient keyboard format. This machine also uses the same microprocessor (6502) as the KIM-1 and SYM-1 machines, although it does not use the KIM-1 bus. Pro-

gramming and data entry are through a full ASCII keyboard like those found on video CRT terminals and larger computers.

The Superboard II can interface with TTY, CRT video terminals, and other peripherals. It is probably one of the simplest of the socalled "advanced" single-board computers and offers much that the lesser machines cannot, for example, more memory and programming in BASIC.

#### APPLE II AND III

The Apple II and its later cousin, the Apple III, shown in Figure 1-1, have become the byword in personal computers, partially because these computers make available a "full-service" microcomputer in a small package. A system that includes 48K bytes of memory, color TV graphics, color TV monitor, a teletypewriter, and two 5.25 inch disc drives can take up little more space than a table top.

The Apple II comes with a plug-in BASIC, with a more extensive version of BASIC available as an option. It also has an assembly language and built-in disassembler capability. The ordinary Apple II is available with an audio cassette interface, although for any serious work it is recommended that at least one disc be acquired.

Also built into the Apple II is a video display circuit that will drive an ordinary television monitor. The regular video format is 40 characters per line, with a total of 24 lines on the CRT screen at any one time. An interesting feature of the Apple II video monitor is that either regular (white characters on black background) or inverse (black characters on white background) modes can be used, and some of the characters can be programmed to flash on and off. The color graphics video display is capable of 15 different colors on a normal color video monitor.

A high-resolution video display provides  $280h \times 192v$  capability, allowing the programmer to draw graphs and other displays on the CRT screen.

#### MICROPROCESSOR FUNDAMENTALS

The microprocessor chip literally revolutionized the electronics industry. Although initially thought of as either a small logic controller or as a data processing machine (depending upon your perspective and the first chip you saw), the microprocessor blossomed in less than a decade into a major force with hundreds of applications. What is a microprocessor? How does it relate to a microcomputer? We will explore these questions here, and hopefully present a good grounding in computer technology basics. But first, we will study computers in general by describing a "typical" programmable digital computer in block diagram form. In chapters to follow we will study the 6502 device.

# Mythical Analytical Device (MAD)

Rather than mold our discussion around any one manufacturer's product, let's make up one that is general enough to cover a large number of actual devices. Our "computer" will be nicknamed the Mythical Analytical Device, or MAD, because the acronym MAD adequately describes both the emotional state of programmers (whose frustrations mount geometrically with each passing "bomb-out") and the mental health of computer sciences "freaks" (who are often seen wandering aimlessly through university corridors muttering the arcane glossolalian prayers of their modern religion, "Hail, microprocessor, from whom all bits and bytes emanate...").

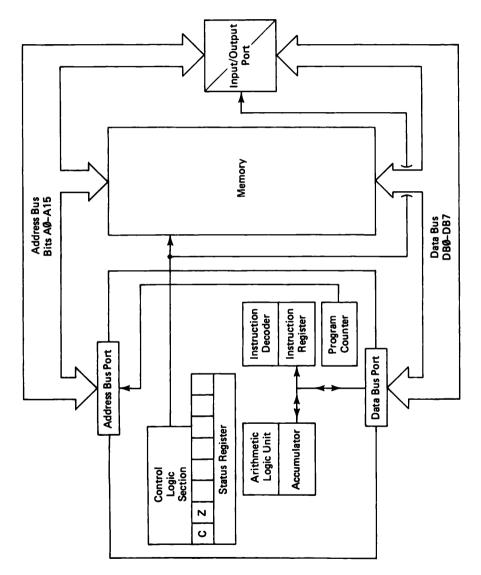

Figure 1-4 shows the block diagram of MAD. Like any programable digital computer, MAD has three main parts: *central processing unit* (CPU), *memory*, and *input/output* (I/O). There are certainly other functions in some machines, but many are either special applications of these main groups or are too unique to be described in a general machine.

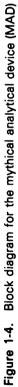

The central processing unit controls the operation of the entire computer. *Memory* can be viewed as an array of "cubbyholes," such as those used by postal workers (Figure 1-5) to sort mail. Each cubbyhole represents a specific address on the letter carrier's route. An address in the array can be uniquely specified (identifying only one location) by designating the row and column in which the cubbyhole is found. If we want to specify the memory location (i.e., cubbyhole) at row 3 and column 2, then we could create a row X column "address number" which, in this example, would be 32.

Each cubbyhole represents a unique location in which to store mail. In the computer, the memory location stores a binary word of information. In an 8-bit computer, each location will store a single 8bit binary word. The different types of memory devices are discussed in another chapter.

The three lines of communication between the memory and the CPU are address bus, data bus, and control logic signals. These avenues of communication control the interaction between memory and I/O

Figure 1-5. "Memory"

on the one hand, and the CPU on the other. Therefore they also control the functioning of the entire computer.

The address bus (bits AØ through A15 in Figure 1-4) communicates to the memory bank the address of the exact memory location being called by the CPU, regardless of whether a read or write operation is taking place. The address bus consists of parallel data lines, one for each bit of the binary word that is used to specify the address location. In most 8-bit microcomputers, for example, the address bus consists of 16 bits. A 16-bit address bus can uniquely specify  $2^{16}$ , or 65,536,different locations. This size is called "64K" not "65K" as one might expect. It seems that "k" represents the metric prefix *kilo*, which denotes 1,000. Since  $2^{10}$  is 1,024, however, computer people long ago decided that kilo would be 1,024, not 1,000. The "big k" (1,024) is represented with an uppercase K rather than k, which is used for real kilo.

The size of memory which can be addressed doubles for every bit added to the length of the address bus. Hence, adding one bit to our 16-bit address bus creates a 17-bit address bus which can designate up to 128K locations. Some 8-bit machines which have 16-bit address buses can be made to look like bigger machines by certain tactics that make a longer pseudo-address bus. In those machines, several 64K memory banks are used to simulate continuously addressable 128K, 256K, or 512K memories.

The data bus is the communications channel over which data travels between the main register (called the accumulator or A-register) in the CPU and the memory. The data bus also carries data to and

from the various input and/or output ports. If the CPU wants to "read" the data stored in a particular memory location, then that data is passed from the memory location over the data bus to the accumulator register in the CPU. Memory write operations are exactly the opposite direction, but otherwise the same.

The size of the data bus is usually cited as the "size" of the computer. Therefore, an 8-bit microprocessor/microcomputer is one that has an 8-bit data bus; a 16-bit microcomputer will have a 16-bit data bus. Do not be confused by salesmen such as the bozo who told me his 6502-based machine (8-bit data bus) was "in reality" a 16-bit machine because it had a 16-bit address bus!

The last memory signal is the control logic or timing signal. These are one or more binary logic signals that tell memory if it is being addressed, and whether the request is a read or write operation. The details of control logic signals differ between different microprocessor chips, so only those of the 6502 will be discussed in this book (for Z80 signals see Z80 User's Manual, by J. J. Carr, Reston Publishing Co.).

The input/output (I/O) section is the means by which the CPU communicates with the outside world. An input port will bring data in from the outside world and then pass it over the data bus to the CPU where it is stored in the accumulator. An output port reverses that data flow direction.

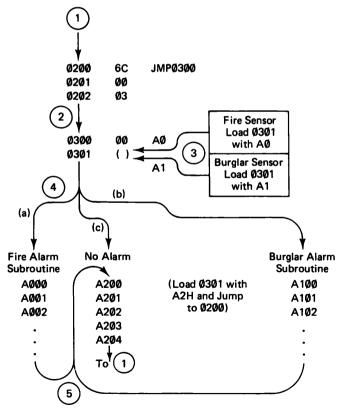

In some machines, separate I/O instructions are distinct from memory instructions. The Z80 is one such machine. The Z80 will pass the port address over the lower 8 bits of the 16-bit address bus (8-bit I/O address used in the Z80 can uniquely address up to 256 different ports). In other machines, such as the 6502, there are no distinct I/O instructions. In those machines, the I/O components are treated as memory locations; this technique is called *memory-mapping* or *memory-mapped I/O*. Input and output operations then become memoryread and memory-write operations, respectively.

#### **Central Processing Unit (CPU)**

The CPU is literally the heart and brains of any programmable digital computer, including MAD. Although there are some different "whistles and bells" features in certain machines, all will have the features shown in our MAD computer (Figure 1-4). The principal subsections of the CPU include (at least) the following: accumulator or A-register, arithmetic logic unit (ALU), program counter (PC), instruction register, status register, and control logic section.

The accumulator is the main register in the CPU, and will have the same bit length as the data bus. All instructions executed by the CPU involve data in the accumulator, unless otherwise specified in the description of that instruction. Therefore, an ADD instruction causes an arithmetic addition of the data cited by the instruction to the contents of the accumulator.

Although there are often other registers in the CPU, the accumulator is the main register. The main purpose of the accumulator is the temporary storage of data operated on by the instruction being executed. Data transfers to and from the accumulator are nondestructive. In other words, data "transfers" are not really transfers at all, but are, instead, "copying" operations. Suppose, for example, the hexadecimal number  $8F_{16}$  is stored in the accumulator when an instruction is encountered requiring that the contents of the accumulator be stored at memory location A008<sub>16</sub>. After the instruction is executed, we will find  $8F_{16}$  both in memory location A008 *and* in the accumulator. If we have the opposite operation (i.e., transfer contents of accumulator to location A008<sub>16</sub>), then we will see the same situation; after the transfer, the data will be in both locations. Since the accumulator contents change every time an instruction is executed, we will have to use such transfers to hold critical data some place in memory.

The arithmetic logic unit (ALU) contains the circuitry that performs the arithmetic operations of addition and (sometimes) subtraction, plus the logical operations of AND, OR, and XOR.

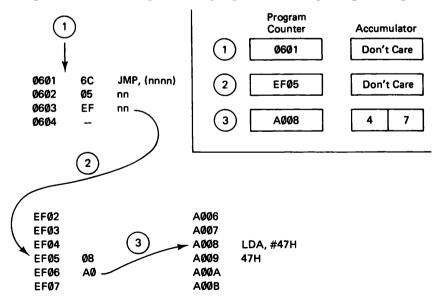

The program counter (PC) contains the address of the next instruction to be executed. The secret to the success of a programmable digital computer is its ability to fetch and execute instructions sequentially. Normally, the PC will increment appropriately (1, 2, 3, or4) while executing each instruction: 1 for 1-byte instructions, 2 for 2byte instructions, etc. For example, the instruction "LDA,n" is a 6502 instruction mnemonic that loads the accumulator with the number "n." In a program, we will find the code for LDA,n followed by "n."

| Location | Code               | Mnemonic |

|----------|--------------------|----------|

| 0100     |                    | LDA,n    |

| 0101     | "n"                | "n"      |

| 0102     | (next instruction) |          |

At the beginning of this operation, PC = 0100, but after execution it will be PC = 0102 because LDA,n is a 2-byte instruction.

There are other ways to modify the program counter. For example, executing any form of JUMP instruction modifies the contents of PC to contain the address of the "jumped to" location. Another way to modify the PC contents is to activate the reset line. The computer sees reset as a hard-wired JUMP to location 0000.

The instruction register is the temporary storage location for instruction codes stored in memory. When the instruction is fetched from memory by the CPU, it will reside in the instruction register until the next instruction is fetched.

The instruction decoder is a logic circuit that reads the instruction register contents and then carries out the intended operation.

The control logic section takes care of housekeeping chores within the CPU, and issues or responds to control signals from the outside world. These signals are not universally defined (which is one reason why we will consider two chips later in this chapter), but control such functions as memory requests, I/O requests, read/write signaling, interrupts, etc.

The status register, also sometimes called status flags, is used to indicate the status of the CPU at any given instant to the program, and sometimes to the outside world. Each bit of the status register represents a different function. Different microprocessor chips use slightly different status register architectures, but all will have a carry flag (C) to indicate when an instruction execution caused a "carry," and a zero flag (Z) that indicates when an arithmetic or logic instruction resulted in zero or nonzero in the accumulator (typically, Z = 1 when the result is zero).

We have now developed the CPU for our MAD computer. This discussion in general terms also describes a typical microprocessor chip; a microprocessor (as opposed to a single-chip computer) is essentially the CPU portion of a MAD.

#### **Operation of MAD**

A programmable digital computer such as MAD operates by sequentially fetching, decoding, and then executing instructions stored in memory. These instructions are stored in the form of binary numbers. Some early machines had two memories, one each for program instructions and data. The modern method, however, uses the same memory for both data and instructions.

How does the dumb computer know whether the binary number stored in any particular location is an instruction, data, or an alphanumeric character representation (e.g., ASCII or Baudot codes)? The answer to this important question is the key to the operation of MAD: The MAD operates in cycles.

A computer will have at least two cycles: instruction fetch and execution, and in some machines these cycles are subcycles. The details differ even though general scenarios are similar.

Instructions are stored in memory as binary numbers called *op*eration codes, or op-codes. During the instruction fetch cycle, an opcode will be retrieved from the memory location specified by the program counter and stuffed into the instruction register. The CPU assumes that the programmer was smart enough to arrange things such that an op-code will be stored at that location when the PC increments to that address.

During the first cycle, an instruction is fetched and stored in the instruction register. During the second cycle, the instruction decoder will read the IR, and then carry out the indicated operation. When these two cycles are completed, an instruction will have been fetched and executed, the program counter incremented to reflect the memory location that will contain the next instruction, and the CPU made ready for the next instruction. The CPU will then enter the next instruction fetch cycle and the process repeats itself.

This process continues over and over again as long as the MAD is working. Each step is synchronized by a train of clock pulses so that events remain rational.

This description illustrates what a computer can or cannot do. The CPU can shift data around, perform logical operations (e.g., AND, OR, XOR), add two N-bit numbers (sometimes subtract as well), all in accordance with a limited repertoire of binary word instructions. These chores are performed sequentially through a series of discrete steps. The secret to whether a problem is amenable to computer solution depends upon whether a plan of action (called an *algorithm*) can be written that will lead to a solution by a sequentially executed series of steps. Most practical instrumentation, control, or data processing chores can be so solved—a factor which accounts for the meteoric rise of the microprocessor. A field of endeavor that studies sequential solutions to practical (and some not so practical) problems is called *numerical methods*.

The MAD computer is merely a hypothetical construct used as a teaching aid. Let's examine a *real* microprocessor—the 6502.

# 2

# 6502 Architecture

The 6502 is one of the two most popular microprocessor chips on the market. Originated by MOS Technology, Inc., maker of the KIM-1 microcomputer, the 6502 is now available from more than 15 secondary sources. Among these secondary sources are Synertek and Rockwell International, who make the SYM-1 and AIM-65 microcomputers, respectively. The 6502 is widely used in applications which range from small Original Equipment Manufacturer (OEM) single-board computers and process controllers to elaborate data processing systems.

The 6502 is actually only one member (albeit the most popular member) of a family of microprocessor chips. Other members of the 65xx family include 6500/1, 6503, 6504, 6505, 6506, 6507, 6512, 6513, 6514, and 6515 devices. All members of the 65xx family (except 6502 and 6512) are housed in the 29-pin DIP IC package. The 6502 and 6512 are very similar to each other, except that 6512 has a data bus enable (DBE) terminal which the 6502 lacks. The 6500/1 is a single-chip computer that includes, in addition to the CPM circuitry, internal ROM, read/write memory, two timers, and four 8-bit input/output ports. The 6500/1 recognizes several timer and I/O instructions in addition to the regular 6502 instruction set.

The two basic philosophies behind third-generation microprocessor architecture are: (1) register-oriented, and (2) memory-oriented. The popular Zilog, Inc. Z80 (which grew out of Intel's 8080a) is an example of a register-oriented microprocessor. The companion volume to this book, Z80 User's Manual, is available from Reston Publishing Company. The 6502 grew out of the philosophy used to develop the 6800, and is an example of a memory-oriented machine.

The differences between the two philosophies are best seen in the structure of the I/O functions and the registers. The Z80 has numerous internal registers, while on the 6502, register functions are performed in external memory. Also, there are no Z80-like I/O instructions for 6502. All I/O ports are treated as memory locations. Such a system is often termed *memory-mapped I/O*.

The specific I/O instructions and internal registers of the Z-80type chip are advantageous in some applications, but for the most part confer only little advantage over 6502-style systems. In fact, since 6502 can perform certain logical and arithmetic operations directly on memory (without the need for intervening data transfers), some types of program will execute considerably faster on 6502 than on Z80. Both types of chip architecture have their optimum applications, as witnessed by the huge success of *both* Z80 and 6502 devices.

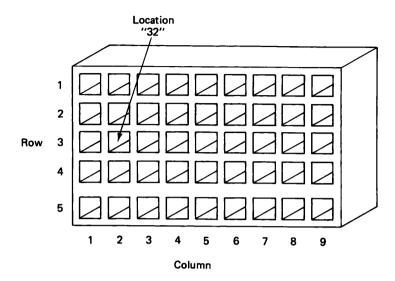

Figure 2-1 shows the block diagram for the 6502. Like most microprocessors of the era, the 6502 uses an 8-bit bidirectional data bus (DB0-BD7) and a 16-bit address bus (A0-A15); the address bus is unidirectional (output). Since there are 16 bits to the address bus, the

Figure 2-1. Block diagram for the 6502 microprocessor

$6502 \text{ can uniquely address } 2^{16}(65,536) \text{ different memory locations. Such a computer is a 65K machine.}$

### **6502 INTERNAL STRUCTURE**

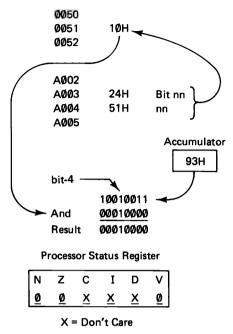

The 6502 is a complete central processing unit (CPU), which contains the following sections and registers: Arithmetic logic unit (ALU), accumulator (A-register), instruction register, instruction decoder/control logic section, interrupt control logic, processor status register, timing section, input data latch, stack pointer, index X register, index Y register, program counter (PCH and PCL), and data bus buffer. These are described here:

Arithmetic Logic Unit (ALU). The ALU is the internal logic that performs all arithmetic (ADC, SBC) and logical (AND, ORA, EOR) operations. The programmer does not have direct access to the ALU, except that the ALU is automatically implied by the instructions which affect the ALU.

The ALU is the heart of any CPU, and is one primary factor that distinguishes a computer or microprocessor from all other digital electronic circuits. This circuit performs the data manipulation including addition, subtraction, comparison, logical-AND, logical-OR, logical-XOR, left-shift, left-rotate, right-shift, right-rotate, bit set or reset, increment, decrement, and bit-test.

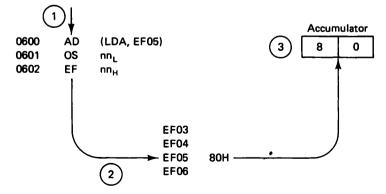

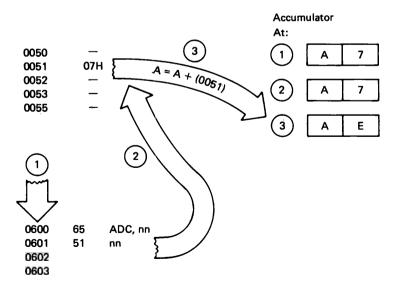

Accumulator. The accumulator, also called the A-register in some texts, is the main internal storage register in the 6502. Its function is to temporarily store data being operated on by the ALU. In the 6502, the accumulator is an 8-bit register that corresponds with the data bus on a bit-for-bit basis (i.e., bit 0 of the accumulator will travel to/from the CPU over DB0 of the data bus, bit 1 over DB1, etc.). Unless otherwise specified, all instructions executed by the 6502 use the accumulator. The addition-with-carry (ADC) instruction, for example, performs binary addition between an 8-bit data word fetched from memory and the contents of the accumulator.

Instruction Register (IR). The instruction register is the internal 6502 register where the instruction op-code is temporarily stored after it is fetched from memory.

Instruction Decoder/Control Logic. This section contains the logic circuits that will examine the contents of the instruction register, determine what operation is intended, and then permit the CPU to execute that instruction.

#### 22 6502 ARCHITECTURE

**Interrupt Control Logic (ICL).** An interrupt is a means by which an external device can gain control of the program. There are two active-LOW interrupt input lines on the 6502: NMI and IRO. The NMI input is a nonmaskable interrupt. When NMI is brought LOW, the processor will switch control to a predetermined subroutine after the current instruction is executed. The IRO is a maskable interrupt request input. Whether or not CPU recognizes the request is determined by the state (1 or 0) of an interrupt masking bit in the program status register. The programmer can cause IRO to be enabled by executing SEI and CLI bits. The subject of interrupts will be discussed in greater detail in Chapters 12 and 13. For now, we will simply state that the logic for handling the interrupt function is the business of the ICL section. The system reset (RES) line also is part of the ICL. The system reset is activated manually by the user, or automatically by a power-on reset circuit. The RES line on many computers is nothing more than a hardware "Jump to 0000" instruction. On the 6502, however, RES is a vectored jump, meaning that it will jump to a location specified by the contents of memory locations FFFCH and FFFDH.

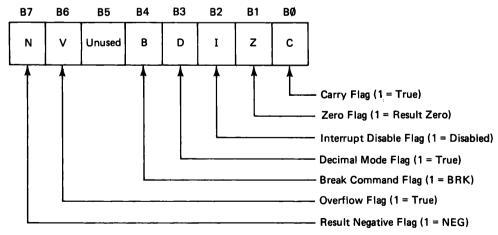

**Processor Status Register (PSR).** The PSR is an 8-bit/internal register that is used to indicate that status of certain processor functions. Each bit of the PSR is a "flag" and is independent of the other bits of the PSR. The flags tell the world the CPU status by being either set (1) or reset (0). The state of each flag is determined either by program control or by the result of the last operation. For example, the interrupt mask flag (I-flag) can be set or reset directly by SEI or SLI instructions, respectively. However, the Zero Flag (Z) is set or reset according to the results of operations on accumulator data. Arithmetic and logical instructions, for example, will leave Z = 0 if the result stored in the accumulator is non-zero, and Z = 1 if that result is zero. The six flags of the PSR are:

- N Negative result (bit 7 = 1)

- Z Zero result (all bits = 0)

- C Carry Flag (arithmetic produced a result, carry)

- I Interrupt mask flag

- D Decimal mode flag

- V Overflow flag

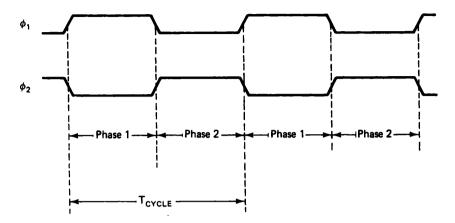

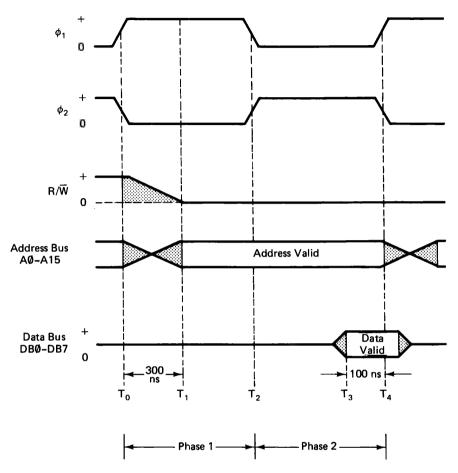

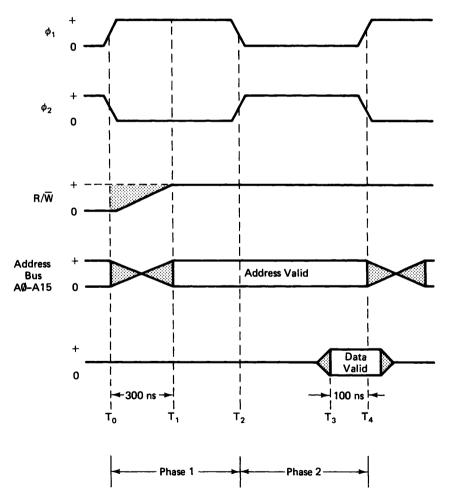

**Timing Section.** Computers operate synchronously with one or more system clocks. The 6502 uses three clock signals:  $\Phi_1$ ,  $\Phi_2$ , and  $\Phi_0$ . The  $\Phi_1$  and  $\Phi_2$  clock signals are internally generated by the timing section,

and are available as outputs (see Chapter 3). The  $\Phi_0$  clock is the master system clock, and is generated externally to the 6502.

**Stack Pointer (SP).** The SP register contains the low order byte within Page One (0100H to 01FFH) where the stack is located. The *push* (i.e., PHA and PHP) and *pull* (i.e., PLA and PLP) instructions operate the stack. The higher order byte of the stack start address is always 01H, with the low order byte (00H to FFH) being supplied by the SP.

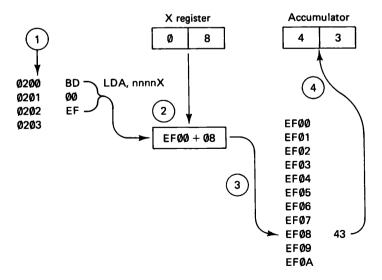

Index Registers X and Y. The X and Y index registers are 8-bit internal registers used in the indirect indexed addressing. In that form of addressing, the contents of either X or Y registers are added to a 2-byte address fetched from memory as a part of the instruction. The X and Y registers can also be operated on by certain instructions, such as load, store, increment, decrement, and exchange data.

**Program Counter (PCL and PCH).** The program counter is a pair of 8-bit registers which contain the address where the next instruction to be executed is stored in memory. When taken together, PCL and PCH form a 16-bit address. When the reset line on the 6502 is brought LOW, either by the power-on reset circuit or by a manual reset button, the program counter is loaded with the address bytes stored at locations FFFCH and FFFDH. In other microprocessors, the reset causes a jump to location 0000H.

The program counter is altered in several ways. Every time an instruction is executed, the program counter is incremented by the number of bytes required for that instruction: a 1-byte instruction increments PC by 1, a 2-byte instruction by 2, etc. For example, in Figure 2-2, the main program encounters an *add with carry* (ADC) instruction at location 0201H. This particular form of ADC uses a form of addressing in which the operand is stored at a location 0204H. Thus, the program counter increments directly from 0201H to 0204H as ADC is being executed.

| Address | Instruction        | Program Counter |  |

|---------|--------------------|-----------------|--|

| 0201    | ADC                | 0201            |  |

| 0202    | (Byte #1)          |                 |  |

| 0203    | (Byte #2)          | +               |  |

| 0204    | (Next Instruction) | 0204            |  |

| 0205    |                    |                 |  |

Figure 2-2. Operation of the program counter (an example)

#### 24 6502 ARCHITECTURE

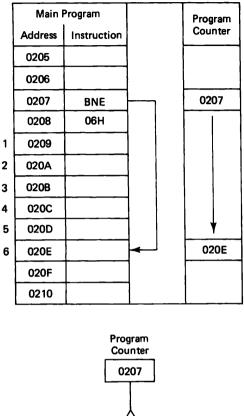

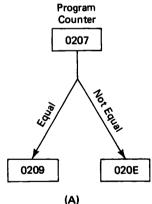

Figure 2-3. Operation of the program counter during the BNE (branch on not-equal to zero) instruction A) forward branch.

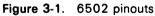

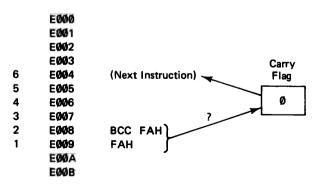

Another way to alter the contents of the program counter is to execute a *branch* instruction such as BNE, BEQ, BCC, and BCS. These instructions use relative addressing. This term means that the program counter will be modified by an amount denoted by the second byte of the instruction. Forward branches are determined by using a positive hexadecimal number, while backward branches are denoted by a two's-

#### 6502 Internal Structure 25

| Main    | Program     |          | Program |

|---------|-------------|----------|---------|

| Address | Instruction |          | Counter |

| 01FD    |             |          |         |

| 01FE    |             |          |         |

| 01FF    |             |          |         |

| 0200    |             |          |         |

| 0201    |             |          |         |

| 0202    |             |          |         |

| 0203    |             | ┝╾┐      |         |

| 0204    |             |          |         |

| 0205    |             |          |         |

| 0206    |             |          |         |

| 0207    | BNE         | <u>}</u> | 0207    |

| 0208    | FA          |          | •       |

| 0209    |             |          | 0203    |

Figure 2-3 (continued). B) backward branch

complement equivalent negative hexadecimal number. For example, consider the *branch on result not equal to zero* (BNE) instruction shown in Figures 2-3A and 2-3B.

The BNE instruction examines the Zero Flag (Z) in the Processor Status Register for Z = 0, which indicates that the result of a previous operation was *not* equal to zero. BNE will fall through to the next instruction in sequence (e.g., 0209H in Figure 2-3A) if the result was

zero (Z = 1). If the result was non-zero (Z = 0), then BNE forces a jump forward or backward a number of steps denoted by the second byte of the instruction. It does this neat trick by altering the program counter contents. Two situations are given in the figures; a forward branch is shown in Figure 2-3A, while a backward branch is shown in Figure 2-3B. Let's consider the forward branch first.

Figure 2-3 shows a forward branch BNE operation from location 0207H. The op-code for BNE is stored at 0207H and the operand 06H is a positive hexadecimal number, so the program will branch six steps *forward* when the branch condition (i.e., Z = 0 for BNE) is satisfied. Consider first the situation where the condition is not satisfied (Z = 1). When BNE is encountered, it reads Z to determine status (1 or 0). If Z = 1, then the condition is not satisfied, so the program "falls through" to the next instruction. Since BNE is a 2-byte instruction, the next location is 0207H +2, or 0209H. When the condition is not met, therefore, the program counter is incremented from 0207H to 0209H.

The alternate situation in Figure 2-3A is when the condition is satisfied (Z = 0). Since the second byte is 06H, the instruction BNE will cause a branch forward by six steps; the program counter is altered by +6 to 020EH. Notice that the six steps are counted from the *next* step following the BNE and its operand, i.e., 0209H is the base for the count, not 0207H.

The backward branch situation is shown in Figure 2-3B. The situation for condition not satisfied is exactly the same as the other case. The program counter will be advanced from 0207H to 0209H. For example, for a backward branch of six steps we would use the two's complement of -6, which is FAH, in the second byte. Counting from the address of the next instruction (0209H), six steps would bring us to 0209H; the program counter is altered to 0203H.

One final way to alter the program counter is to execute either a jump instruction or an interrupt. In both cases, the operation transfers control to some other memory location by altering the PC contents.

The 6502 program counter is divided into two 8-bit registers called PCL and PCH. The PCL register outputs the low byte of the 16-bit address, while PCH outputs the high byte of the address. PCL and PCH forms the 16-bit address.

#### **MEMORY ALLOCATION RESTRAINTS**

Memory space in microcomputers is usually divided into "pages" of 256 bytes each. Page zero is 0000H to 00FFH, page one from 0100H to 01FFH, page two from 0200H to 02FFH, etc. On the 6502, we are

constrained from using locations in page zero, page one, and page FFH.

**Page Zero.** Memory locations from 0000H to 00FFH are in page zero, and are used in two different addressing modes: *zero page* and *indirect*. In zero page addressing, the CPU assumes that the high order byte of the address is 00H, while the low order byte is the second byte of the instruction. In indirect addressing, the second byte of the instruction points to a location in page zero where the low order byte of the intended address is stored; the high order byte will be stored at the next higher memory location. Since there are 256 locations in page zero, we can store up to 128 pairs of address bytes.

**Page One.** The "stack" is a section of memory used by the processor for such chores as the temporary storage of program counter contents when the processor goes to a subroutine. In the 6502, the stack is in page one (from 0100H to 01FFH). Usage of either page zero or page one addresses should be done cautiously because of these pre-emptory uses.

**Page FFH.** The six highest bytes in page FFH are predesignated for certain vectors, arranged in three pairs. These vectors are the addresses where the computer goes on reset and on both types of interrupt. These locations are pre-allocated as shown in Figure 2-4.

| Memory Location | Use   | Comment                                                                                                                                                                                                                        |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FFFFH<br>FFFEH  | IRQ   | Interrupt request line (IRQ) low causes processor<br>to jump to the memory location specified in these<br>two bytes. The high order byte of the 16-bit address<br>is stored at FFFFH, while the low order byte is at<br>FFFEH. |

| FFFDH<br>FFFCH  | RESET | Reset low causes jump to address specified by the contents of these locations: FFDH contains the high order byte, FFCH contains the low order byte.                                                                            |

| FFFBH<br>FFFAH  | NMI   | Nonmaskable interrupt request. See IRQ above.<br>High order byte is stored at FFFBH, low order byte<br>at FFFAH.                                                                                                               |

Figure 2-4. Vector locations for IRQ, RESET, and NMI

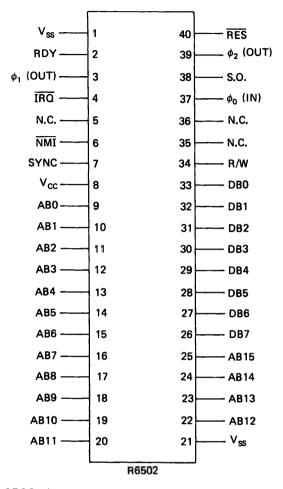

### 6502 Pinouts

The 6502 microprocessor is housed in a 40-pin Dual Inline Package (DIP). This package is shown in Figure 3-1 with the pinout designations that apply to the 6502. Note that most microprocessor chips use NMOS technology, so appropriate anti-static handling procedures must be followed lest the IC be zapped into never-never land.

#### 6502 Pinouts by Pin Number

| 1  | $\mathbf{V}_{ss}$ | 0 to $\pm 7$ volts    |

|----|-------------------|-----------------------|

| 2  | RDY               | Ready                 |

| 3  | $\Phi_1$ (out)    | Phase-1 clock output  |

| 4  | ĪRÒ               | Interrupt request     |

| 5  | N.Č.              | (no connection)       |

| 6  | <b>NMI</b>        | Nonmaskable interrupt |

| 7  | SYNC              | Synchronization       |

| 8  | $V_{cc}$          | +5 volts              |

| 9  | AB0               | Address bus bit 0     |

| 10 | AB1               | Address bus bit 1     |

| 11 | AB2               | Address bus bit 2     |

| 12 | AB3               | Address bus bit 3     |

| 13 | AB4               | Address bus bit 4     |

| 14 | AB5               | Address bus bit 5     |

| 15 | AB6               | Address bus bit 6     |

| 16 | AB7               | Address bus bit 7     |

| 17 | AB8               | Address bus bit 8     |

| 18 | AB9               | Address bus bit 9     |

| 19 | AB10              | Address bus bit 10    |

#### 6502 Pinouts by Pin Number (continued)

| 20 | AB11     | Address bus bit 11 |

|----|----------|--------------------|

| 21 | $V_{ss}$ | 0 to $+7$ volts    |

| 22 | AB12     | Address bus bit 12 |

| 23 | AB13     | Address bus bit 13 |

| 24 | AB14     | Address bus bit 14 |

| 25 | AB15     | Address bus bit 15 |

| 26 | DB7      | Data bus bit 7     |

| 27 | DB6      | Data bus bit 6     |

| 28 | DB5      | Data bus bit 5     |

| 29 | DB4      | Data bus bit 4     |

| 30 | DB3      | Data bus bit 3     |

#### 6502 Pinouts by Pin Number (continued)

| 31       | DB2                               | Data bus bit 2                |

|----------|-----------------------------------|-------------------------------|

| 32       | DB1                               | Data bus bit 1                |

| 33       | DB0                               | Data bus bit 0                |

| 34       | R/W                               | Read/Write                    |

| 35       | N.C.                              | (no connection)               |

| 36       | N.C.                              | (no connection)               |

| 37       | Φ <sub>0</sub> (IN)               | Phase-0 clock input           |

| 38       | S.O.                              | Set overflow flag             |

| 39<br>40 | $\frac{\Phi_2}{\text{RES}}$ (OUT) | Phase-2 clock output<br>RESET |

#### **6502 Pinout Descriptions**

| Designation | Pin     | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB0 – DB7   | (below) | Eight-bit bidirectional data bus.<br>LOW (logical-0) is $V_{ss}$ to $V_{ss}$ + 0.4<br>volt; input HIGH is $V_{ss}$ + 2.4 volts<br>to $V_{cc}$                                                                                                                                                                                                                                |

| DB0         | 33      | data bus bit 0                                                                                                                                                                                                                                                                                                                                                               |

| DB1         | 32      | data bus bit 1                                                                                                                                                                                                                                                                                                                                                               |

| DB2         | 31      | data bus bit 2                                                                                                                                                                                                                                                                                                                                                               |

| DB3         | 30      | data bus bit 3                                                                                                                                                                                                                                                                                                                                                               |

| DB4         | 29      | data bus bit 4                                                                                                                                                                                                                                                                                                                                                               |

| DB5         | 28      | data bus bit 5                                                                                                                                                                                                                                                                                                                                                               |

| DB6         | 27      | data bus bit 6                                                                                                                                                                                                                                                                                                                                                               |

| DB7         | 26      | data bus bit 7                                                                                                                                                                                                                                                                                                                                                               |

| AB0 — AB15  | (below) | Sixteen-bit address bus capable of ad-<br>dressing up to 65,536 (64K) unique<br>memory locations. These lines are<br>all outputs, and produce the same<br>HIGH and LOW voltage levels as<br>the data bus lines will respond to;<br>i.e., output-LOW (logical-0) is $V_{ss}$<br>to $V_{ss}$ +0.4 volt, while output-<br>HIGH (logical-1) is $V_{ss}$ +2.4 volt to<br>$V_{cc}$ |

| AB0         | 9       | address bus bit 0                                                                                                                                                                                                                                                                                                                                                            |

| AB1         | 10      | address bus bit 1                                                                                                                                                                                                                                                                                                                                                            |

| AB2         | 11      | address bus bit 2                                                                                                                                                                                                                                                                                                                                                            |

| AB3         | 12      | address bus bit 3                                                                                                                                                                                                                                                                                                                                                            |

| AB4         | 13      | address bus bit 4                                                                                                                                                                                                                                                                                                                                                            |

| AB5         | 14      | address bus bit 5                                                                                                                                                                                                                                                                                                                                                            |

| Designation         | Pin | Description                                                                   |

|---------------------|-----|-------------------------------------------------------------------------------|

| AB6                 | 15  | address bus bit 6                                                             |

| AB7                 | 16  | address bus bit 7                                                             |

| AB8                 | 17  | address bus bit 8                                                             |

| AB9                 | 18  | address bus bit 9                                                             |

| AB10                | 19  | address bus bit 10                                                            |

| AB11                | 20  | address bus bit 11                                                            |

| AB12                | 22  | address bus bit 12                                                            |

| AB13                | 23  | address bus bit 13                                                            |

| AB14                | 24  | address bus bit 14                                                            |

| AB15                | 25  | address bus bit 15                                                            |

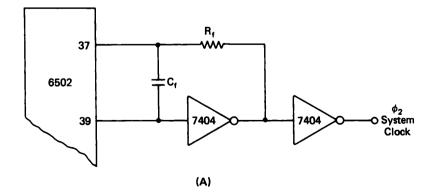

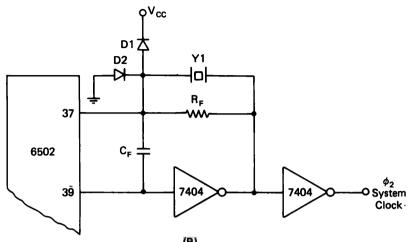

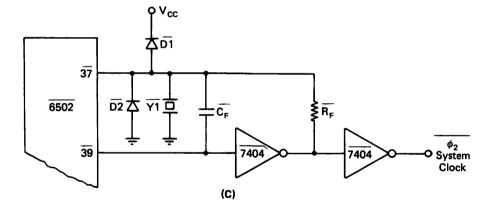

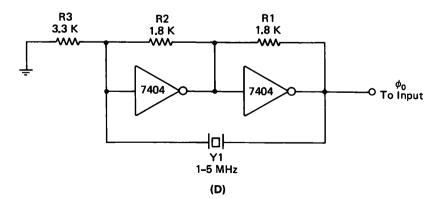

| $\mathbf{\Phi}_{0}$ | 37  | Phase-0 system clock input. Either                                            |

|                     |     | an RC timing network (not rec-                                                |

|                     |     | ommended) or an external crystal                                              |

|                     |     | clock oscillator will supply a 1 mHz                                          |

|                     |     | signal (2 mHz in some versions) to                                            |

|                     | _   | this pin                                                                      |

| $\mathbf{\Phi}_1$   | 3   | Phase-1 clock output; generated in-                                           |

|                     |     | ternally from $\Phi_0$ clock; comple-                                         |

|                     | ••• | ment of phase-2 clock                                                         |

| $\phi_2$            | 39  | Phase-2 clock output; generated in-                                           |

|                     |     | ternally from $\Phi_0$ clock; comple-                                         |

| R/W                 | 94  | ment of phase-1 clock                                                         |

| R/W                 | 34  | Indicates the <i>direction</i> of the data on the data bus; when this line is |

|                     |     | HIGH, the CPU is processing a                                                 |

|                     |     | read (input) operation; when this                                             |

|                     |     | line is LOW the CPU is processing                                             |

|                     |     | a write (output) operation                                                    |

| ĪRO                 | 4   | Interrupt request, this active-LOW                                            |

| щų                  | -   | input is used to interrupt the pro-                                           |

|                     |     | gram being executed so that a sub-                                            |

|                     |     | routine can be executed instead.                                              |

|                     |     | This interrupt input is maskable,                                             |

|                     |     | so it will cause a response only if                                           |

|                     |     | the internal interrupt flag of the                                            |

|                     |     | Processor Status Register is ena-                                             |

|                     |     | bled                                                                          |

| <b>NMI</b>          | 6   | Nonmaskable interrupt; similar to                                             |

|                     |     | the interrupt request line $(\overline{IRQ})$ ,                               |

|                     |     | except that this active-LOW input                                             |

|                     |     | is always active, and cannot be dis-                                          |

|                     |     |                                                                               |

#### 6502 Pinout Descriptions (continued)

| Designation     | Pin     | Description                                                                                                                                                                                                                                                                                     |

|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

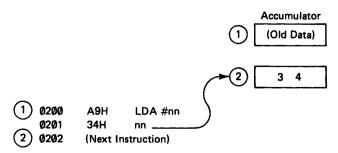

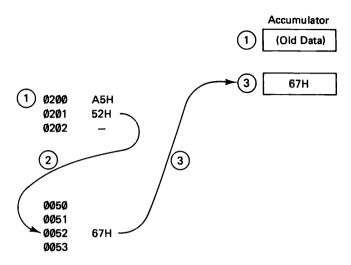

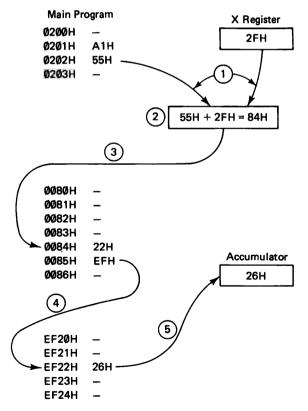

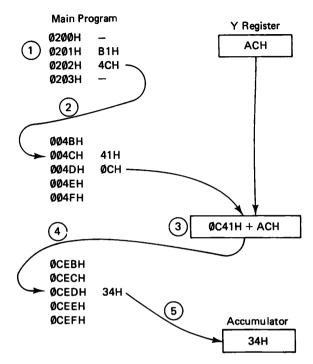

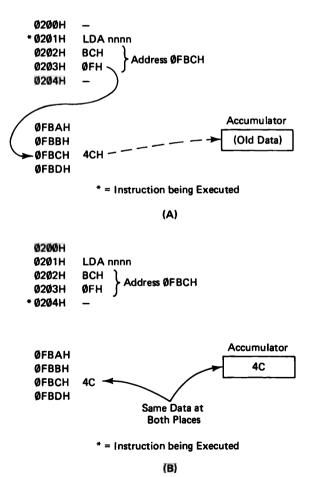

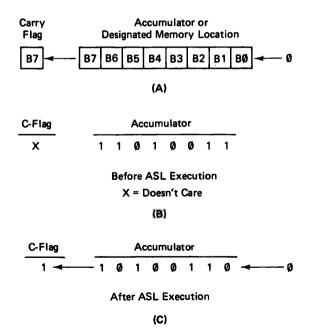

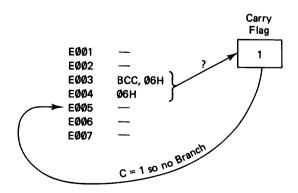

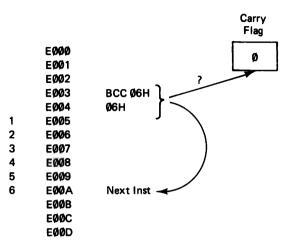

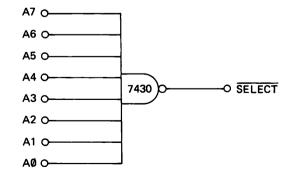

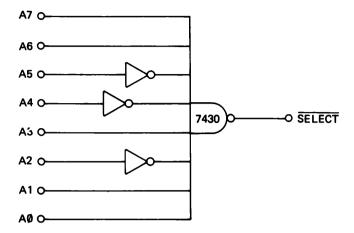

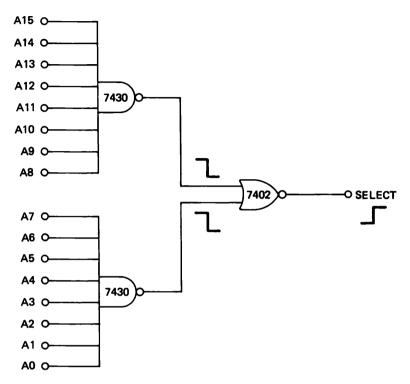

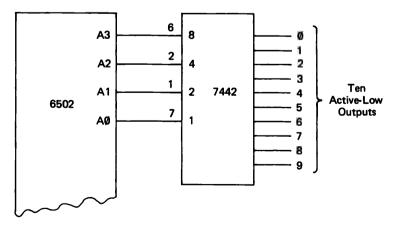

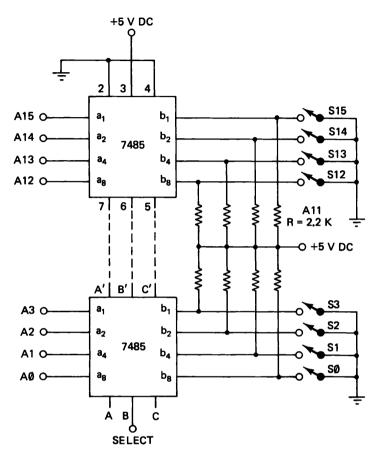

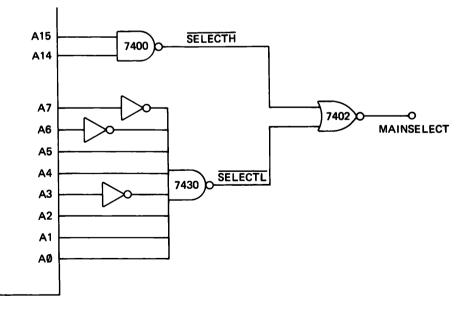

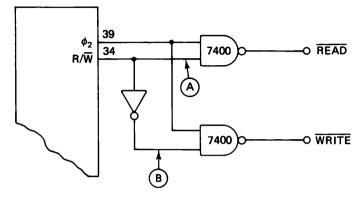

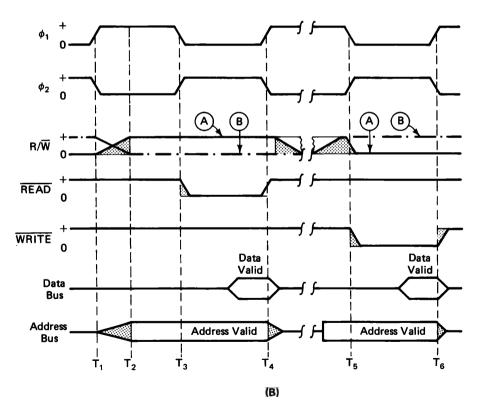

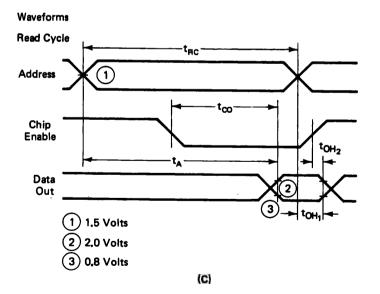

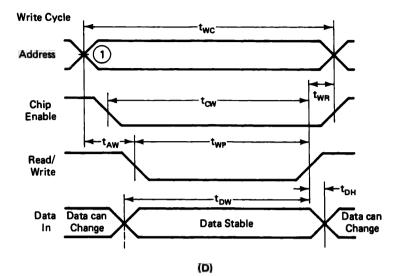

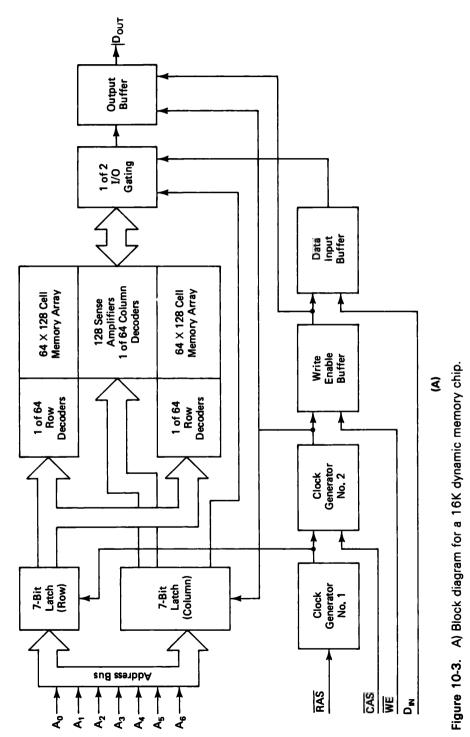

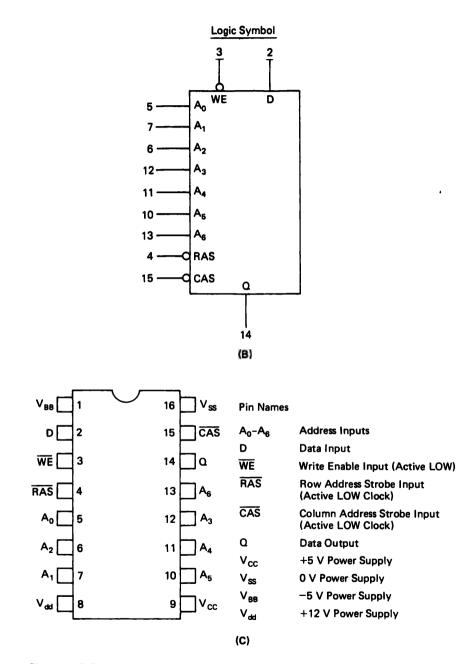

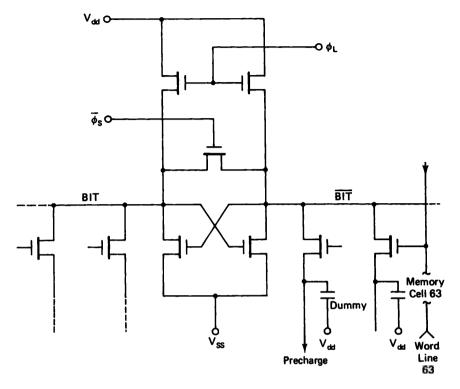

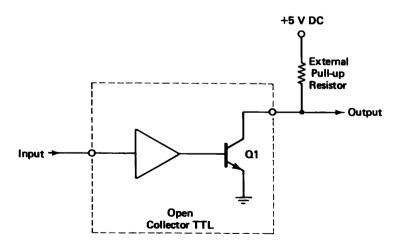

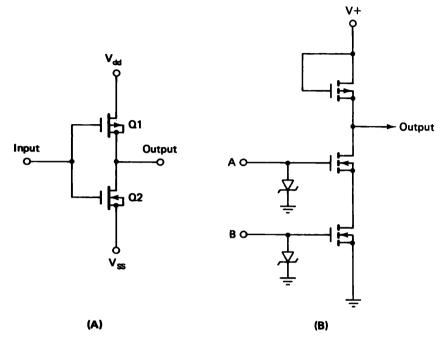

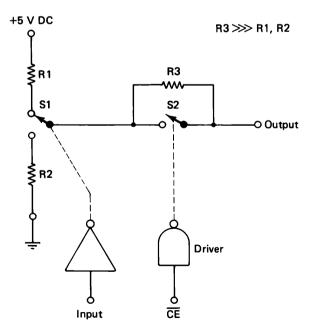

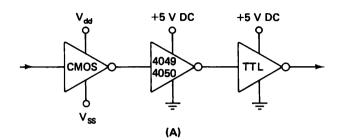

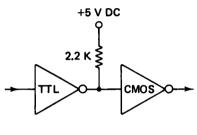

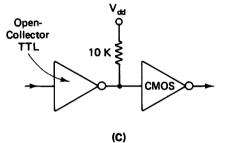

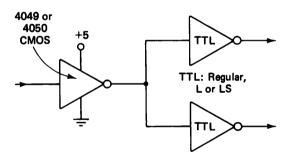

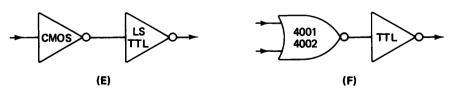

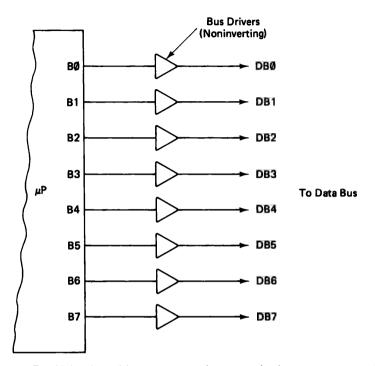

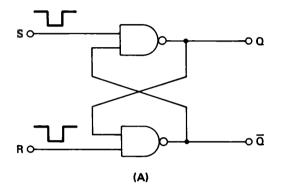

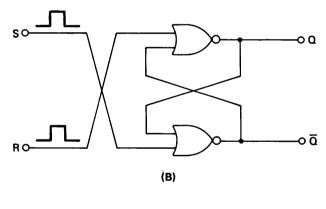

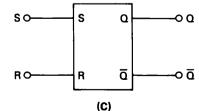

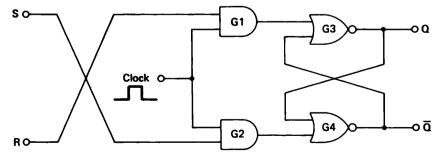

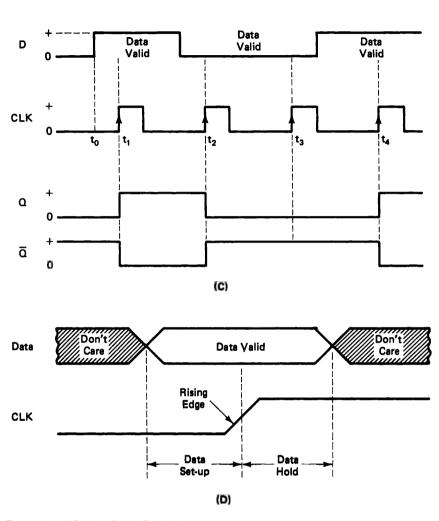

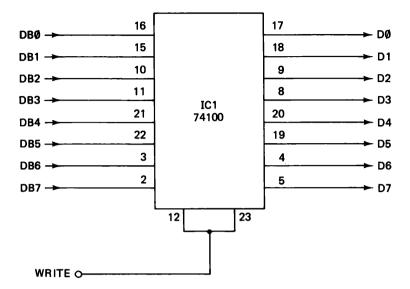

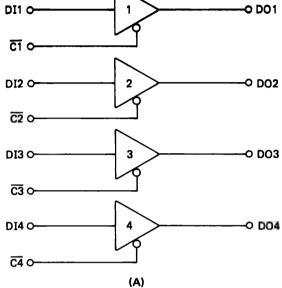

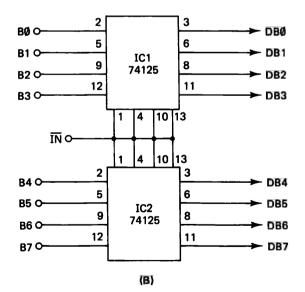

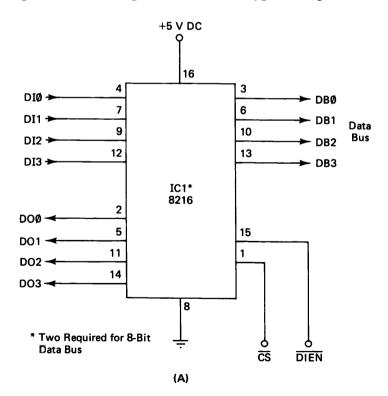

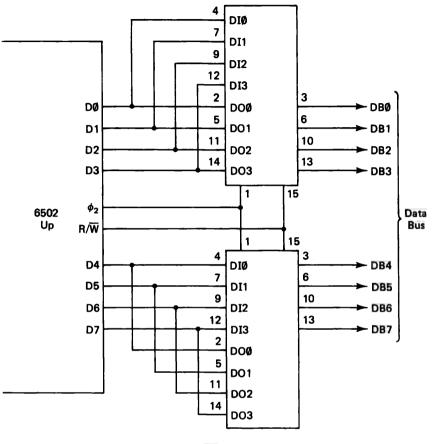

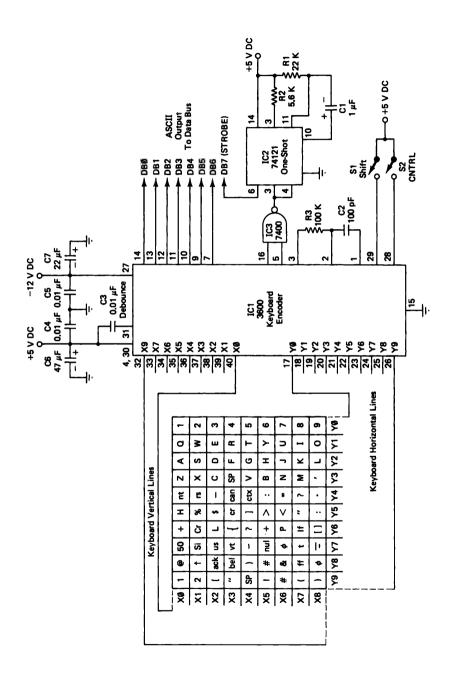

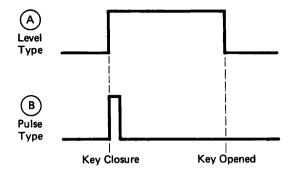

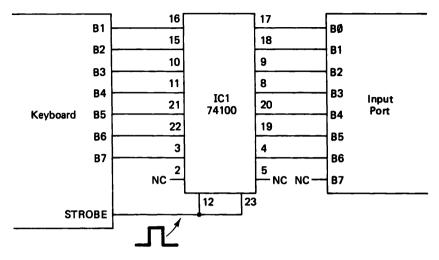

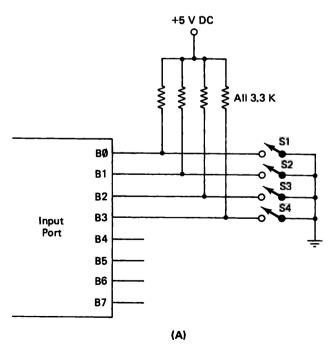

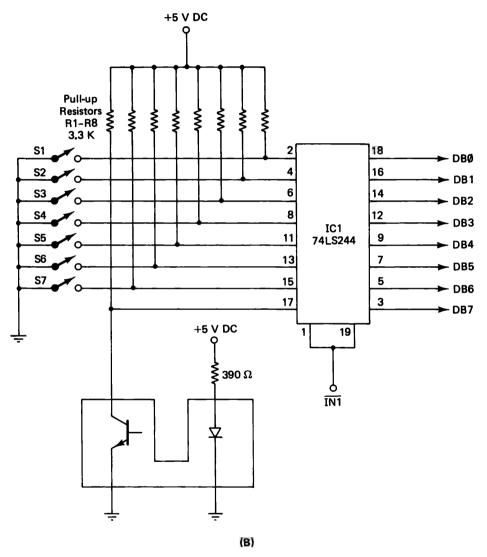

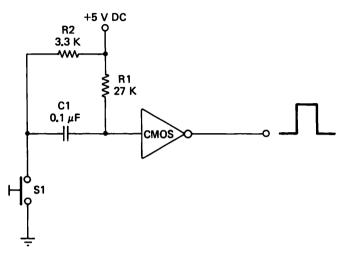

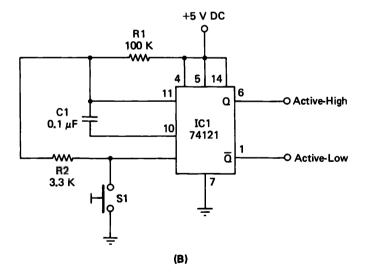

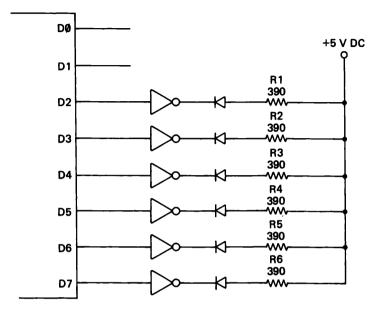

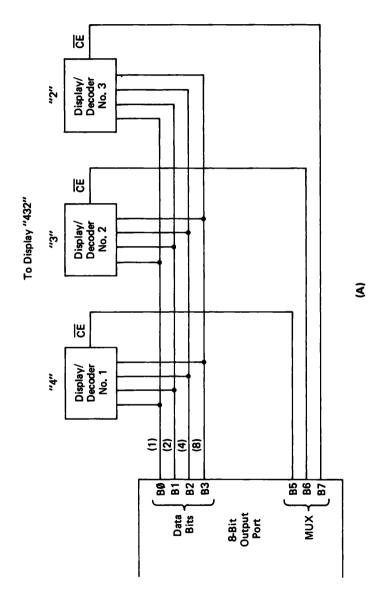

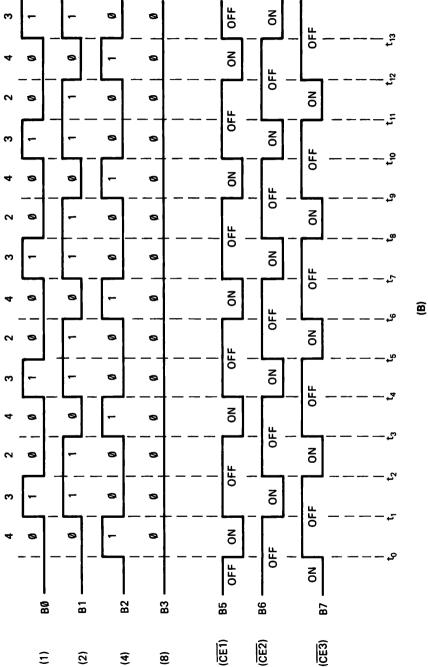

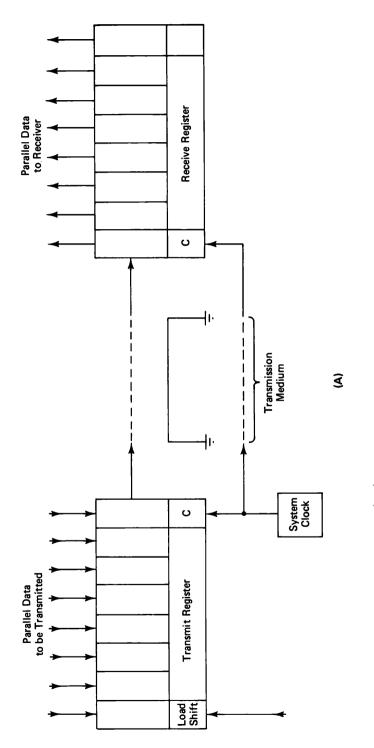

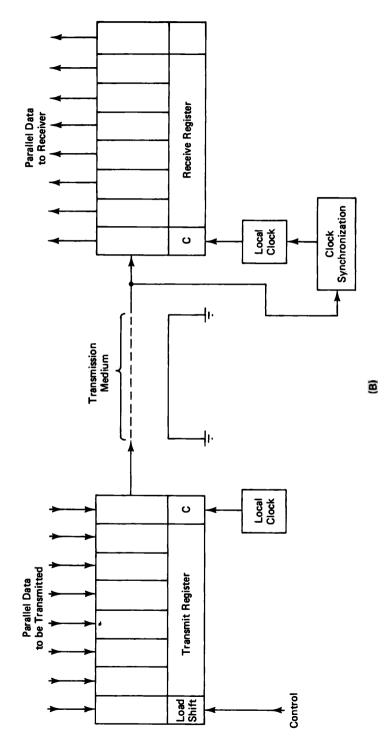

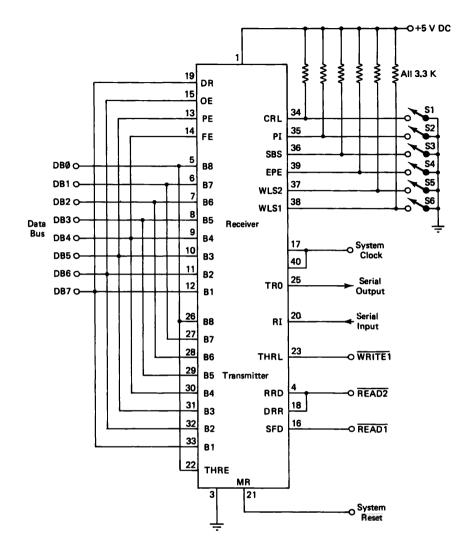

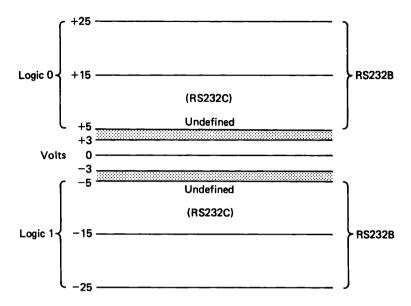

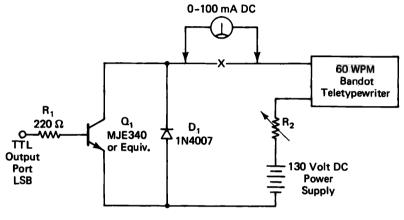

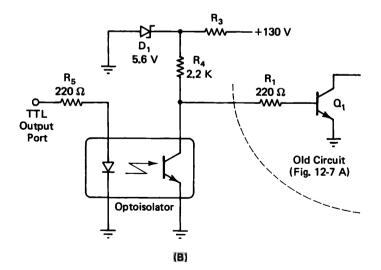

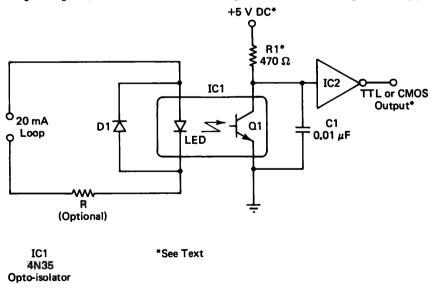

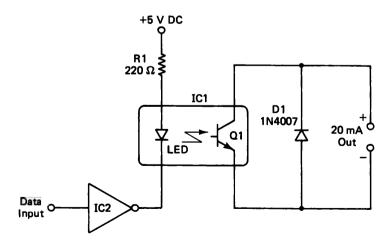

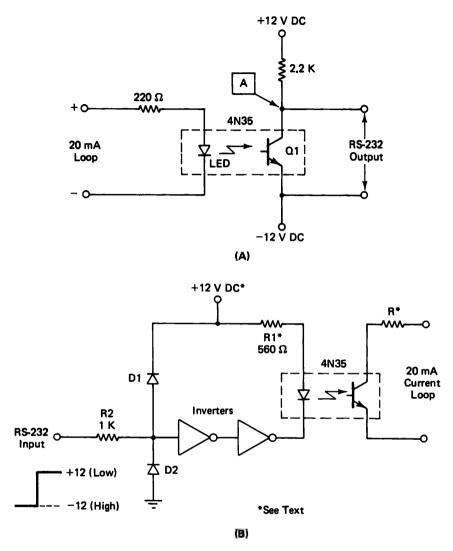

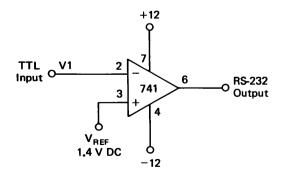

|                 |         | abled by the programmer. Pro-<br>gram will execute an interrupt<br>subroutine instead of the main<br>program as soon as the current in-<br>struction is finished execution                                                                                                                      |