# SILICON GATE MOS 2500 SERIES

#### DESCRIPTION

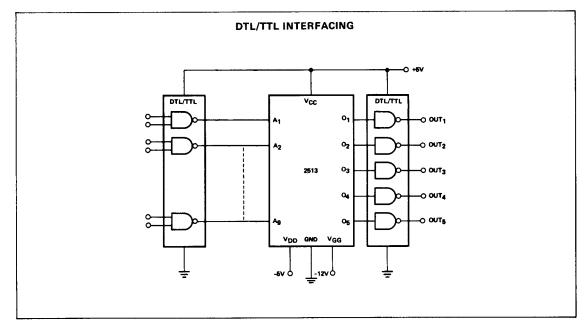

The Signetics 2513 is a high speed 2560-bit Static ROM organized as 64x8x5. A standard 7x5 dot matrix fits well in the 2513. The product uses +5V, -5V and -12V power supplies, TTL level interface signals and Tri-State Outputs for direct, low cost interfacing with TTL, DTL, CMOS and 2500 Series MOS.

#### **FEATURES**

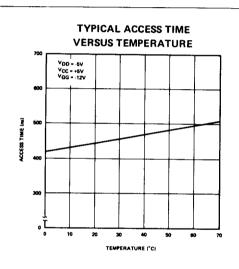

- 450 ns TYPICAL ACCESS TIME

- STATIC OPERATION

- TTL/DTL COMPATIBLE INPUTS

- +5. -5. ~12V POWER SUPPLIES

- TRI-STATE OUTPUT CONTROLLED BY CHIP ENABLE FOR BUSSING CAPABILITY

- 2513/CM2140 ASCII FONT STANDARD (7 X 5)

- 24-PIN DIP

- P-MOS SILICON GATE TECHNOLOGY

## **APPLICATIONS**

RASTER SCAN CRT DISPLAYS (ROW OUTPUT)

PRINTER CHARACTER GENERATOR

PANEL DISPLAYS AND BILLBOARDS

MICRO-PROGRAMMING

CODE CONVERSION

#### PROCESS TECHNOLOGY

The use of Signetics' P channel Silicon Gate Process allows the design and production of higher functional density and operating speed than other techniques.

#### SILICONE PACKAGING

Low cost silicone DIP packaging is implemented and reliability is assured by the use of Signetics unique silicon gate MOS process technology. Unlike the standard metal gate MOS process the silicon material over the gate oxide passivates the MOS transistors. In addition, Signetics proprietary surface passivation and silicone packaging techniques result in an MOS circuit with inherent high reliability, superior moisture resistance, and ionic contamination barriers.

#### BIPOLAR COMPATIBILITY

All inputs of the 2513 can be driven directly by standard TTL voltage levels. The data output buffers are capable of sinking a minimum of 1.6 mA, sufficient to drive one standard TTL load.

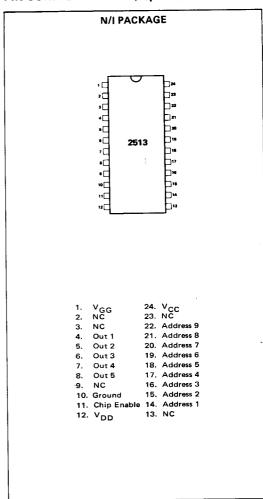

## PIN CONFIGURATION (Top View)

## PART IDENTIFICATION TABLE

| PART    | ORGANIZATION | PROGRAMMING |  |  |

|---------|--------------|-------------|--|--|

| 2513N/I |              |             |  |  |

| CM2140  | 64X8X5       | ASCII Font  |  |  |

| 2513N/I | 64X7X5       |             |  |  |

| CMXXXX  | 64X8X5       | Custom      |  |  |

N PACKAGE = 24 PIN SILICONE DIP

I PACKAGE = 24 PIN CERAMIC DIP

# **CHARACTER FORMAT**

# ROW ADDRESS A3 A2 A1 06 04 03 02 01 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 0

CHARACTER ADDRESS

As As A7 As

# MAXIMUM GUARANTEED RATINGS(1)

Operating Ambient Temperature

Storage Temperature

Package Power Dissipation(2) @TA 70°C

Input(3) and Supply Voltages

with respect to VCC

O°C to 70°C

-65°C to +150°C

730mW

+0.3 to -20V

# NOTES

of this specification is not implied.

2. For operating at elevated temperatures the device must be derated based on a +150°C maximum junction temperature and a thermal resistance of 110°C/W junction to ambient.

3. All inputs are protected against static charge.

4. Parameters are valid over operating temperature range unless specified.

5. All voltage measurements are referenced to ground.

Stresses above those listed under "Maximum Guaranteed Rating" may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or at any other condition above those indicated in the operational sections

changes and improvements.

7. Typical values are at +25°C and nominal supply voltages.

8. Guaranteed input levels are stated for worst case conditions including a ±5% variation in V<sub>CC</sub> and a temperature variation of 0°C to +70°C. Actual input requirements with respect

6. Manufacturer reserves the right to make design and process

to  $V_{CC}$  are  $V_{IH} = V_{CC}$  - 1.85V and  $V_{IL} = V_{CC}$  - 4.15V.

# DC CHARACTERISTICS

$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}; V_{CC} = +5\text{V } \pm 5\%; V_{DD} = -5\text{V } \pm 5\%; V_{GG} = -12\text{V } \pm 5\% \text{ unless otherwise noted.}$  (Notes 4, 5, 6, 7)

| 2 A IMBOL       | TEST                                 | MIN  | TYP | MAX  | UNIT | CONDITIONS                                                                             |

|-----------------|--------------------------------------|------|-----|------|------|----------------------------------------------------------------------------------------|

| ILI             | Input Load Current                   |      | 10  | 500  | nA   | V <sub>IN</sub> = -5.5V<br>T <sub>A</sub> = 25°C                                       |

| <sup>1</sup> LO | Output Leakage Current               |      | 10  | 1000 | nA   | V <sub>OUT</sub> = -5.5V<br>T <sub>A</sub> = 25°C<br>V <sub>CE</sub> = V <sub>CC</sub> |

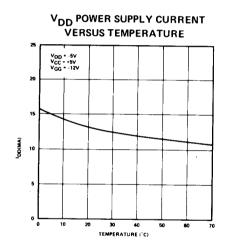

| IDD             | V <sub>DD</sub> Power Supply Current |      | 12  | 15   | mA   | Outputs Open                                                                           |

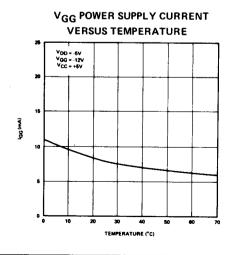

| <sup>1</sup> GG | V <sub>GG</sub> Power Supply Current |      | 10  | 15   | mA   | Outputs Open VCE = VCC                                                                 |

| V <sub>IL</sub> | Input Logic "0"                      |      |     | +0.6 | ٧    | Note 8                                                                                 |

| VIH             | Input Logic "1"                      | +3.4 |     | 5.3  | V    | Note 8                                                                                 |

## **AC CHARACTERISTICS**

$T_A = 0^{\circ}C$  to +70°C;  $V_{CC} = 5V \pm 5\%$ ;  $V_{DD} = -5V \pm 5\%$ ;  $V_{GG} = -12V \pm 5\%$ ; unless otherwise noted.

| SYMBOL                   | TEST                                               | MIN | TYP | MAX | UNIT | CONDITIONS                               |

|--------------------------|----------------------------------------------------|-----|-----|-----|------|------------------------------------------|

| V <sub>OL</sub>          | Output Logic "Zero"                                | -5  |     | 0.4 | V    | One TTL Load                             |

| $v_{OH}$                 | Output Logic "One"                                 | 3.0 | ļ   |     | V    | One TTL Load                             |

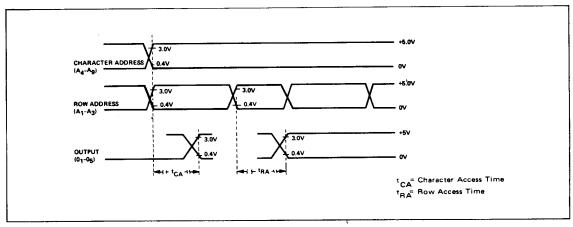

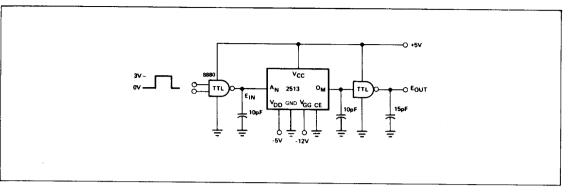

| <sup>t</sup> CA(CM2140). | Character Access Time                              |     | 500 | 600 | ns   | See AC Test Setup                        |

| <sup>t</sup> RA          | Row Access Time (A <sub>1</sub> - A <sub>3</sub> ) |     | 450 | 500 | ns   | See AC Test Setup                        |

| <sup>t</sup> CE          | Chip Enable to Output                              |     | 150 |     | ns   |                                          |

| CIN                      | Address Input Capacitance                          |     |     | 10  | pF   | $f = 1 MHz, V_{IH} = V_{CC}, 25mV p - p$ |

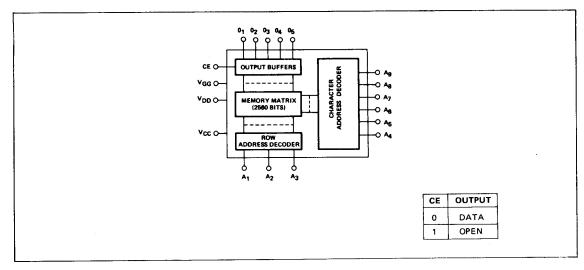

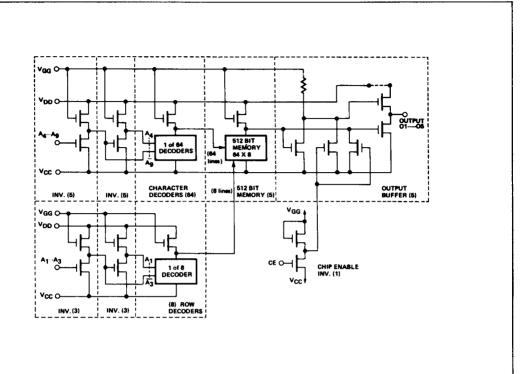

## **BLOCK DIAGRAM**

## **TIMING DIAGRAM**

## **AC TEST SETUP**

## TYPICAL CHARACTERISTIC CURVES

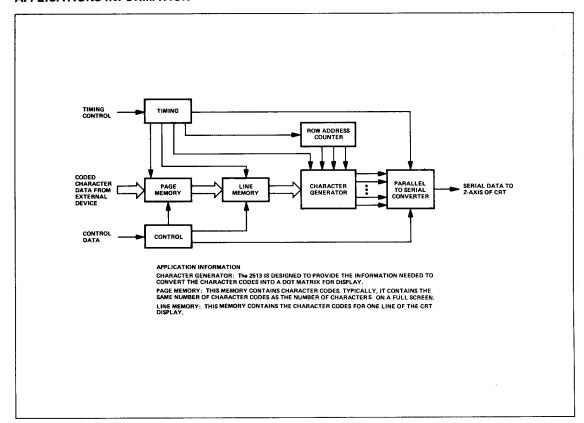

## APPLICATIONS INFORMATION

## CIRCUIT CROSS-SECTION

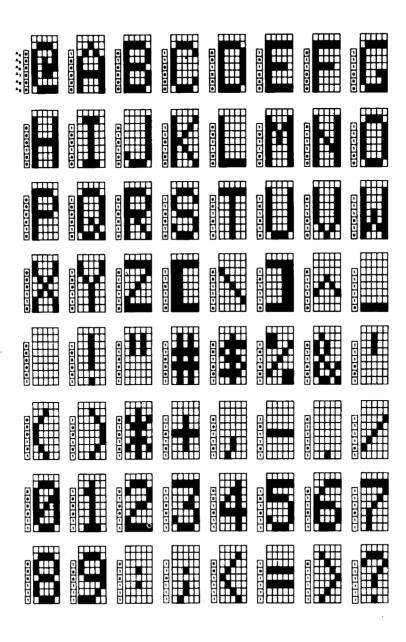

## ASCII CHARACTER FONT

#### 2513N/CM2140

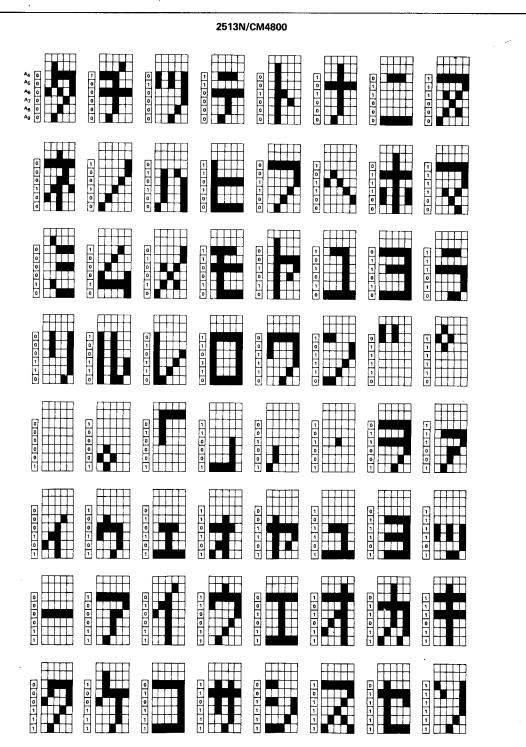

## JAPANESE KATAKANA FONT

| COMPANY         |                  |          |

|-----------------|------------------|----------|

| ADDRESS         |                  |          |

| CITY            | STATE            | ZIP_     |

| TELEPHONE       |                  |          |

| AUTHORIZED SIGN | ATURE            |          |

| DATE            |                  |          |

| CUSTOMER PRINT  | OR ID NO         |          |

| PURCHASE ORDER  | NUMBER           |          |

| DEVICE TYPE     | 2513             |          |

| CUSTOM PATTERN  | NUMBER (TO BE EN | TERED BY |

| SIGNETICS)      |                  |          |

## ORGANIZATION AS CHARACTER GENERATOR

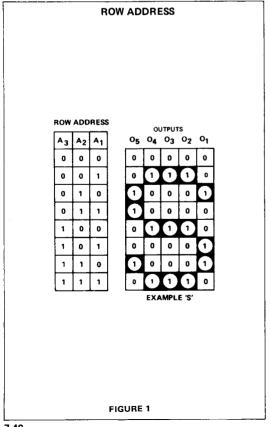

A six-bit binary address (A4 through A9) selects 1-of-64 matrix characters arranged 5 dots horizontally and 8 dots vertically. A three bit binary address code (A1 through A3) selects 1 of 8 rows. Five outputs display a complete row of the character matrix. See Figure 1. The devices may also be used in pairs to provide 9 X 7 and 10 X 8 vertical scan formats.

## CHARACTER FORMAT

# CHARACTER ADDRESS

# **COLUMN ADDRESS** ASCII CHARACTER

FIGURE 2

## ORGANIZATION AS READ-ONLY MEMORY

For a straight 512 X 5 read-only memory, the five outputs will display any one of 512 5-bit stored words corresponding to a 9-bit address applied to A<sub>1</sub> through A<sub>9</sub>.

## **CUSTOM DEVICES**

For unique custom memory patterns, this form should be used to transmit coding instructions. The nomenclature for a custom device will consist of the basic product type followed by a unique CM number assigned by Signetics. For example, "2513N/CM2141".

#### PROGRAMMING WITH PUNCHED CARDS

For maximum accuracy and minimum cost and turnaround time, the truth table should be transmitted to Signetics in the form of punched cards according to the format indicated on the following pages.

PROGRAMMING WITH WRITTEN TRUTH TABLE When punched data cards cannot be supplied, the truth table may be transmitted in written form using the attached blank truth table.

## VERIFICATION

Upon receipt of either punched card or written truth table information, Signetics will prepare a computer tabulation of the instructions and return to the address indicated. If errors are detected, they should be transmitted to Signetics as quickly as possible.

#### LOGIC CONVENTION

Logic "1"s or blackened squares in the truth table will result in "high" output from the indicated output terminal (i.e. 3.2V minimum). Similarly, a "1" address input level is interpreted as 3.2V minimum.